从DPU的崛起谈谈计算体系变革(一)和(二)从技术发展趋势和数据中心面临的问题上总结了数据中心互联技术需要解决的问题:

四. DPU的技术细节

接下来我们将从系统角度分析当前DPU做的什么事情,解决了哪些问题。

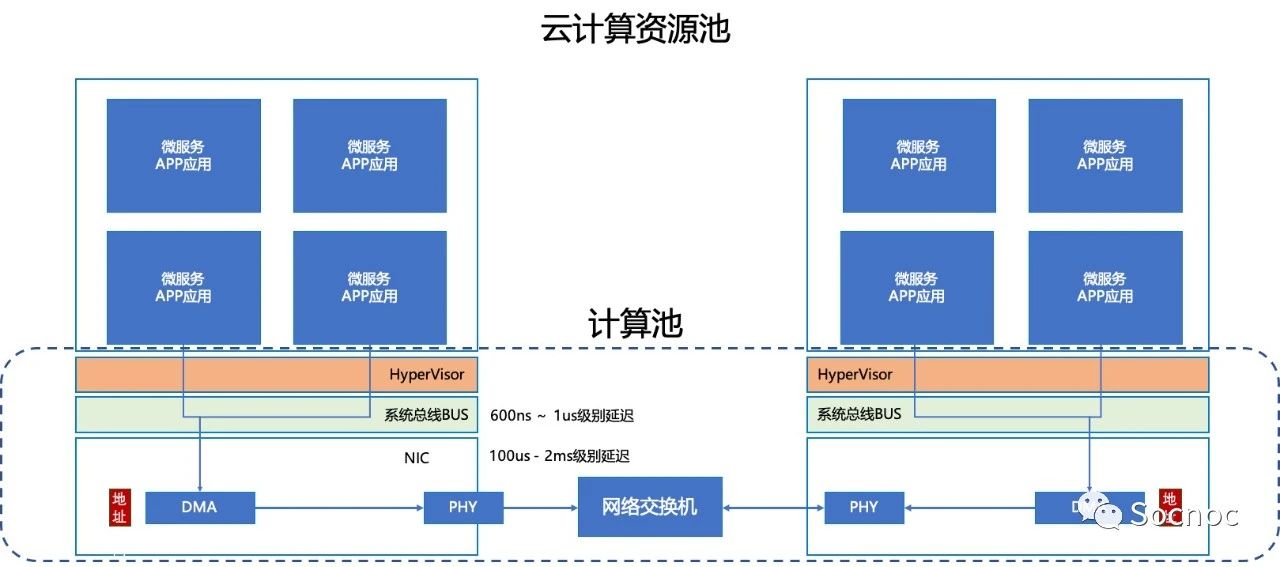

4.1 传统云计算的网络模型

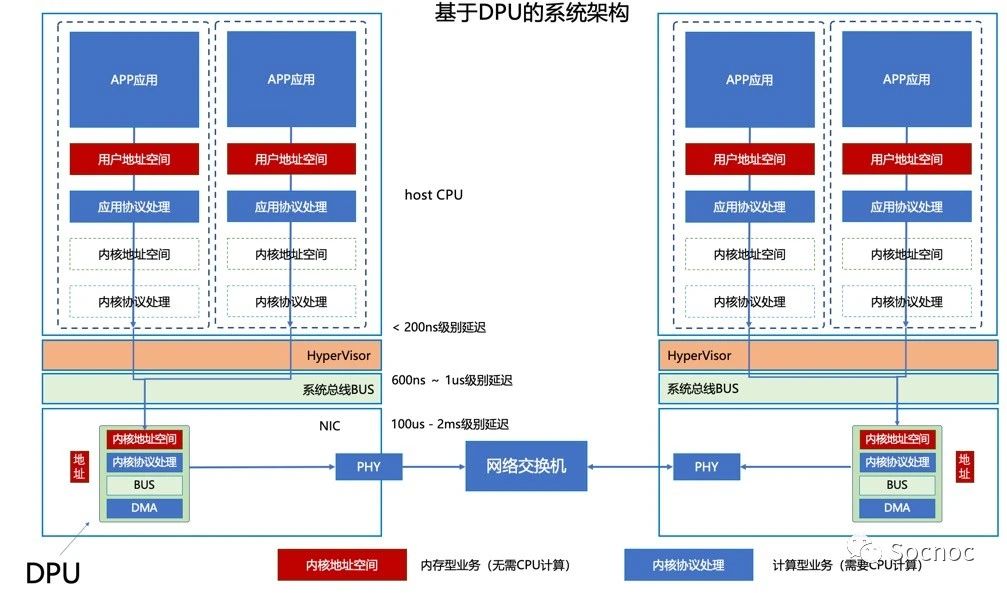

服务器互联和网络架构是一个非常复杂并且涉及到非常多的环节,为了简化问题,我只将DPU会涉及到的环节显示出来,如下图:

计算模块:主要由host CPU承担(部分由网卡上面的DMA小芯片承担)。当一个微服务(APP应用)和另外一个微服务(APP应用)通讯的时候,按照节点内(同一个host CPU上),和节点间(不同host CPU)上,数据流涉及的环节分别如下:

4.1.1 节点间数据流动:

这是传统服务器和服务器互联的应用场景,这种场景中数据主要经历用户空间、内核空间、hypervisor、总线、网卡、PHY、交换机等一些列路径。在这些路径中:

- host CPU环节:现代CPU计算非常快,延迟一般由计算量确定。如果协议复杂、延迟就高,主频高,延迟就低。由于大部分协议都在host CPU上处理,所以传统意义上提高主频可以降低延迟;

- HyperVisor路径:HyperVisor和系统OS一般深度耦合,是IaaS计算平台的核心,计算量不大,主要工作是资源调度和计算切换(context switch)。一般云计算应用场景,资源(CPU、内存等)存在一定量的超售(也就是一个CPU卖了2-4个用户,用户通过分时间使用CPU)。由于内存的速率和CPU存在一个数量级的差异,频繁的计算切换将严重影响CPU的效率,使得CPU处于等待数据读取和写入阶段。同时因为网络需要考虑状态(TCP时序等),一旦切换发生很有可能需要重新开始计算一部分数据,导致了无形中浪费了计算资源,也增加了延迟。

- 系统总线模块:这个模块开始就是纯硬件模块了,一般的软件架构师不关注这一块,一般的网络芯片架构师也不设计这一块,是被忽视的部分。我们列出来是因为我们DPU+将在这一块上做文章,同时在DPU中也得包含这个部分。技术提升比较简单,提升总线频率即可。

- 网卡模块:这个是重头戏,工作内容却非常简单,就是将网络报文转化成光电信号发出去。由于CPU需要处理大量的工作,所以增加一个DMA(一个小的MCU做简单的网络协议处理功能)协助CPU干活。基本上现在Smart NIC和DPU就是对这个模块进行升级,让一个MCU干更多复杂的事情。

- PHY、网络交换机部分:这一块就是以太网协议的设备了。

4.1.2 节点内数据流动:

这种数据模式是微服务的基本通讯方式。基本路径和节点间互联一样,唯一的区别是路由由Hypervisor(NAT或者端口,软路由)或者网卡(Bridge,硬路由)处理,即网络报文不需要额外交换机设备即可处理。这种方式是云计算的基本处理方式。

4.1.3 云计算资源池:

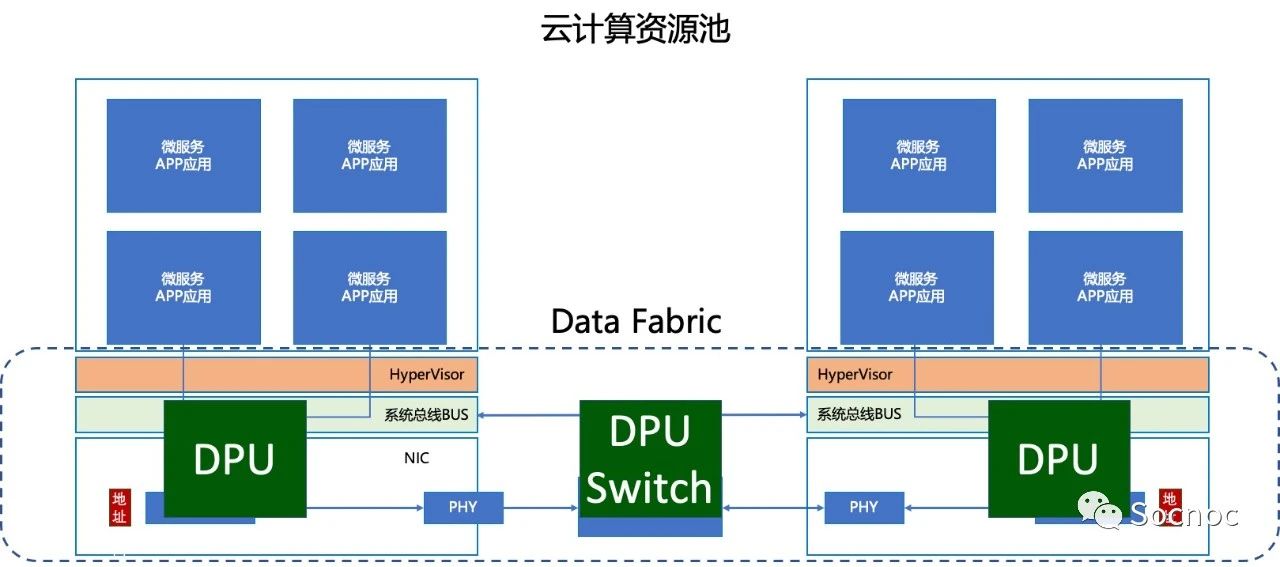

在分布式系统中(云计算、分布式数据库、分布式存储等),微服务同时存在多节点上,所以节点间、节点内通讯共存。在这种模式上,每个微服务相当于一个跨服务器间的“进程”。这种情况下,多台服务器互联成为一个“大服务器”。其中网络形成一个网络拓扑,称为Fabric。所以DPU的目标就是构建一个快速的Fabric网络,用于云计算应用。

图:网络Fabric、计算池、微服务构成云计算技术IaaS

综上可以看到当前数据中心(包括小型集群)都构建在一个网络Fabric基础上,在这个Fabric上提供统一基于TCP/IP协议的微服务架构。构成这个网络Fabric的基础就是以太网技术,而技术发展目标就是提升吞吐率和降低延迟。

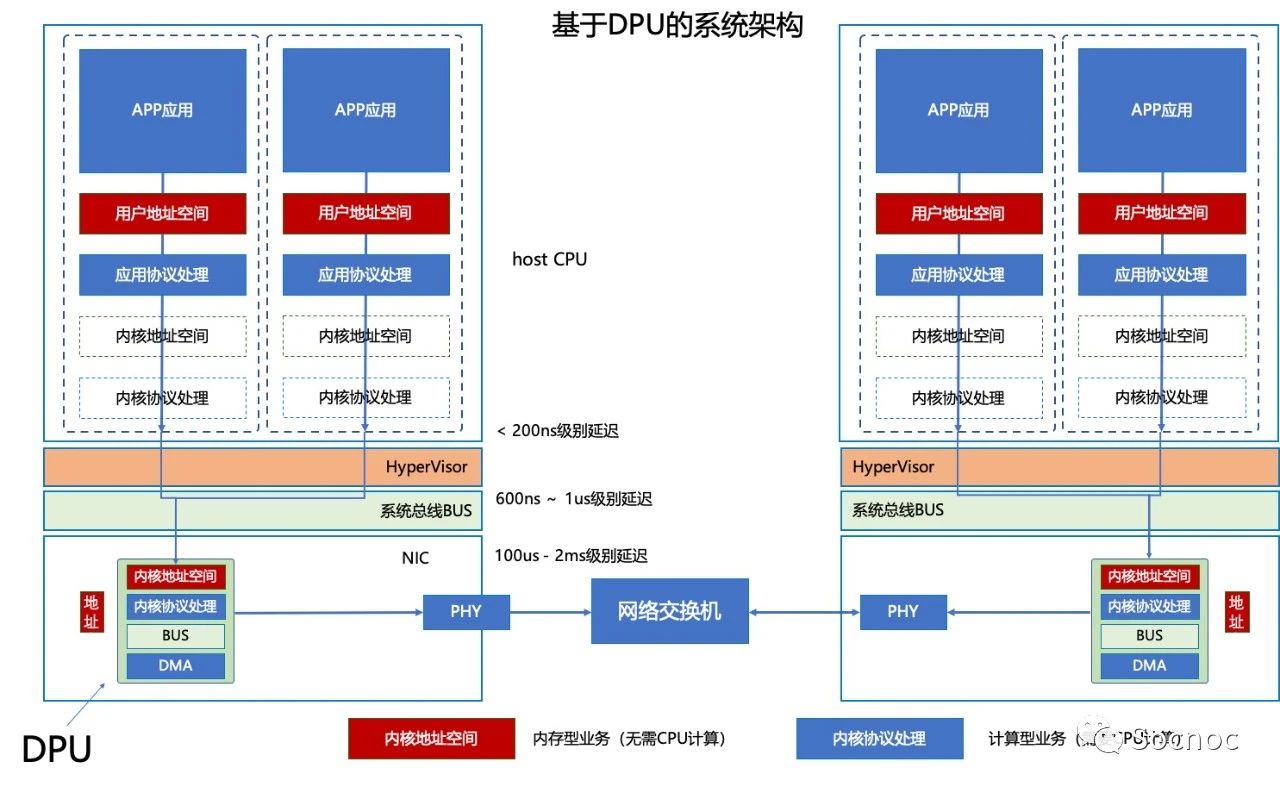

4.2 DPU构建下的云计算架构

上面已经介绍了网络Fabric是微服务和云计算发展的必然趋势。这个网络Fabric就像一张数据网,数据在中间流动。所以Fungible和Nvidia把组成这个Fabric的芯片命名为DPU,数据处理芯片。那DPU如何构建这个Fabric?如何降低网络延迟呢?

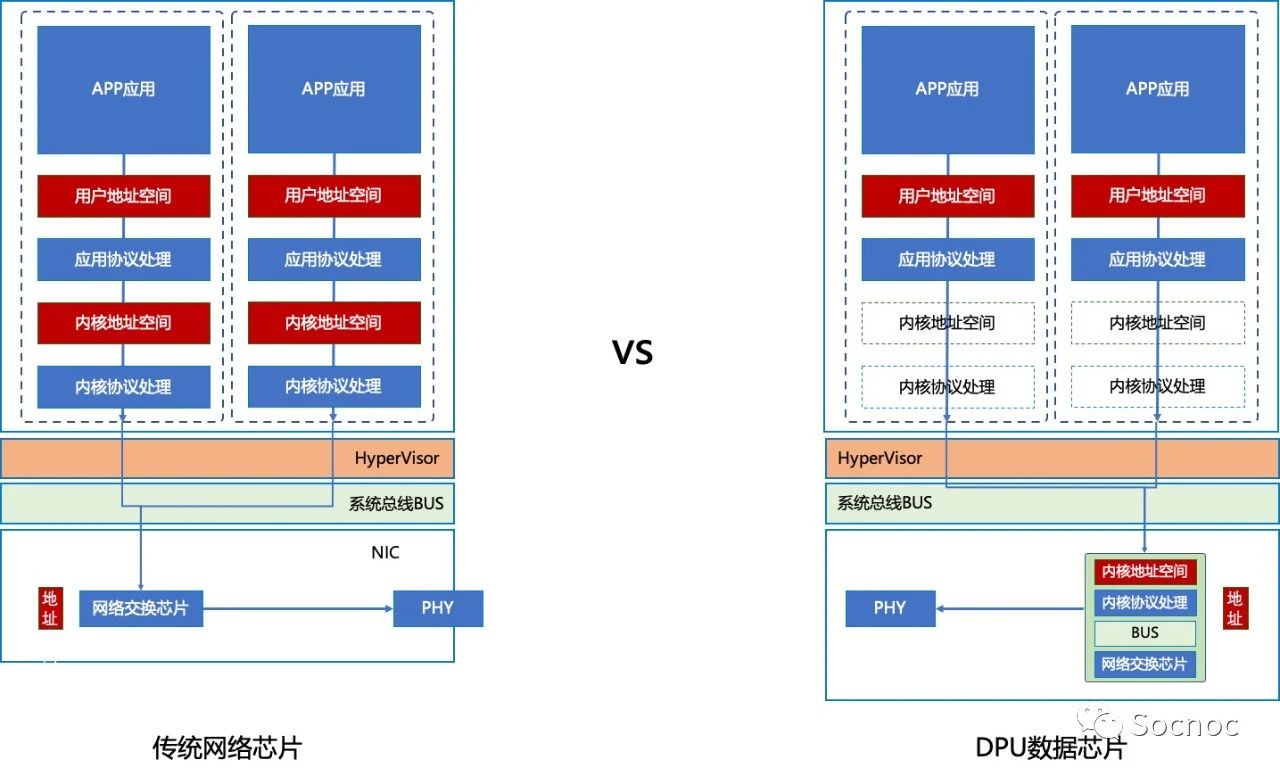

4.2.1 DPU的创新

DPU如何创新?刚刚介绍了在数据流中,内核协议处理部分和微服务应用相关性很小。所以一个想法就是将内核模块下沉到DMA上,这样就需要一个更加强大的MCU。最开始Xillinx和Intel都用FPGA来替代传统的DMA(网络芯片),达到应用加速的目的。在这种架构下,数据处理发生在host CPU之前,所以可以改善应用通讯的延迟,主要原因是:

- 网络处理发生在中断前,这个没有改进延迟,但节省了CPU的等待时间

- FPGA是独占式处理网络任务,不需要context switch,极大降低了高负载应用情况下的切换带来的延迟,极大的降低了网络抖动

- 可以把一些需要硬件加速的通用计算用FPGA加速,进一步释放CPU

通过DPU互联我们可以有效的降低网络延迟和抖动,构建一个网络Fabric。

4.2.2 当前DPU的问题:过热

由于上述创新和Nvidia的大V效应,DPU很快热了起来。现在DPU最大的问题就是“过热”,功耗太高了。以前一个网络DMA芯片功耗才5瓦左右,现在一个DPU动则100瓦以上(Fungible F1 120瓦)。大部分应用场景无法用承受这么大功耗的网络设备。尤其是在100/200G以上,光模块功耗已经超过网络设备的情况下,再增加一个100瓦的网络DPU,会极大的提升网络的能源消耗。所以必须解决DPU功耗问题。

4.2.3 当前DPU的问题:架构臃肿

另外一个问题和架构有关,如果仔细看看DPU的架构不难发现,基本上DPU包括三个模块:1)网络模块,2)计算模块,3)总线模块。其中计算模块可以理解为以前网络DMA芯片的升级版本,从一个简单的ASIC升级成了一个强大的CPU或者网络处理器;网络模块是NIC的核心部件,接口为100/200G,同时提供网络交换功能,本质是一个小型的网络交换芯片;而总线模块是因为需要互联host CPU进行协议转换,也需要互联DPU内置CPU,一般采取PCIe 4.0/5.0为主。

如果不是Fungible把F1叫做DPU用于智能网络,我觉得把这颗芯片当作一个路由器或者防火墙芯片也是绰绰有余的。考虑到Fungible具备强大的路由器、防火墙背景,这就不难理解了。我感觉Fungible的技术路线就是将防火墙芯片变成小放在网卡设备上,给每一台服务器提供一个防火墙芯片。但120瓦的功耗的确有点高。个人觉得这条技术路线不是DPU应该做的事情。

Nvidia很快就发现了这个问题,他们觉得如果用DPU处理CPU的任务是不可能的。DPU的CPU只应该做路径初始化和异常处理,有点类似L2/L3层交换机的意思。所以Nvidia的DPU就只放了几颗arm cpu,增加可编程能力而已。功耗也明显降低了下来。

4.2.4 当前DPU的问题:成本太高

和功耗一样现在的DPU成本太高了,基于DPU的解决方案变没有降低网络互联的成本。

4.2.5 当前DPU的问题:应用场景

目前DPU都是面向数据中心的应用场景。但服务器增长空间更多在边缘计算中心,而且未来边缘计算互联将成为网络技术趋势,所以DPU必须考虑边缘计算场景。

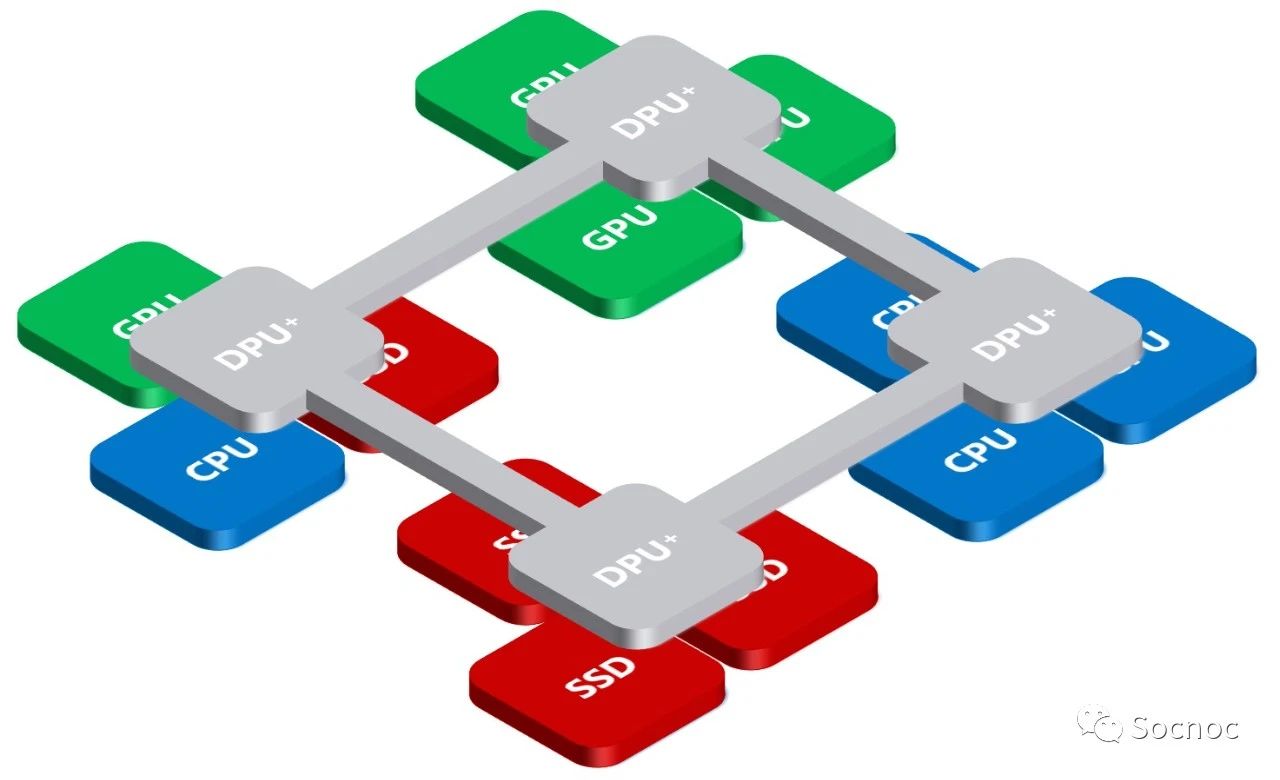

下一代数据中心(集群)将以Data Fabric作为支撑,而DPU是这个新Fabric的核心。

DPU的兴起核心原因是数据的爆发超过了CPU的处理能力,专业的数据必须由专业的设备处理。在这个思路下,以太网网络两端被DPU取代,然后DPU之间形成一个新的以太网协议,构建一个基于光技术的Data Fabric。

下面我们补充详细介绍一下为什么数据芯片会催生新的计算架构。

5.1 DPU和Smart NIC

DPU区别于Smart NIC最显著的特点,DPU本身构建了一个新的网络拓扑,而不是简单的数据处理卸载计算。最开始Fungible就是因为发展了自己的TCP协议,极大的降低了以太网互联的延迟和抖动问题,从而定义了DPU芯片。

DPU和Smart NIC的区别如下:

- DPU可以构建新的协议,Smart NIC一般只是加速协议处理

- DPU可以构建总线拓扑,Smart NIC是一个设备,无法构建新的总线拓扑

- DPU可以作为中心芯片(可以直接控制SSD等设备),而Smart NIC无法直接控制SSD、GPU等

Nvidia对DPU和Smart NIC做了一个非常详细的介绍,但没有到核心架构上。DPU可以脱离host CPU存在,而Smart NIC不行。这个本质的区别就是DPU可以构建自己的总线系统,从而控制和管理其他设备,也就是一个真正意义上的中心芯片,第三颗芯片。这个也是为什么Smart NIC出来这么多年,只有Fungible可以说他们的芯片是DPU!

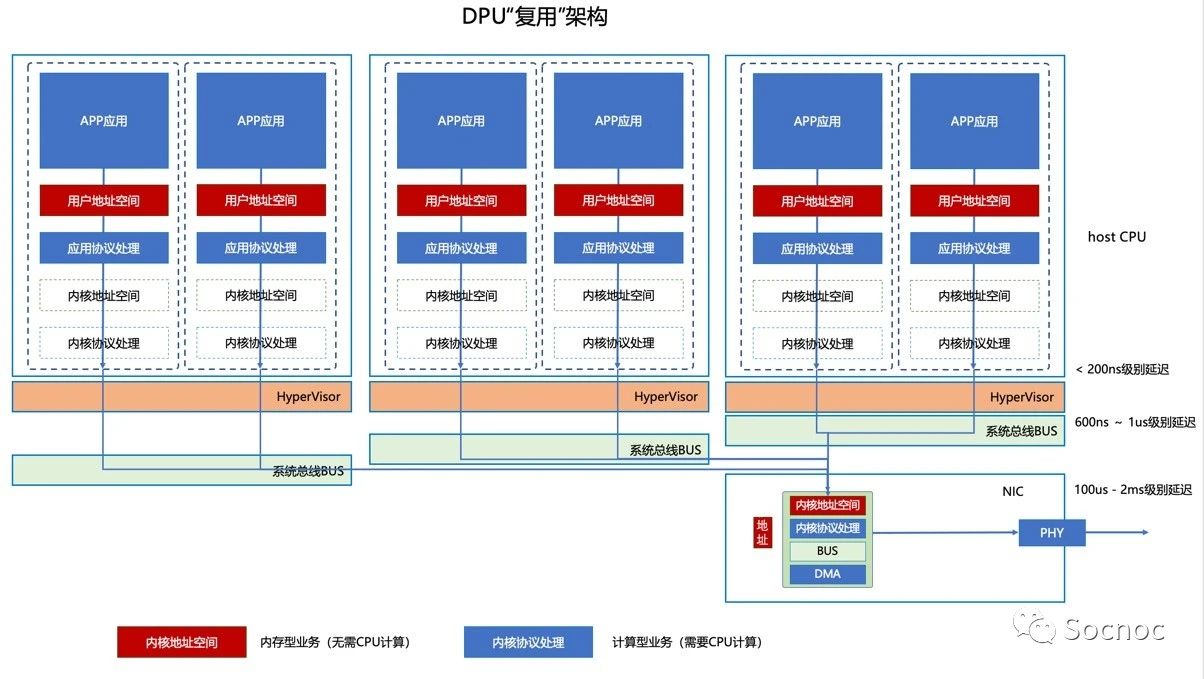

5.2 “神奇”的DPU复用

总线是一个非常珍贵的资源,可以做很多事情!Fungible的架构师明显意思到了这一点,做了非常有意思的解决方案。DPU复用!我们见过利用SR-IOV技术在一个服务器中虚拟化多个网卡VF的技术来实现多张网卡的,但很少见到一张网卡被多个服务器使用的?当然回到Fungbile DPU功耗达到120瓦的实际情况下,我们必须多“复用”这个DPU达到降低使用成本的目的。Fungible的架构师还真的就这么干了一个系统。

在DPU复用架构中,DPU实际上起到了交换ASIC作用

也就是说DPU可以互联一个小集群。目前Fungible是支持8个,Nvidia的BlueFiled应该也不会超过8个。

5.3 DPU复用开创的“芯”计算架构

DPU的复用看似是Fungible一个无奈的选择(功耗和成本太高、需要降低TCO),但却创造了一个全新的计算架构。传统的以CPU为中心的计算体系,要让位给DPU为了。未来我们将单独从架构上分析为什么这个趋势是不可避免的。

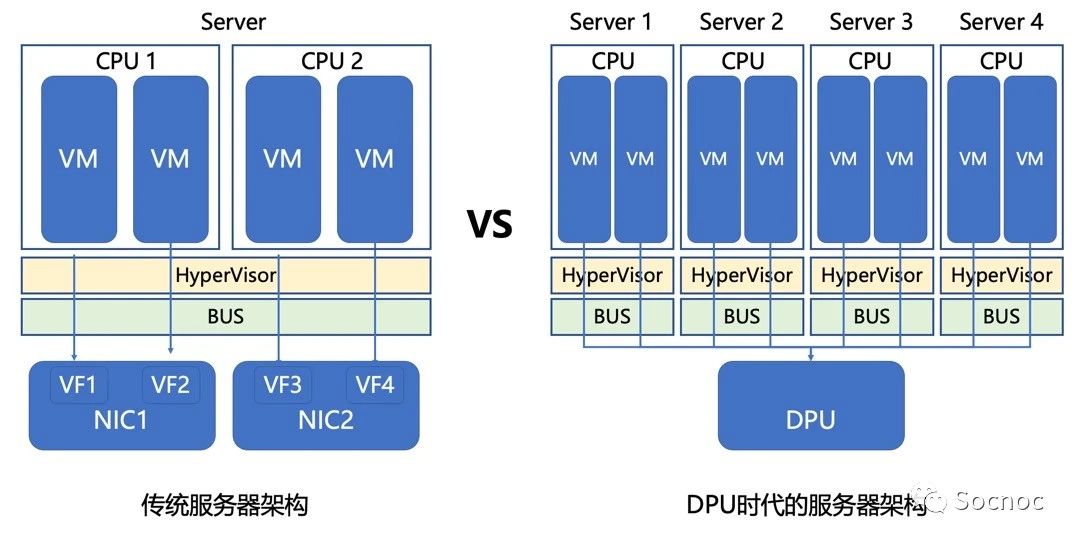

传统服务器架构中,服务器设计以CPU为中心,CPU通过初始化总线树,给每一个设备分配ID,然后所有设备按照总线协议进行协作。网卡通过SR-IOV技术可以通过软硬件协同的方式加速虚拟化环境中的网络性能,这种网络处理方式中,Mellonax的ConnectX性能比较突出。如果需要多路CPU,就通过CPU总线的方式扩展一路、双路、四路、甚至八路CPU加强计算能力。这种架构通用计算能力强悍,但重复计算较多(每个VM都需要处理相似的网络计算),对CPU的开销比较大,成本非常高。这个就是30% Datacenter tax的来源。

在DPU复用架构中,DPU相当于一个网络交换机,互联多个CPU服务器,形成一个计算集群。由于网络协议栈和一些公共计算由DPU提前处理完成,在这个集群中,CPU和CPU通讯减少了很多开销,达到了降低延迟的效果。或者反过来说,就是不需要强大的CPU了。这样可以极大降低8路互联集群的CPU成本,同时增强网络数据处理能力。在云计算领域具备非常明显的竞争优势。所以成为当前技术发展最热门的方向。

5.4 DPU到底是什么?

目前DPU是没有一个明确的定义的。虽然大家都强调以数据处理为主,但实际上做的都是Smart NIC的事情。同时明显Fungbile的出发是以网络架构为中心,以网络安全为手段的技术路线,本质上是一个L4(协议层)的公司在试图解决L2/L3(Fabric和路由)的问题,而Nvidia是以设备为中心,以GPU数据加速为手段,本质上是一个L1(设备层)的公司在解决L2/L3(Fabric和路由)的问题,两个公司的技术背景和技术路线也存在明显的差别。其他公司就只能算是一个Smart NIC公司了,打着DPU的旗号干加速的事情。

5.5 DPU的未来

虽然Fungible和Nvidia都意识到了DPU的重要性,时间上具备领先优势,也做出了新架构的解决方案。但Intel发布的IPU进一步强调了在基础架构上数据芯片的重要性,干脆把IaaS模块全部下沉到了DPU上,将这个DPU重新命名为IPU。虽然Intel目前还没有明确表明自己IPU的架构,但可以预见Intel将整合网络、软件平台、总线技术的技术力量。

虽然目前DPU/IPU的定义没有标准,但数据芯片作为未来计算架构的支撑已经成为必然趋势。

本文来源:https://mp.weixin.qq.com/s/npSGdrGScH3EW2qU0u1AOw

https://mp.weixin.qq.com/s/loOTdaamUIziJRNH1v3lRg作者:LEO

推荐阅读

更多Arm服务器及计算相关内容请关注Arm服务器专栏。