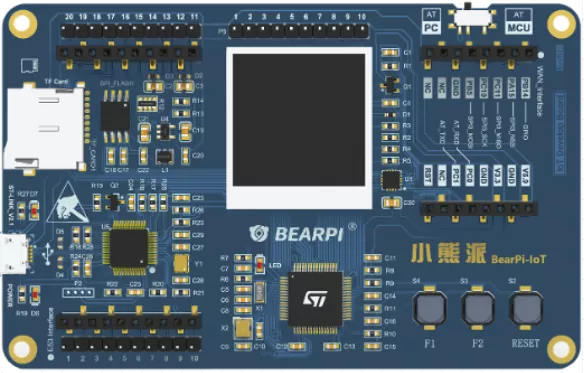

本文介绍了如何在 RT-Thread Studio 上使用 RT-Thread Nano,并基于BearPI-IOT STM32L431RCT6的基础工程进行讲解如何使用PIN设备接口及相关软件包使用。

BearPI-IOT board

为什么需要设备接口

- RT-Thread 分为标准版本和 Nano 版本,其特点如下:

- RT-Thread 标准版:拥有设备驱动框架,软件包等组件,软件包都是基于设备驱动接口来实现。

- RT-Thread Nano:仅仅只是一个 RTOS 内核。没有任何组件。

- Nano 是无法直接使用 RT-Thread 丰富软件包功能。

- Nano 是一个面向低资源的 MCU 等芯片,不可能增加如同标准版的设备驱动框架。

- Nano 需要一套统一设备驱动 API ,屏蔽不同芯片的 HAL 层的区别。方便移植工程到不同的平台。

- Nano 需要一套设备驱动 API ,可以方便使用丰富软件包组件。

准备工作

- 使用 RT-Thread Studio 建立一个 STM32L431RCT6 的 RT-Thread Nano 基础工程。

- 基础工程创建可参考:在 RT-Thread Studio 上使用 RT-Thread Nano

PIN 设备接口

- 在 RT-Thread 标准版中,PIN设备设备提供了一套设备管理接口来访问 GPIO,用户程序可以直接使用该 API 操作 GPIO 的功能,设备管理接口如下:

- RT-Thread 丰富软件包都是基于这套 API 进行开发适配,所以 Nano 也需要一套这样子的 API。在 PIN 设备接口,可以完全沿用标准版的这套API。

适配 PIN 设备接口

- 复制 RT-Thread 完整版工程中的 pin.h 文件(路径:rt-thread\components\drivers\include\drivers\pin.h)到我们准备好的 STM32L431RCT6 的 RT-Thread Nano 基础工程中。

- 由于 RT-Thread Nano 没有驱动框架,所以我们要把 pin.h 中有关完整版的内容去掉。整理完之后的 pin.h 文件如下:

/*

* Copyright (c) 2006-2021, RT-Thread Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021-08-21 RiceChen the first version

*/

#ifndef PIN_H__

#define PIN_H__

#include <rtthread.h>

#ifdef __cplusplus

extern "C" {

#endif

#define PIN_LOW 0x00

#define PIN_HIGH 0x01

#define PIN_MODE_OUTPUT 0x00

#define PIN_MODE_INPUT 0x01

#define PIN_MODE_INPUT_PULLUP 0x02

#define PIN_MODE_INPUT_PULLDOWN 0x03

#define PIN_MODE_OUTPUT_OD 0x04

#define PIN_IRQ_MODE_RISING 0x00

#define PIN_IRQ_MODE_FALLING 0x01

#define PIN_IRQ_MODE_RISING_FALLING 0x02

#define PIN_IRQ_MODE_HIGH_LEVEL 0x03

#define PIN_IRQ_MODE_LOW_LEVEL 0x04

#define PIN_IRQ_DISABLE 0x00

#define PIN_IRQ_ENABLE 0x01

#define PIN_IRQ_PIN_NONE -1

struct rt_device_pin_mode

{

rt_uint16_t pin;

rt_uint16_t mode;

};

struct rt_device_pin_status

{

rt_uint16_t pin;

rt_uint16_t status;

};

struct rt_pin_irq_hdr

{

rt_int16_t pin;

rt_uint16_t mode;

void (*hdr)(void *args);

void *args;

};

void rt_pin_mode(rt_base_t pin, rt_base_t mode);

void rt_pin_write(rt_base_t pin, rt_base_t value);

int rt_pin_read(rt_base_t pin);

rt_err_t rt_pin_attach_irq(rt_int32_t pin, rt_uint32_t mode,

void (*hdr)(void *args), void *args);

rt_err_t rt_pin_detach_irq(rt_int32_t pin);

rt_err_t rt_pin_irq_enable(rt_base_t pin, rt_uint32_t enabled);

/* Get pin number by name,such as PA.0,P0.12 */

rt_base_t rt_pin_get(const char *name);

#ifdef __cplusplus

}

#endif

#endif - 我们需要适配如上7个 PIN 设备 API ,参考实例:

- drv\_gpio.c:

/*

* Copyright (c) 2006-2021, RT-Thread Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021-08-21 RiceChen the first version

*/

#include <board.h>

#include "pin.h"

#include "drv_gpio.h"

#ifdef RT_USING_PIN

#define PIN_NUM(port, no) (((((port) & 0xFu) << 4) | ((no) & 0xFu)))

#define PIN_PORT(pin) ((uint8_t)(((pin) >> 4) & 0xFu))

#define PIN_NO(pin) ((uint8_t)((pin) & 0xFu))

#define PIN_STPORT(pin) ((GPIO_TypeDef *)(GPIOA_BASE + (0x400u * PIN_PORT(pin))))

#define PIN_STPIN(pin) ((uint16_t)(1u << PIN_NO(pin)))

#define __STM32_PORT_MAX 8u

#define PIN_STPORT_MAX __STM32_PORT_MAX

static const struct pin_irq_map pin_irq_map[] =

{

{GPIO_PIN_0, EXTI0_IRQn},

{GPIO_PIN_1, EXTI1_IRQn},

{GPIO_PIN_2, EXTI2_IRQn},

{GPIO_PIN_3, EXTI3_IRQn},

{GPIO_PIN_4, EXTI4_IRQn},

{GPIO_PIN_5, EXTI9_5_IRQn},

{GPIO_PIN_6, EXTI9_5_IRQn},

{GPIO_PIN_7, EXTI9_5_IRQn},

{GPIO_PIN_8, EXTI9_5_IRQn},

{GPIO_PIN_9, EXTI9_5_IRQn},

{GPIO_PIN_10, EXTI15_10_IRQn},

{GPIO_PIN_11, EXTI15_10_IRQn},

{GPIO_PIN_12, EXTI15_10_IRQn},

{GPIO_PIN_13, EXTI15_10_IRQn},

{GPIO_PIN_14, EXTI15_10_IRQn},

{GPIO_PIN_15, EXTI15_10_IRQn},

};

static struct rt_pin_irq_hdr pin_irq_hdr_tab[] =

{

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

{-1, 0, RT_NULL, RT_NULL},

};

static uint32_t pin_irq_enable_mask = 0;

#define ITEM_NUM(items) sizeof(items) / sizeof(items[0])

rt_base_t stm32_pin_get(const char *name)

{

rt_base_t pin = 0;

int hw_port_num, hw_pin_num = 0;

int i, name_len;

name_len = rt_strlen(name);

if ((name_len < 4) || (name_len >= 6))

{

return -RT_EINVAL;

}

if ((name[0] != 'P') || (name[2] != '.'))

{

return -RT_EINVAL;

}

if ((name[1] >= 'A') && (name[1] <= 'Z'))

{

hw_port_num = (int)(name[1] - 'A');

}

else

{

return -RT_EINVAL;

}

for (i = 3; i < name_len; i++)

{

hw_pin_num *= 10;

hw_pin_num += name[i] - '0';

}

pin = PIN_NUM(hw_port_num, hw_pin_num);

return pin;

}

void rt_pin_write(rt_base_t pin, rt_base_t value)

{

GPIO_TypeDef *gpio_port;

uint16_t gpio_pin;

if (PIN_PORT(pin) < PIN_STPORT_MAX)

{

gpio_port = PIN_STPORT(pin);

gpio_pin = PIN_STPIN(pin);

HAL_GPIO_WritePin(gpio_port, gpio_pin, (GPIO_PinState)value);

}

}

int rt_pin_read(rt_base_t pin)

{

GPIO_TypeDef *gpio_port;

uint16_t gpio_pin;

int value = PIN_LOW;

if (PIN_PORT(pin) < PIN_STPORT_MAX)

{

gpio_port = PIN_STPORT(pin);

gpio_pin = PIN_STPIN(pin);

value = HAL_GPIO_ReadPin(gpio_port, gpio_pin);

}

return value;

}

void rt_pin_mode(rt_base_t pin, rt_base_t mode)

{

GPIO_InitTypeDef GPIO_InitStruct;

if (PIN_PORT(pin) >= PIN_STPORT_MAX)

{

return;

}

/* Configure GPIO_InitStructure */

GPIO_InitStruct.Pin = PIN_STPIN(pin);

GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;

GPIO_InitStruct.Pull = GPIO_NOPULL;

GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_HIGH;

if (mode == PIN_MODE_OUTPUT)

{

/* output setting */

GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;

GPIO_InitStruct.Pull = GPIO_NOPULL;

}

else if (mode == PIN_MODE_INPUT)

{

/* input setting: not pull. */

GPIO_InitStruct.Mode = GPIO_MODE_INPUT;

GPIO_InitStruct.Pull = GPIO_NOPULL;

}

else if (mode == PIN_MODE_INPUT_PULLUP)

{

/* input setting: pull up. */

GPIO_InitStruct.Mode = GPIO_MODE_INPUT;

GPIO_InitStruct.Pull = GPIO_PULLUP;

}

else if (mode == PIN_MODE_INPUT_PULLDOWN)

{

/* input setting: pull down. */

GPIO_InitStruct.Mode = GPIO_MODE_INPUT;

GPIO_InitStruct.Pull = GPIO_PULLDOWN;

}

else if (mode == PIN_MODE_OUTPUT_OD)

{

/* output setting: od. */

GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_OD;

GPIO_InitStruct.Pull = GPIO_NOPULL;

}

HAL_GPIO_Init(PIN_STPORT(pin), &GPIO_InitStruct);

}

rt_inline rt_int32_t bit2bitno(rt_uint32_t bit)

{

int i;

for (i = 0; i < 32; i++)

{

if ((0x01 << i) == bit)

{

return i;

}

}

return -1;

}

rt_inline const struct pin_irq_map *get_pin_irq_map(uint32_t pinbit)

{

rt_int32_t mapindex = bit2bitno(pinbit);

if (mapindex < 0 || mapindex >= ITEM_NUM(pin_irq_map))

{

return RT_NULL;

}

return &pin_irq_map[mapindex];

};

rt_err_t rt_pin_attach_irq(rt_int32_t pin, rt_uint32_t mode, void (*hdr)(void *args), void *args)

{

rt_base_t level;

rt_int32_t irqindex = -1;

if (PIN_PORT(pin) >= PIN_STPORT_MAX)

{

return -RT_ENOSYS;

}

irqindex = bit2bitno(PIN_STPIN(pin));

if (irqindex < 0 || irqindex >= ITEM_NUM(pin_irq_map))

{

return RT_ENOSYS;

}

level = rt_hw_interrupt_disable();

if (pin_irq_hdr_tab[irqindex].pin == pin &&

pin_irq_hdr_tab[irqindex].hdr == hdr &&

pin_irq_hdr_tab[irqindex].mode == mode &&

pin_irq_hdr_tab[irqindex].args == args)

{

rt_hw_interrupt_enable(level);

return RT_EOK;

}

if (pin_irq_hdr_tab[irqindex].pin != -1)

{

rt_hw_interrupt_enable(level);

return RT_EBUSY;

}

pin_irq_hdr_tab[irqindex].pin = pin;

pin_irq_hdr_tab[irqindex].hdr = hdr;

pin_irq_hdr_tab[irqindex].mode = mode;

pin_irq_hdr_tab[irqindex].args = args;

rt_hw_interrupt_enable(level);

return RT_EOK;

}

rt_err_t rt_pin_detach_irq(rt_int32_t pin)

{

rt_base_t level;

rt_int32_t irqindex = -1;

if (PIN_PORT(pin) >= PIN_STPORT_MAX)

{

return -RT_ENOSYS;

}

irqindex = bit2bitno(PIN_STPIN(pin));

if (irqindex < 0 || irqindex >= ITEM_NUM(pin_irq_map))

{

return RT_ENOSYS;

}

level = rt_hw_interrupt_disable();

if (pin_irq_hdr_tab[irqindex].pin == -1)

{

rt_hw_interrupt_enable(level);

return RT_EOK;

}

pin_irq_hdr_tab[irqindex].pin = -1;

pin_irq_hdr_tab[irqindex].hdr = RT_NULL;

pin_irq_hdr_tab[irqindex].mode = 0;

pin_irq_hdr_tab[irqindex].args = RT_NULL;

rt_hw_interrupt_enable(level);

return RT_EOK;

}

rt_err_t rt_pin_irq_enable(rt_base_t pin, rt_uint32_t enabled)

{

const struct pin_irq_map *irqmap;

rt_base_t level;

rt_int32_t irqindex = -1;

GPIO_InitTypeDef GPIO_InitStruct;

if (PIN_PORT(pin) >= PIN_STPORT_MAX)

{

return -RT_ENOSYS;

}

if (enabled == PIN_IRQ_ENABLE)

{

irqindex = bit2bitno(PIN_STPIN(pin));

if (irqindex < 0 || irqindex >= ITEM_NUM(pin_irq_map))

{

return RT_ENOSYS;

}

level = rt_hw_interrupt_disable();

if (pin_irq_hdr_tab[irqindex].pin == -1)

{

rt_hw_interrupt_enable(level);

return RT_ENOSYS;

}

irqmap = &pin_irq_map[irqindex];

/* Configure GPIO_InitStructure */

GPIO_InitStruct.Pin = PIN_STPIN(pin);

GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_HIGH;

switch (pin_irq_hdr_tab[irqindex].mode)

{

case PIN_IRQ_MODE_RISING:

GPIO_InitStruct.Pull = GPIO_PULLDOWN;

GPIO_InitStruct.Mode = GPIO_MODE_IT_RISING;

break;

case PIN_IRQ_MODE_FALLING:

GPIO_InitStruct.Pull = GPIO_PULLUP;

GPIO_InitStruct.Mode = GPIO_MODE_IT_FALLING;

break;

case PIN_IRQ_MODE_RISING_FALLING:

GPIO_InitStruct.Pull = GPIO_NOPULL;

GPIO_InitStruct.Mode = GPIO_MODE_IT_RISING_FALLING;

break;

}

HAL_GPIO_Init(PIN_STPORT(pin), &GPIO_InitStruct);

HAL_NVIC_SetPriority(irqmap->irqno, 5, 0);

HAL_NVIC_EnableIRQ(irqmap->irqno);

pin_irq_enable_mask |= irqmap->pinbit;

rt_hw_interrupt_enable(level);

}

else if (enabled == PIN_IRQ_DISABLE)

{

irqmap = get_pin_irq_map(PIN_STPIN(pin));

if (irqmap == RT_NULL)

{

return RT_ENOSYS;

}

level = rt_hw_interrupt_disable();

HAL_GPIO_DeInit(PIN_STPORT(pin), PIN_STPIN(pin));

pin_irq_enable_mask &= ~irqmap->pinbit;

if ((irqmap->pinbit >= GPIO_PIN_5) && (irqmap->pinbit <= GPIO_PIN_9))

{

if (!(pin_irq_enable_mask & (GPIO_PIN_5 | GPIO_PIN_6 | GPIO_PIN_7 | GPIO_PIN_8 | GPIO_PIN_9)))

{

HAL_NVIC_DisableIRQ(irqmap->irqno);

}

}

else if ((irqmap->pinbit >= GPIO_PIN_10) && (irqmap->pinbit <= GPIO_PIN_15))

{

if (!(pin_irq_enable_mask & (GPIO_PIN_10 | GPIO_PIN_11 | GPIO_PIN_12 | GPIO_PIN_13 | GPIO_PIN_14 | GPIO_PIN_15)))

{

HAL_NVIC_DisableIRQ(irqmap->irqno);

}

}

else

{

HAL_NVIC_DisableIRQ(irqmap->irqno);

}

rt_hw_interrupt_enable(level);

}

else

{

return -RT_ENOSYS;

}

return RT_EOK;

}

rt_inline void pin_irq_hdr(int irqno)

{

if (pin_irq_hdr_tab[irqno].hdr)

{

pin_irq_hdr_tab[irqno].hdr(pin_irq_hdr_tab[irqno].args);

}

}

void HAL_GPIO_EXTI_Callback(uint16_t GPIO_Pin)

{

pin_irq_hdr(bit2bitno(GPIO_Pin));

}

void EXTI0_IRQHandler(void)

{

rt_interrupt_enter();

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_0);

rt_interrupt_leave();

}

void EXTI1_IRQHandler(void)

{

rt_interrupt_enter();

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_1);

rt_interrupt_leave();

}

void EXTI2_IRQHandler(void)

{

rt_interrupt_enter();

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_2);

rt_interrupt_leave();

}

void EXTI3_IRQHandler(void)

{

rt_interrupt_enter();

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_3);

rt_interrupt_leave();

}

void EXTI4_IRQHandler(void)

{

rt_interrupt_enter();

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_4);

rt_interrupt_leave();

}

void EXTI9_5_IRQHandler(void)

{

rt_interrupt_enter();

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_5);

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_6);

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_7);

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_8);

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_9);

rt_interrupt_leave();

}

void EXTI15_10_IRQHandler(void)

{

rt_interrupt_enter();

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_10);

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_11);

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_12);

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_13);

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_14);

HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_15);

rt_interrupt_leave();

}

int rt_hw_pin_init(void)

{

#if defined(__HAL_RCC_GPIOA_CLK_ENABLE)

__HAL_RCC_GPIOA_CLK_ENABLE();

#endif

#if defined(__HAL_RCC_GPIOB_CLK_ENABLE)

__HAL_RCC_GPIOB_CLK_ENABLE();

#endif

#if defined(__HAL_RCC_GPIOC_CLK_ENABLE)

__HAL_RCC_GPIOC_CLK_ENABLE();

#endif

#if defined(__HAL_RCC_GPIOE_CLK_ENABLE)

__HAL_RCC_GPIOE_CLK_ENABLE();

#endif

return RT_EOK;

}

#endif /* RT_USING_PIN */ - drv_gpio.h:

/*

* Copyright (c) 2006-2021, RT-Thread Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021-08-21 RiceChen the first version

*/

#ifndef __DRV_GPIO_H__

#define __DRV_GPIO_H__

#include <drv_common.h>

#include <board.h>

#include "pin.h"

#ifdef __cplusplus

extern "C" {

#endif

#define __STM32_PORT(port) GPIO##port##_BASE

#define GET_PIN(PORTx,PIN) (rt_base_t)((16 * ( ((rt_base_t)__STM32_PORT(PORTx) - (rt_base_t)GPIOA_BASE)/(0x0400UL) )) + PIN)

struct pin_irq_map

{

rt_uint16_t pinbit;

IRQn_Type irqno;

};

#ifdef __cplusplus

}

#endif

#endif /* __DRV_GPIO_H__ */ 编写 PIN 设备使用示例

* Copyright (c) 2006-2021, RT-Thread Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021-08-21 RT-Thread first version

*/

#include <rtthread.h>

#define DBG_TAG "main"

#define DBG_LVL DBG_LOG

#include <rtdbg.h>

#include "drv_gpio.h"

#define LED0_PIN GET_PIN(C, 13)

int main(void)

{

LOG_D("Hello RT-Thread!");

rt_pin_mode(LED0_PIN, PIN_MODE_OUTPUT);

for(;;)

{

rt_pin_write(LED0_PIN, PIN_HIGH);

rt_thread_mdelay(500);

rt_pin_write(LED0_PIN, PIN_LOW);

rt_thread_mdelay(500);

}

return RT_EOK;

}

- 实例代码运行现象:板载的 LED 进行周期性闪烁。

PIN 设备相关软件包使用

- 我们使用LedBlink软件包来验证PIN设备接口。

- 首先克隆 LedBlink 软件包到 STM32L431RCT6 的 RT-Thread Nano 工程。LedBlink 软件包链接:https://github.com/aeo123/LedBlink.git

- 使用 LedBlink 软件包实例:

#include <rtthread.h>

#define DBG_TAG "main"

#define DBG_LVL DBG_LOG

#include <rtdbg.h>

#include "drv_gpio.h"

#include "ledblink.h"

#define LED0_PIN GET_PIN(C, 13)

int main(void)

{

int count = 1;

LOG_D("Hello RT-Thread!");

led_add_device(LED0_PIN);

while (count++)

{

led_on(1);

rt_thread_mdelay(500);

led_off(1);

rt_thread_mdelay(500);

}

return RT_EOK;

} - LedBlink 软件包无需任何修改便可在 RT-Thread Nano 工程中使用。

- 实例代码运行现象:板载的 LED 进行周期性闪烁。

总结

- 通过适配PIN设备接口,我们可以无缝对接到软件包的使用。

- 对于低资源的芯片使用 Nano 并且能够使用 RT-THREAD 丰富的软件,无疑是一个非常完美的做法。也没有庞大的驱动框架。

- 通过这样的方式,学习完 RT-THREAD Nano 在转移到 RT-THREAD 标准版的学习,更加简单方便。

首发:Rice 嵌入式开发技术分享

作者:RiceDIY推荐阅读

更多嵌入式技术干货请关注Rice 嵌入式开发技术分享