今年的hotchip由于疫情原因还是在线上举办,这个其实更有利于国内人员的参与,不需要跋涉重洋,电脑前看看视频就可以了。虽然是线上,不过hotchip演讲的质量还是很高的,我个人主要关注了处理器和AI加速器相关的topic,今天先简要的聊聊CPU部分。

今年的CPU topic包括4个section,Intel占2个,Alder Lake 和Xeon Sapphire Rapids,还有AMD的Zen 3,以及IBM Z系列的Telum。这几个都是高性能处理器,以性能和频率优先,因此堆料十足,尤其是IBM,作为大型机的代表,基本上可以算是CPU核心的巅峰。

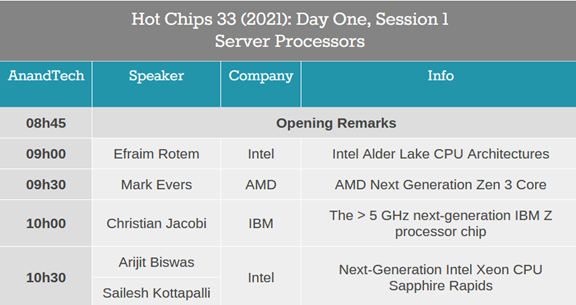

第一个是Intel的桌面级CPU Alder Lake架构,看到这张slides真有点感慨,风水轮流转,现在轮到Intel学ARM了,也搞起大小核的设计。这也不是什么新鲜技术,通过Peformance 和Efficient core的组合和动态调度,可以合理的平衡性能和功耗,尤其是功耗方面。这套系统在移动端获得了很大的成功,Intel选择这样的设计,可能还是想尝试下高性能移动端的市场。

这个scalable的配置或许能旁证上述推论,Alder Lake架构设想通过不同大小核的组合,形成一个架构类似的处理器系列,覆盖从Mobile到Desktop的全产品线。为了更好地实现这一点,还引入了Building Block的概念,把主要核心和外设模块像积木一样搭起来,相当于后端的modularize。

为了更好的调度大小核,Alder lake引了一个Thread Director。演讲中花了很大篇幅来讲这个调度的规则,大体上是硬件提供一些运行中数据,然后由专门的软件据此计算出核心负载和程序需求,在用特定算法进行调度。其中还专门强调了P core上执行的不一定是性能高的,E core上也不一定是性能低的。这个和通常的理解有点不同,应该是根据power budget进行计算的结果,可以选择让E core跑在更高的频率上以及使用加速硬件单元来获取高性能。

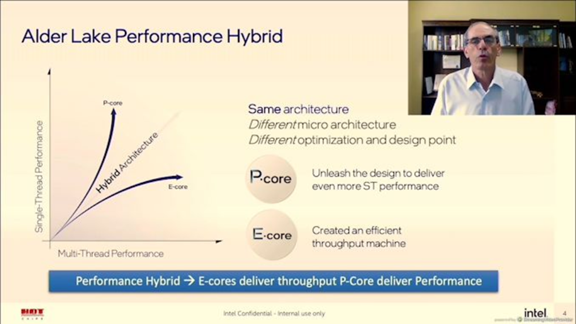

另一个值得注意的点是Alder Lake引入了New Matrix engine, 和之前的Vector engine一起可以提供从向量到矩阵的各层级加速。这一点是Intel想要用CPU来进行AI加速的设计策略,相比一些fix function加速器可以提供灵活的多的可编程性。这个scalar+vector+Matrix的组合也是很多大型AI芯片的选择,比如华为的达芬奇,国内streaming computing的NeuralScale。Intel相比这些公司最大的优势是X86完善的生态和良好的编程性,很容易适配AI日新月异的模型和应用场景。

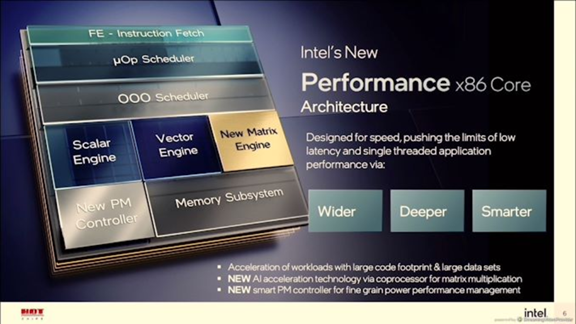

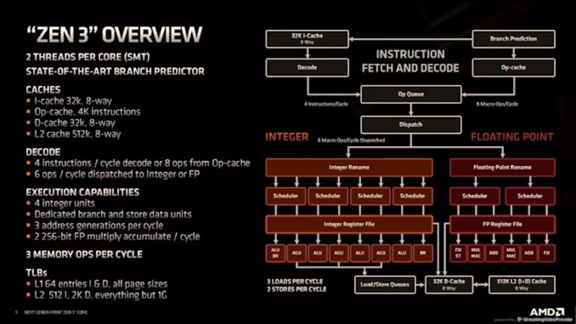

对于AMD的Zen3,我的感觉是中规中矩,稳扎稳打的节奏。相比Zen2主要是增大了一些硬件资源,提升了单线程的性能,扩大了缓存,提出了3D V-cache,可以提高15%的性能。这个是工艺上的改进,就不做评价了。另外Zen3的slides中有很多流水线的细节和配置参数,可以给处理器设计人员做一个很好的参考。总而言之,Zen是一个在架构和商业上都获得巨大成功的架构,值得反复的研究。

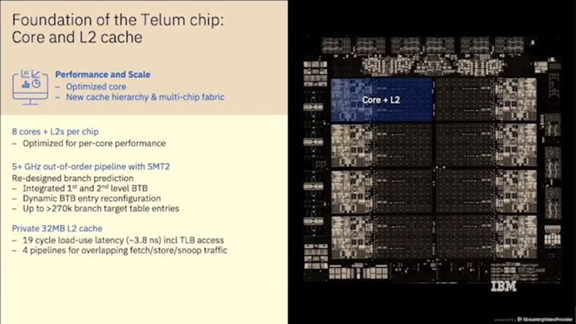

虽说X86架构占据了绝大多数的服务器市场,不过IBM还在持续推出它的大型机芯片Z系列。这种系统在一些大型企业,比如银行,金融类产业还是挺有市场的,毕竟这些行业不差钱,稳定性和高并发性才是最重要的。从这一代Z架构,也就是Telum可以看出来,资源上很是大方,毕竟Performance是最主要的考虑因素。

Telum chip是530 sq mm的庞然大物(Samsung 7nm),这么大的面积上只有8个核心,可见单个核心的面积有多夸张。另外,每个核心4MB L2,这个size只能说是oh my god。虽说是4MB的L2,不过这个size不是独享的,IBM引入了一个virtual cache的概念,即每个核心上的RAM资源通过ring bus进行连接,可以动态配置成L3或者L4 cache,这样可以根据程序特点来对cache资源进行配置,达到最优的存储局部性。并且这些RAM不但可以在一个chip内互联,还可以跨chip间互联。比如一个4-drawer的system就可以组成高达8GB的L4 cache。这个设计还是非常独特的。

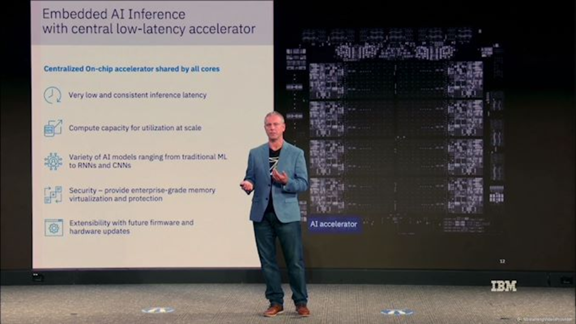

另外Telum也引入了AI accelerator,由8个核心共享,可以提供6TFLOPs的计算能力。这个数字不算很大,毕竟Telum不是专门针对AI的CPU。不过也从侧面表明了AI加速已经成为处理器设计中不可忽视的一部分。同时IBM也设计了相关的AI指令,是memory-to-memory的CISC指令,这个设计规则和TPU类似,包含convolution,matrix multiply, pooling,activation等function,应该是挺传统的一种fix function的加速方案。

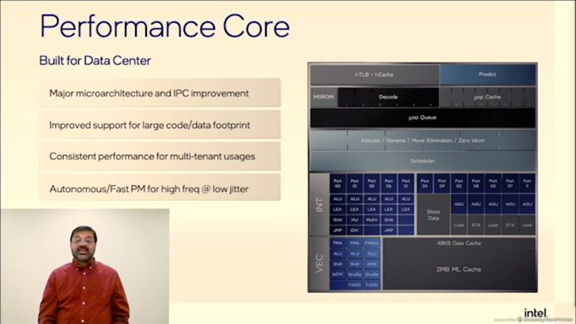

最后是Intel的Xeon处理器系列Sapphire Rapids,这是服务器级别的CPU架构。对比Zen3来看,新一代Xeon在核心的参数上要高一些。毕竟这几年被AMD蚕食掉不少市场,不能再慢慢挤了。从标题中就能看出,在AI和Memory/IO上有比较大的改进。

上图是其流水线示意图,和Zen3相同,单cycle可以译码6条指令。执行级,整数单元包括5个ALU,其中有2个jump,另外存储单元包含5个AGU,3个给load,2个给store。对比Zen3的4个ALU和1个jump,性能要强一些;在LSU上,Zen3是shared的3条AGU,而Intel看起来是独享的,理论上可以同时执行3条load和2条store指令。另外intel配置了48K的L1 Dcache,而Zen3的size是32KB。这些资源山的提升使的新一代Xeon在单核性能上会略高于Zen3.

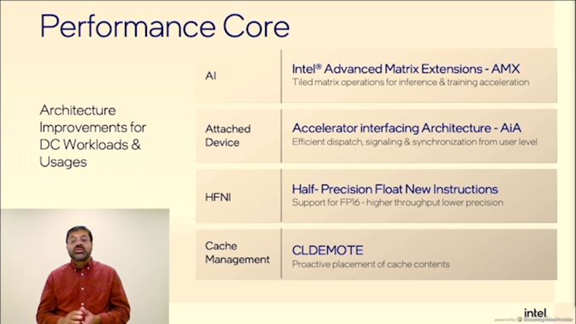

另一个就是对AI的加速,使用了AMX extension;为此设计了专门的AiA接口,user level就可以dispatch;支持半精度的指令以及cache management。推测之前Alder Lake的Matrix 加速应该也是AMX。除此之外,后边还介绍了其他几个acceleration engines,包括Data streming用来搬数据;Quick assist,加速crypto和compression的;以及Dynamic load balancer做CPU负载调度。这些专用加速模块出现在Xeon架构中,说明DSA的理念已经深入到传统处理器设计中,这也是提高CPU系统综合性能的有效方法。

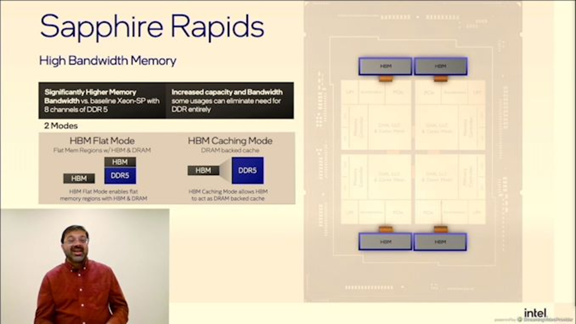

另外intel还设计了HBM的dual mode config,除了传统的HBM memory layout外,还可以把HBM当last level cache使用。Intel的这个技术搞的还挺神秘,在后边的question中有人问tag怎么处理,表示为机密不能透露。猜测应该是需要专门的硬件来做tag array,并且以HBM的block size做为cache line size。

从演讲的4款处理器可以大致看出当前高性能CPU设计的一些趋势。制造方面,chiplet和高速核间互联成为流行方案;核心设计上,还是采用更宽的发射宽度和更多的执行单元个数,不过这样的提升已经比较接近ILP的极限;系统上,通过DSA设计提供对专用领域的加速,获得整体上的性能提升,尤其在AI方面,针对特定算子和算法的加速已经成为CPU设计不可或缺的一部分。

具体的slides可以关注anandtech的live blog

https://www.anandtech.com/Sea...