今天在出差的路上,时间有限,只能简单写一点分享。

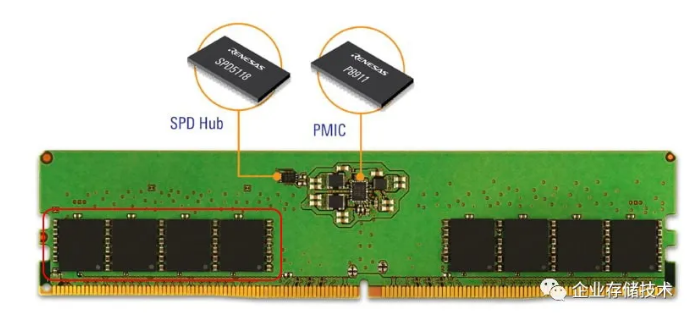

这两天看到业内专家、UEFI社区博主老狼写了一篇《DDR5来了,它长什么样?外观上有哪些特征?是不是该上船了?》,又顺着文末的参考资料跟着学习了一些。但我想写的其实是很简单的一点,其实估计同行朋友也不难发现。先看看下面两张图:

非ECC DDR5每个子通道4颗芯片

用于客户端(台式机)的Non-ECC DDR5内存,DRAM芯片数量如同现在的DDR4一样是8个x8 bit位宽的颗粒,虽然分成了2个32bit的子通道。

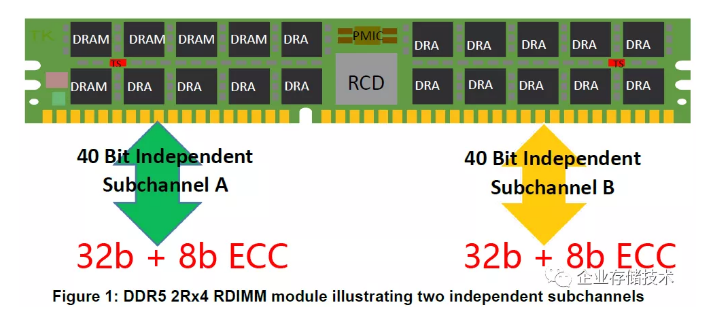

ECC DDR5每个子通道5颗芯片

用于服务器(也包括一些工作站)的ECC内存,则是每个子通道都要加一颗DDR5 DRAM芯片,数据位和校验位4+1的比例。

举个例子,以前DDR4 ECC内存是由非ECC的8个颗粒增加到9个,现在就要从8个增加到10个。相当于DDR5要多出1/9的存储芯片,整条内存的成本就提高了吧。

Non-ECC DDR5内存,是2个32Bit的子通道;而ECC DDR5就需要2个40Bit Subchannel A和B(以前DDR4 ECC一共是72Bit),因为每个故障域内都要能做到芯片级的容错。

当然也有达不到芯片级容错的ECC,比如我在《暗藏Win7支持?NVIDIA RTX A4000专业显卡另类测试》里面提到的GPU显存ECC开关,就是8颗芯片只有1/16的校验位(16GB显存打开ECC后可用为15GB)。

至于DDR5引入了On-die ECC,这个只是用于芯片内部的校验,应该是为了保证高频信号的完整性。服务器ECC内存不但仍要加芯片,而且还比以前加得更多。

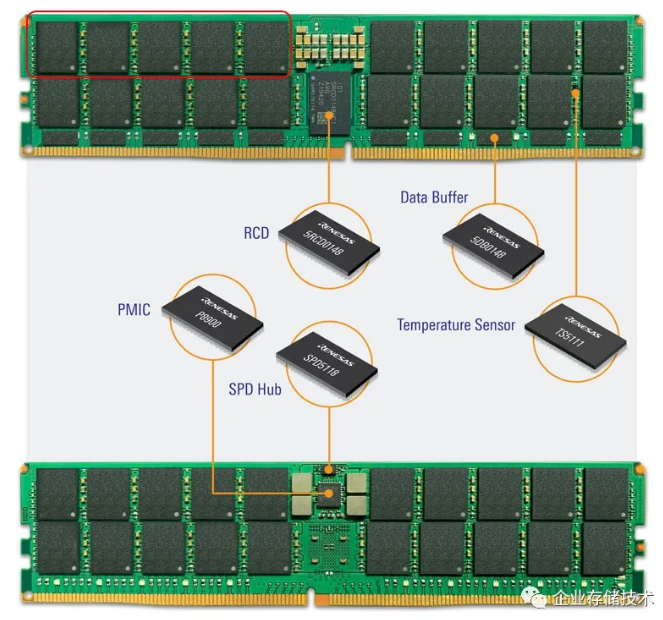

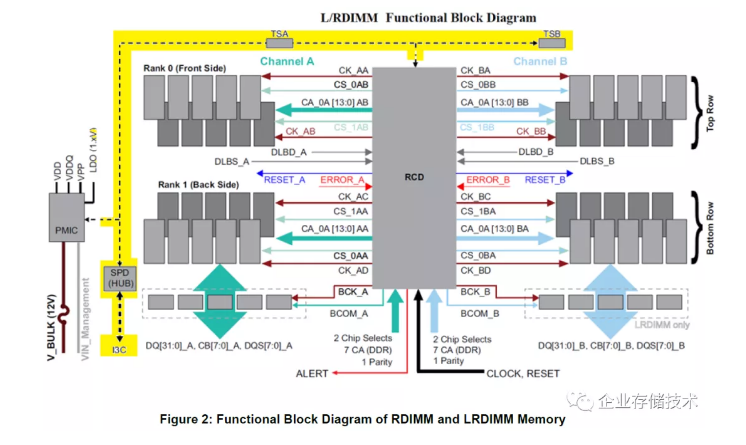

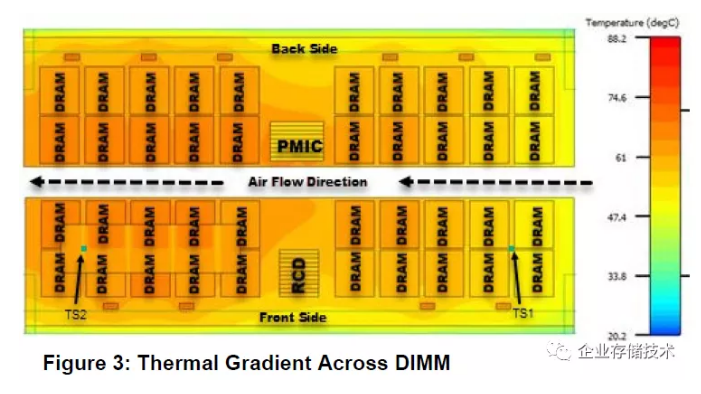

最后再引用《Micron DDR5: Key Module Features》里面的2张图,供大家参考。

作者:企业存储技术

原文:https://mp.weixin.qq.com/s/-mw452lObKKrick5D3VWYA

推荐阅读

欢迎关注企业存储技术极术专栏