复盘:集成平台促器件综合、扩张边界破产品局限

复盘海外特种集成电流市场重视国家大规模投入技术外溢效应

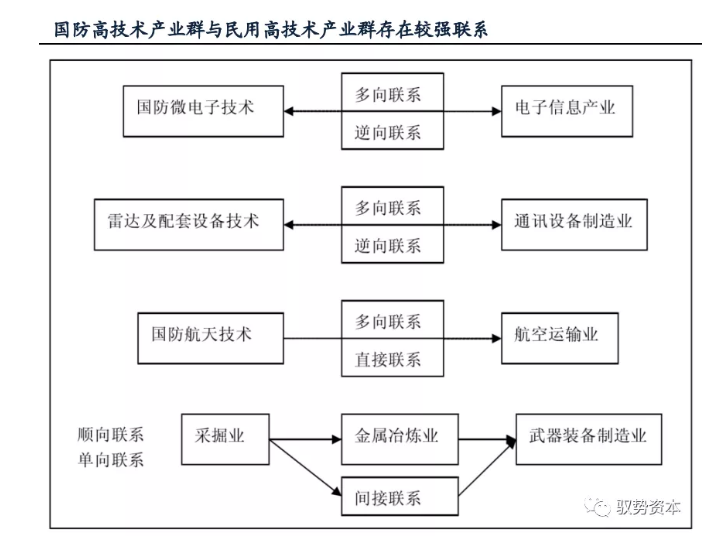

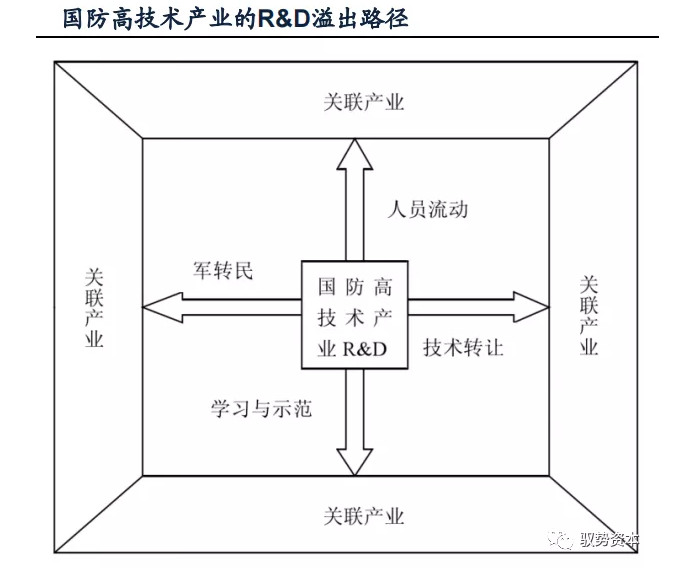

国防高技术是以军事需要为牵引而发展的当代尖端技术,许多高科技多首先在国防领域应用。据《国防高技术产业R&D溢出效应》(胡茂盛,2011年3月,南京航空航天大学),许多高科技往往首先在国防领域应用,由此产生了国防高技术群,如国防微电子、国防光电技术、国防计算机技术、国防精确制导技术、国防新材料技术、国防航天技术等,并通过国防高技术转换为民用,形成新的产业群,并在此基础上带动各行各业技术水平的提高,从而提高整个国民经济效益。据测算,国防高技术转民用后,经营得好的企业,其高技术产品获得的利润,可以达到总销售额的30%以上(即国防转民用后经营好的企业净利润率可在30%以上)。

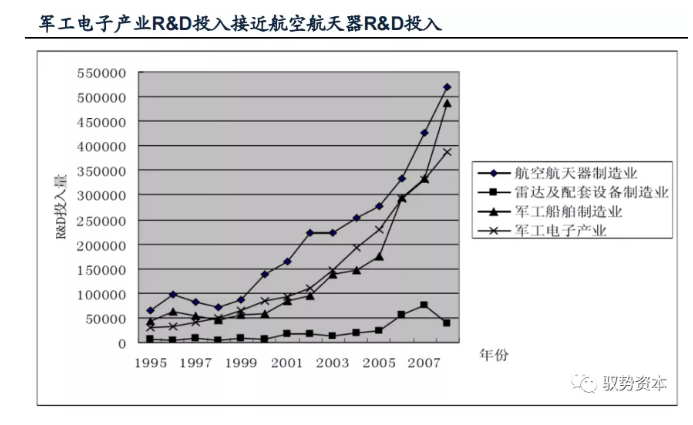

国防高技术产业具有丰富的科技资源、人力资源、产业资源,国防高科技产业的R&D投入对相关产业以及区域经济发展具有很强的溢出效应。据《国防高技术产业R&D溢出效应》(胡茂盛,2011年3月,南京航空航天大学),该文以1995-2008年间国防高技术产业各部门的R&D投入以及民用相关部门的工业增加值等数据为样本,探寻国防R&D投入对产业影响几何、国防高技术产业的R&D溢出能在多大程度上促进相关产业的发展、相关产业能否真正从中受益?该文采用灰色关联度的方法分析了国防高技术产业与相关部门之间的关联度,并用回归分析方法,对国防高技术产业的R&D溢出效应进行了衡量,得出结论认为军工电子对电子通讯设备制造业存在较大的溢出效应。

复盘海外,美国政府对国家安全应用的微电子技术需求与强大的资金支持,与其半导体工业紧密相关。据《Trusted Microelectronics:A Critical Defense Need Dave Chesebrough》(李应选译,中国航天电子技术研究院科技委),从雷达和数据处理开始,微电子技术支撑了战略司令部到现场通信、运输、武器系统和平台的所有军事和国家安全系统。

实际上,美国半导体工业的发展在一定程度上源于美国政府对研发的资助,然而近些年商业应用的大规模拓展和大批量生产使得政府对微电子器件的需求被边缘化。例如,据《半导体产业优势国家和地区资金支持的经验与启示》(张晓兰,黄伟熔,国家信息中心经济预测部,2020年第8期),美国采用国防采购资金支持产业发展,而集成电路产品与军事领域关系密切,依托军备采购的大量需求美国半导体产品军用市场空间巨大,而在半导体产业发展初期,美国厂商与军队合作研发,产品主要以军用领域为主。

如1959年美国导弹发射系统首次应用集成电路、1961年Ti公司与美国空军共同研制出首台集成电路组装计算机,军队注入大量资金为美国半导体产业发展提供了强大支持,直接推动产业扩张和技术进步,为美国集成电路产业优势的形成奠定了坚实基础。据该文,20世纪60年代,美国80%~90%的集成电路产品由国防部购买,直至90年代末美国半导体市场才逐渐转向为民用领域。

Xilinx介绍:全球FPGA行业破局者、领先者、增长型IC企业

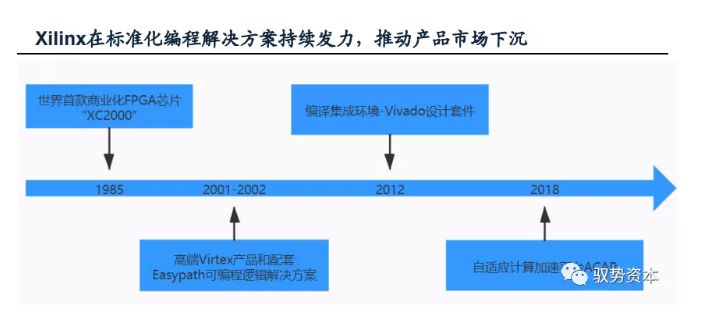

产品标准化创新的先驱者,公司发展的重点产品和软件推出引领行业发展方向。

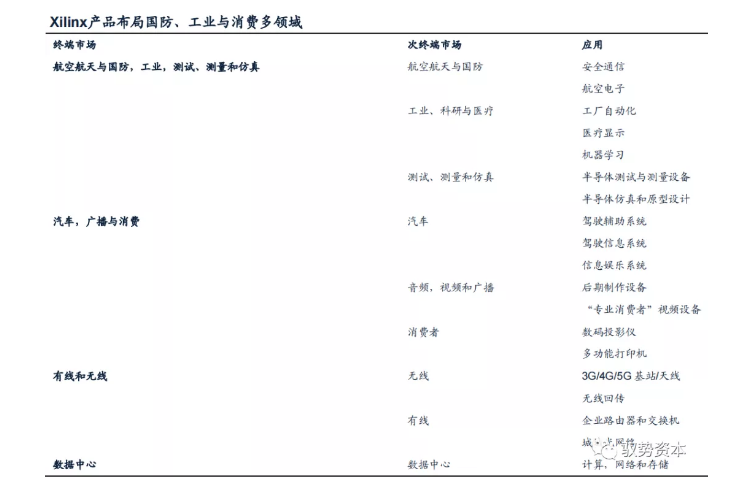

Xilinx(赛灵思,XLNX)成立于1984年,是一家提供半定制可编程逻辑器件解决方案的平台。Xilinx主要经营FPGA、SoC、ACAP等器件以及配套的开发工具、IP核、设计服务和培训服务,市占率超过50%,目前处于全球相关行业的龙头位置。Xilinx的产品主要应用于国防工业、5G、汽车电子、数据中心等领域。Xilinx属于Fabless经营模式,本身只负责器件的设计、开发和销售,而将器件的生产外包给专业的半导体制造公司如UMC、IBM和Seiko Epson。

从产品属性看,FPGA半定制化的可编辑性和灵活性成为其绑定高端通信客户的先天优势,但定制化的价格和成本高敏感性反过来成为FPGA应用领域下沉的关键阻碍。Xilinx从1985年开始在产品标准化领域持续发力,通过提供泛用性的编程解决方案向下游其他市场突围。1985年,Xilinx推出世界首款商业化FPGA芯片“XC2000”,通过自创门阵列通用结构推动产品标准化开端,随后公司推出Virtex芯片和配套Easypath编程逻辑解决方案进一步降低用户学习成本,提升产品泛用性。2018年,公司推出具有功能突破性的ACAP平台实现对AI和机器学习领域的市场渗透。

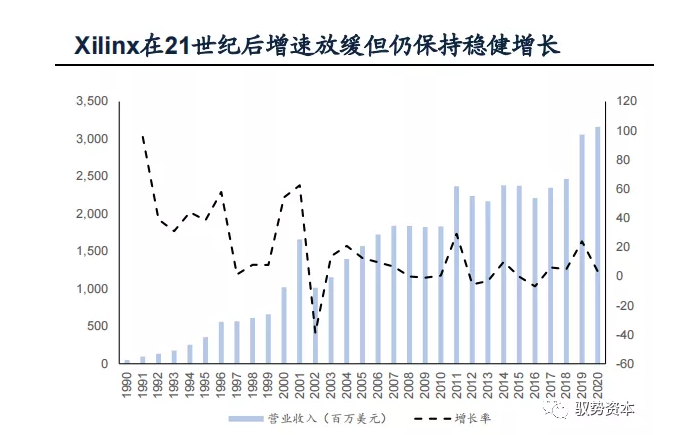

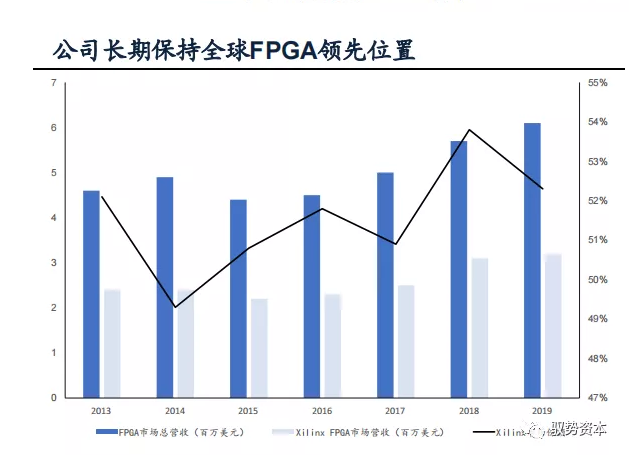

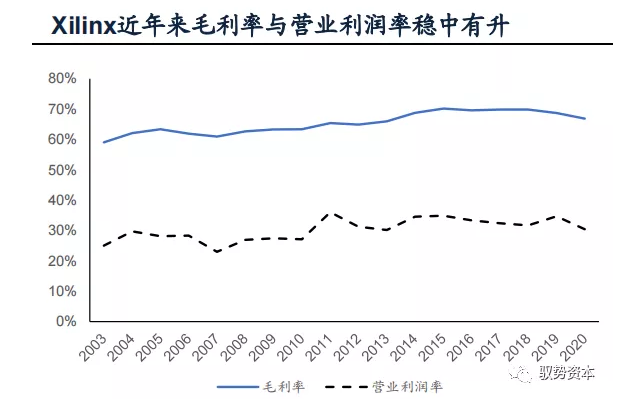

FPGA市场绝对龙头,主业聚焦增长稳健。放眼长期视角,Xilinx营业收入规模在上世纪末保持强劲增长势头,进入21世纪后增速放缓但仍保持稳健增速,且在FPGA产品领域市场份额稳定保持50%水平且震荡上升。Xilinx2020财年营收31.63亿美元,同比增长3.39%;2019财年营收32.59亿美元,同比增长24%,该财年营收增速较大或与新产品ACAP的推出和软件平台Vitis的开源免费带来的客户引流有关。

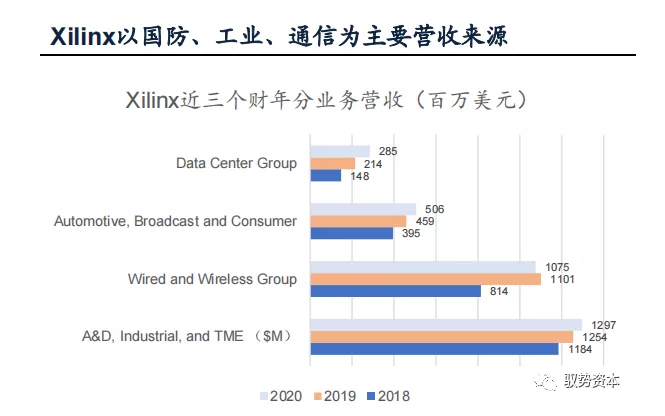

从营收构成来看,国防工业和5G领域业务是主要组成部分,营收占比之和超过80%,主营业务集中度高。国防、工业、TME(测试、测量&仿真)业务为公司长期以来的绝对主营业务,营收占比接近50%且增速始终保持稳定,5G领域业务在亚太地区特别是在中国迅速扩张,2019财年和2020财年的营收增速分别是44.66%和32.93%。

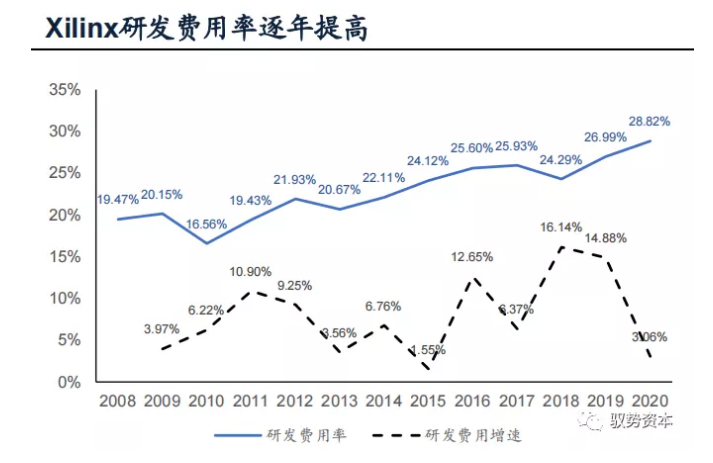

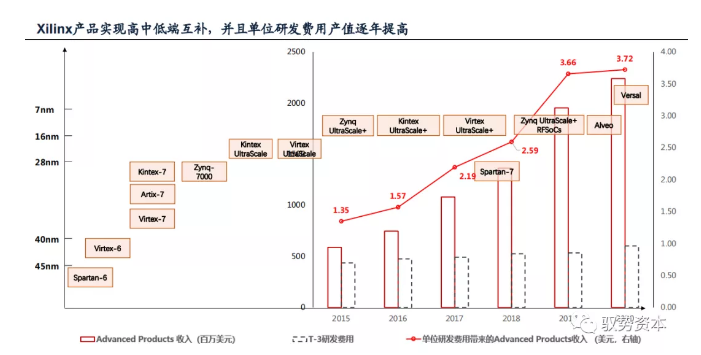

外部并购与内部研发双核驱动,技术实力铸就高技术壁垒。近年来Xilinx持续整合产业链相关公司,致力于增强技术优势,泛化拓展产品边界,如收购Solarflare为公司提供SmartNIC技术以降低网络连接低延迟,收购DeePhi以优化软件,提升FPGA在视频和图像深度学习方面的优势。Xilinx对这些公司的收购重组实现了产品细节的优势互补,致力于为客户提供更专业丰富服务、打造可编程逻辑生态平台提供捷径。研发费用持续保持正增长态势。

Xilinx近四年研发投入以12.4%年复合的增长率持续上涨,到2020年已实现每年超过8亿美元的巨额投入,超过行业第二Altera(现为Intel子公司)的每年4.18亿美元和行业第三Lattice的6.12亿美元。2018年,公司研发历时4年,斥资超过10亿美元的自适应计算加速平台ACAP问世。ACAP将软可编辑模块和硬不可编辑模块相结合,赋予用户动态调整硬件的能力,该项产品的应用领域目前还较为狭窄,但考虑其未来在AI、机器学习等领域的广阔应用前景,或为公司带来可观营收。

FPGA厂商核心壁垒:软件工具、转换成本、IP资源、产品定位

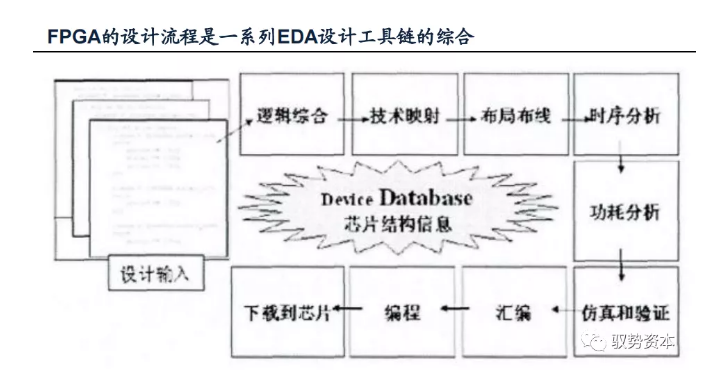

FPGA的设计流程是一系列EDA设计工具链的综合,编程语言的专用性及流程的复杂化等加大第三方企业渗透的难度。用户在FPGA设计流程中,需要使用到HDL语言、逻辑综合工具、门级网表工具、工艺映射工具、逻辑打包工具、布局工具及布线工具等一系列EDA设计工具。

从工作内容看,一般FPGA的EDA软件处理包括以下步骤,电路设计、逻辑综合、工艺映射、布局布线、仿真和编码下载等。具体看,据西安电子科技大学2010年硕士论文《基于LUT的FPGA工艺映射优化》,FPGA支持软件的设计流程,是从用户的设计输入开始,首先进行逻辑综合,将设计输入转化为网表文件并优化,而后采用约束库进行技术映射,再进行布局布线、时序分析、功耗分析、仿真烟增,最后汇编产生二进制的比特流文件下载到芯片,继而完成FPGA的开发。

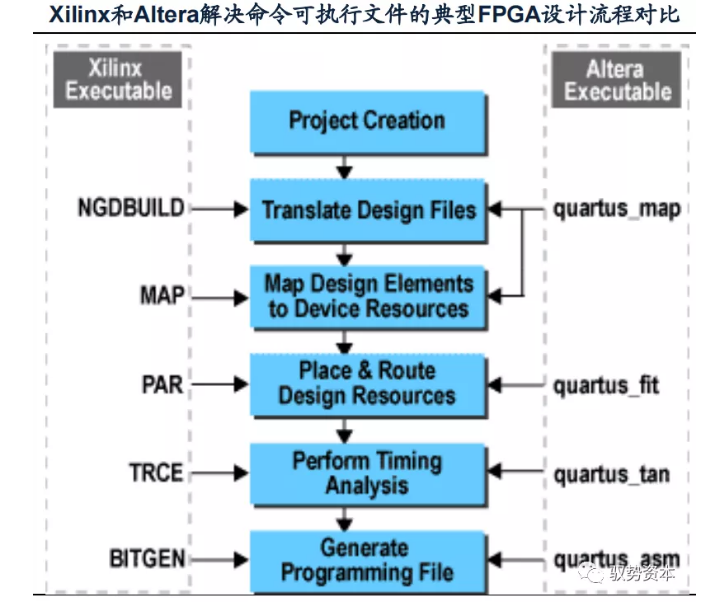

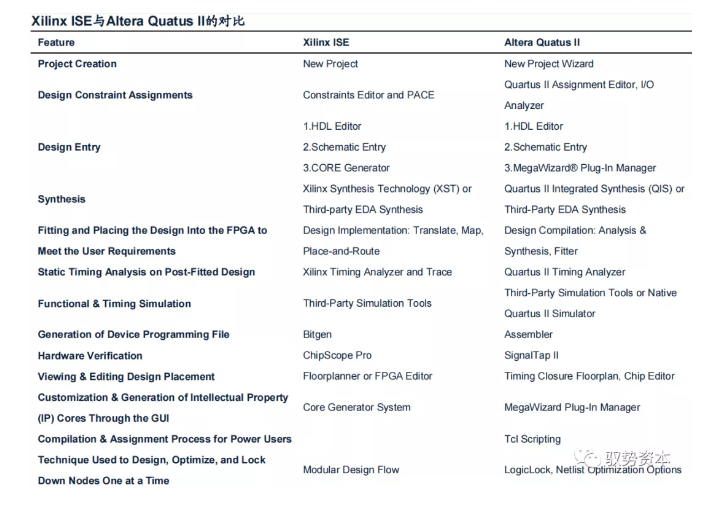

在布局布线中,因支持FPGA开发的EDA软件需要将电路描述为FPGA芯片的配置信息,因此EDA设计软件必须利用FPGA芯片的内部结构信息,而为了该信息不被泄密而增加芯片设计被破解的可能,因此除了前端的(如行为综合、逻辑综合、前仿真)可使用第三方工具外,FPGA芯片供应商一般都提供自己设计的EDA后端工具(如工艺映射工具、布局布线工具等),如在21世纪初期Altera、Xilinx分别有自己的开发工具Quartus II、ISE工具。

专用工具的复杂化与FPGA技术升级相互驱动,结构越复杂、密度越高、性能越强的FPGA往往会带动相关软件的复杂化、升级化,因此软件的供应能力与专用性形成FPGA企业的壁垒之一。制程的先进性除与公司自身的研发水平相关外,也与下游代工厂相关,同时主要厂商Xilinx与Intel在先进制程的推出时间上相差不大,因此软件带来的竞争优势相对而言会更为持久。

软件复杂化及专用化带来使用者更高的转换成本。对于芯片设计商而言,产品相对更趋于标准化。而对于下游客户而言切换使用平台的难度更多取决于其本身的产品粘性及陡峭的软件学习曲线,即使是开发新设计,对于客户而言转换FPGA供应商的成本也更高。FPGA需要独特的硬件语言编程,当制程工艺越先进,使用复杂特定开发软件即意味着需要更多的精力。

例如,随着FPGA厂商逐步提高产品集成化,在芯片中涉及大量的LUT结构、高性能运算单元、应用处理器、内存层次资源等。虽然体系结构的复杂化增强了产品并行处理性能的优势,但也增加了客户编程的复杂性。因此,一旦客户设计团队熟悉供应商特定的开发软件,再切换到其他供应商的学习曲线变十分陡峭。从某种程度上说,对于Altera和Xilinx而言二者在起步阶段并无重大的、领先的器件优势,而各自软件优势(包括运营)反而会使得二者的市场份额保持相对稳定。

先发优势下,IP核资源的积累逐步巩固护城河,并可创造边际成本接近为0的类AMD模式。IP核也称为知识产权核或知识产权模块,是集成电路中可重用设计方法学中针对芯片设计的可重用模组。对于FPGA,通过将更多的系统级设计工具和IP内核与其结合使用,可以增强FPGA与其他方案相比的竞争优势。

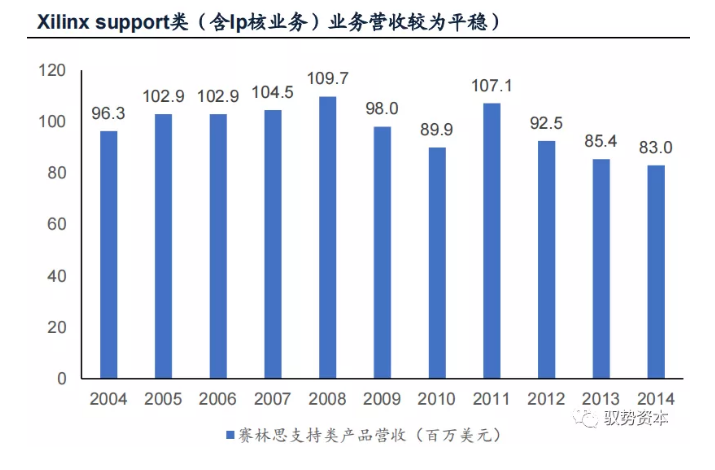

对于FPGA厂商而言,更多使用的硬IP内核(用来提供设计最终阶段产品,嵌入在PLD电路中),与软IP核(使用Verilog、VHDL等硬件描述语言的功能块)相比可实现更低成本、更高性能与更低功耗。例如,对于Xilinx,2014年其支持类产品(软件、配置方案、IP核以及设计设备)实现收入0.83亿美元,占总销售收入的3.5%。相比于硬件销售,IP核等作为研发费用已前置的产品,对于Xilinx而言销售给客户的边际成本接近为零,具备高利润率、易复制等特征。

高中低端互补、差异化与集成化共存的产品布局战略。具有从45nm到7nm的全制程覆盖,利于Xilinx拓宽其产品应用范围及目标客户,进一步增强客户粘性,并在一定基础上通过多群体开发降低FPGA在设计与开发环节的算法、语言的难度与丰富IP核资源库,本质上将推动FPGA向大众化开发方向发展。此外,Xilinx在基站、航空航天、数据存储、汽车等多应用场景的拓展,利于降低单一市场波动对企业经营的影响,提高抗宏观及中观风险能力。

集成平台,实现多器件综合突破现有市场限制并增加客户粘性

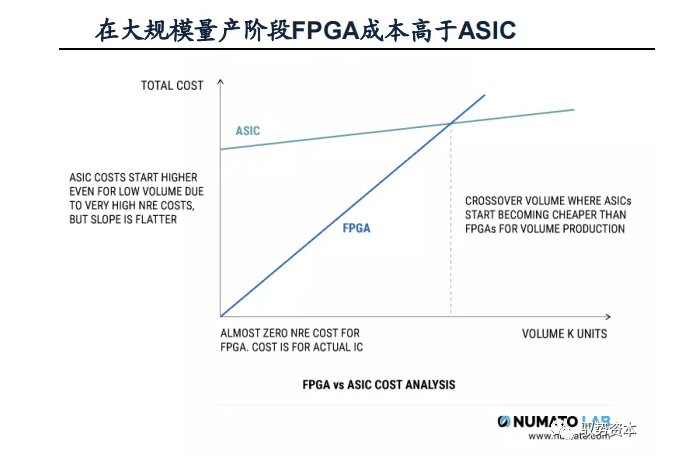

相比于AISC在量产期的低成本,FPGA在发展初期往往更多用于量产规模小的原型制造、产品初期验证或者与其他芯片共同出售,限制FPGA的规模应用与市场开拓。

因无需高额流片即可验证芯片产品,在量产初期或者开展研发类项目,FPGA的性价比优势最为明显,可实现对ASIC的部分替代。但当量产规模提升后,FPGA的性能优势以及成本优势反而下降,且该时期内FPGA的传统优势——可编辑性带来的灵活性——反而对产品及市场推广意义较低,因此该时期OEM厂商通常会使用ASIC。

FPGA与ASIC在多方面的比较总结:

项目FPGA:

1.可重配置电路。可以使用不同的设计重新配置FPGA。他们甚至有能力在芯片的其余区域仍在工作时重新配置一部分芯片!此功能已广泛用于数据中心的加速计算中。

2.通常使用诸如VHDL或Verilog之类的硬件描述语言(HDL)来指定设计。

3.更容易进入,可以低至30美元的价格开始进行FPGA开发。

4.不适合大批量生产。

5.较低的能源效率,需要相同功能的更多功率,而ASIC可以以更低的功率实现相同的功能。

6.与类似过程节点的ASIC相比,工作频率受限制。路由和可配置逻辑占用了FPGA中的时序裕量。

7.FPGA无法进行模拟设计。尽管FPGA可能包含特定的模拟硬件,例如PLL,ADC等,但它们在创建RF收发器方面并不十分灵活。

8.FPGA非常适合于雷达,手机基站等应用,在这些应用中可能需要升级当前设计以使用更好的算法或更好的设计。在这些应用中,FPGA的高成本不是决定因素。相反,可编程性是决定性因素。

9.首选用于原型设计和验证设计或概念。许多ASIC都是使用FPGA本身原型化的!主要的处理器制造商自己使用FPGA来验证其片上系统(SoC)。使用FPGA原型设计可以更轻松地确保设计按预期正常工作。

10.FPGA设计人员通常不需要关心后端设计。一切都由综合和路由工具处理,以确保设计按RTL代码中的描述工作并满足时序要求。因此,设计人员可以专注于完成RTL设计。

项目ASIC:

1.永久电路。一旦将专用电路绑扎到硅中,就无法更改它。该电路将在整个使用寿命内保持相同的工作状态。

2.与FPGA相同。使用HDL(例如Verilog,VHDL等)指定设计。

3.在成本,学习曲线,与半导体代工厂的联系等方面,进入壁垒非常高。从头开始进行ASIC开发可能耗资数百万美元。

4.适用于非常大批量的生产。

5.功耗比FPGA高得多。可以非常精细地控制和优化ASIC的功耗。

6.由于其电路针对其特定功能进行了优化,因此使用同一处理节点制造的ASIC的运行频率要比FPGA高得多。

7.ASIC可以在同一芯片上具有完整的模拟电路,例如WiFi收发器以及微处理器内核。这就是FPGA所缺乏的优势。

8.ASIC绝对不适合可能需要频繁或一次升级设计的应用领域。

9.除非经过绝对验证,否则不建议使用ASIC对设计进行原型设计。一旦硅被录音,几乎无法做任何事情来修复设计错误(有例外)。

10.ASIC设计师需要注意从RTL到复位树,时钟树,物理布局和路由,过程节点,制造约束(DFM),测试约束(DFT)等的所有内容。通常,每个提到的区域都由不同的专家来处理。

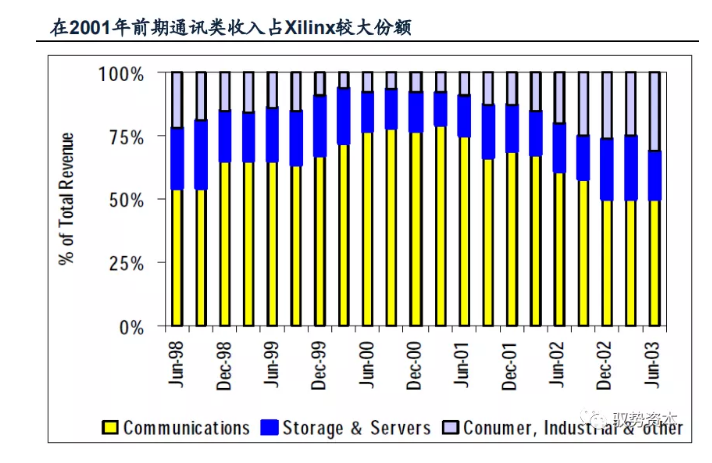

量产后期带来的成本劣势等易限制FPGA的应用。简单来说,FPGA在市场上的强大卖点是产品的快速发展和不断变化的标准。自1985年Xilinx推出全球第一款商用FPGA以来,在90年代末期公司业绩(以及全球FPGA市场)主要由通信产品推动。在通信等领域,FPGA有着广泛的应用,因其需要高速的通信协议处理方式(契合FPGA的优良并行处理能力),另一方面通信协议随时都在修改(契合FPGA的可编辑性),不适合做成专门的芯片,所以具备可编辑性的FPGA就成为相关通信厂商权衡成本与性能后的首选。

总结看,数量需求、价格以及成本敏感性成为PLD厂商盈利能力与收入提升与增长的最大障碍之一。同时,除通信领域以及规模化应用前的ASIC验证外,高速数字信号处理领域也是FPGA的传统优势领域,如军工、航空航天等领域。但该领域的潜在增长与规模相比于消费端仍有一定差距。基于此,Xilinx在1998-2001时期通信类产品收入占公司总收入接近75%(月度)。

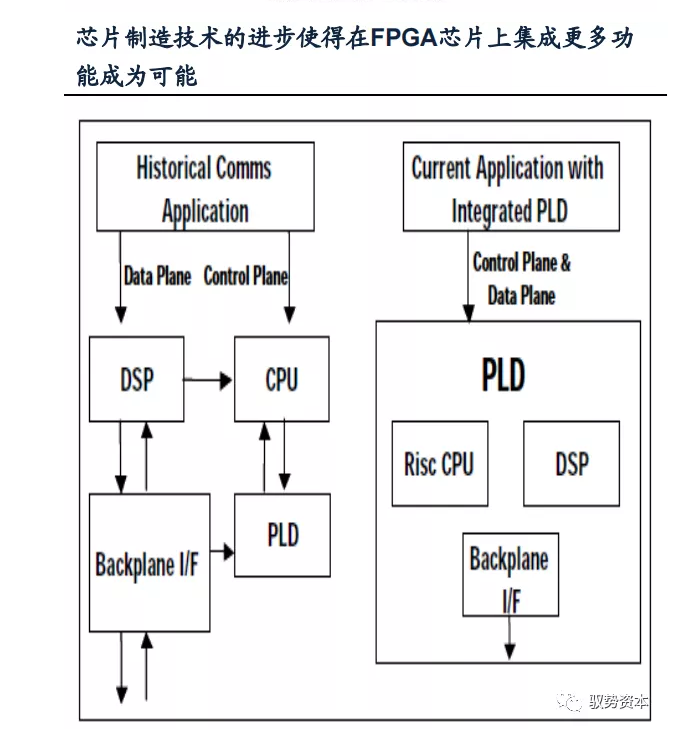

芯片制造技术的进步使得Xilinx可以在原有产品上集成更多功能,继而打破现有应用市场的限制。相比于此前的单纯可编程门阵列架构,得益于芯片制造技术的进步(摩尔定律推动下,集成电路晶体管数量在单位晶圆面积下扩增,同时成本也更低),Xilinx通过推出高端产品集成更多功能,提供更低价格的集成解决方案。例如,2001年后期Xilinx在其高端Virtex产品和Spartan产品线中实施该战略,借此切入潜在市场规模更大的DSP或者MCU等市场。

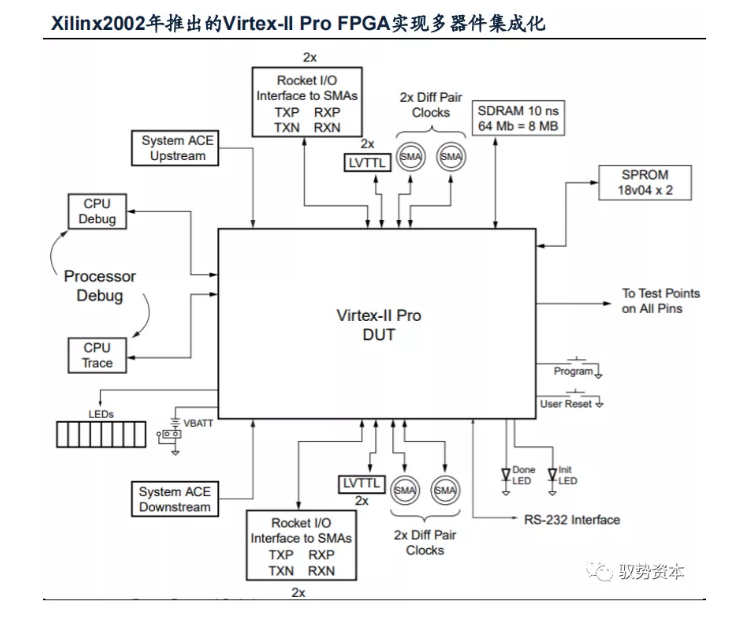

高端产品实现集成化与低成本化,增强产品竞争力与客户粘性,并进一步向对价格敏感程度高的消费级市场拓展。2002年,Xilinx发布Virtex-IIProFPGA系列产品,并在2003年发布新价格点,总体价格水平比2002年降低多达50%,Xilinx主要将这一业界领先的新价格水平归功于采用300毫米晶圆制造工艺以及同类产品中最小的芯片尺寸。在当时,该产品可提供同类产品中功能最强大、成本最低的解决方案——以不到30美元的价格提供集成有超过6700逻辑单元和500K位嵌入式块存储器,以及一个嵌入式PowerPC处理器和四个RocketIO串行收发器的FPGA器件;以不到100美元的价格提供集成有2万个逻辑单元和1.5M位嵌入式RAM,以及两个PowerPC处理器和八个RocketIO收发器的FPGA器件,具备业内领先的产品竞争力。除价格降低外,得益于同步开发的Virtex-IIProEasyPath解决方案,客户使用门槛逐步降低。

Virtex-IIProEasyPath解决方案是彼时业界速度最快且风险较低的可编程逻辑解决方案成本降低途径,可进一步提供高达80%的成本节约。利用该系列产品解决方案,客户进行复杂系统设计不仅可继续利用Virtex-IIProFPGA作为系统的关键单元,同时还拥有通过Virtex-IIProEasyPath解决方案投入生产的灵活性,实现对客户的进一步绑定。开发较低器件密度产品,为客户提供可大批量应用的低成本解决方案,实现向规模性较为突出、对价格敏感的消费级市场拓展。对于需要较低器件密度的大批量应用,Xilinx公司提供世界上成本最低的FPGA产品线——Spartan-IIE系列产品为新应用提供了高达60万系统门的逻辑密度和高达514个I/O引脚,并实现低成本化,并随该系列产品的扩充,Xilinx进一步巩固了自己在为FPGA和ASIC客户提供针对低成本应用(如机顶盒、等离子显示屏和广播视频设备)的大I/O数器件方面的领导地位。

扩张边界,从客户需求出发降低软件编程壁垒与产品应用局限

从客户需求出发,协助客户从FPGA向ASIC实现转变,为客户提供可行的芯片研发低成本路径。如上文所述,如果客户若希望实现规模化量产与应用,从成本与性能角度考虑一般会从PLD过渡到自行设计的ASIC。为减少此类客户的流失及增强粘性,Xilinx及其竞争对手Altera(目前已被Intel收购)提供了过渡路径。

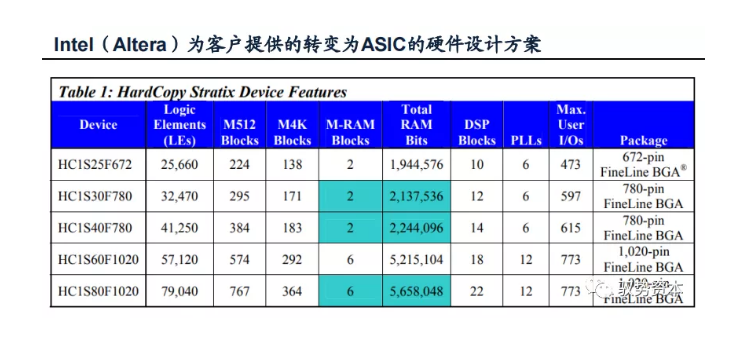

对于Xilinx,根据客户所要求的用途定制测试设备而后将其出售。Altera提供了一项称为“Hardcopy”的政策,具体方案为,根据客户的PLD设计,Altera将为他们创建结构化的ASIC或半定制芯片。然后,Altera将节省的成本(可以在90%的范围内)转嫁给客户,并可实现对客户的挽留,这种半定制设计方法可以为客户提供技术优势和卓越的性能。

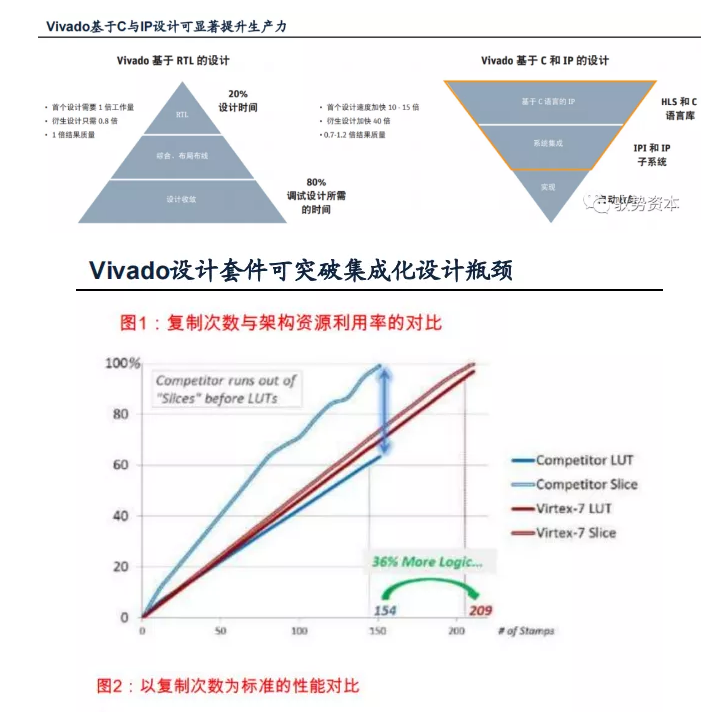

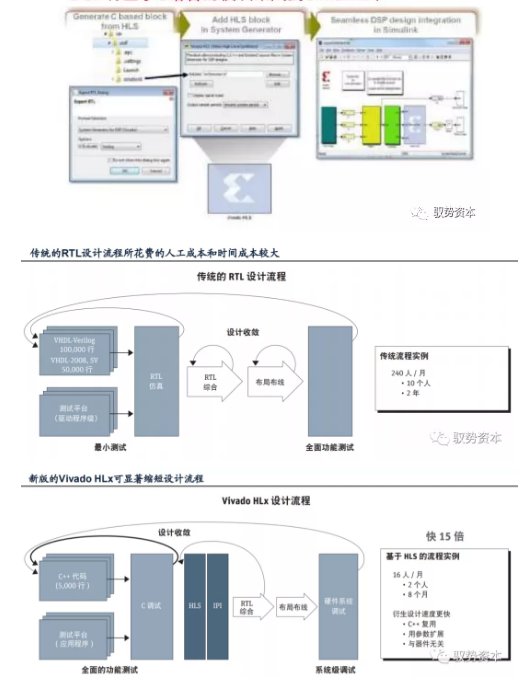

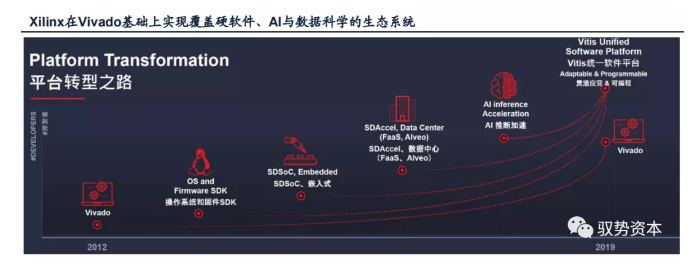

FPGA规模普及难点之一为较高难度的编程设计(客户角度),因此Xilinx一直致力于增加软件的通用性以进一步降低客户的使用壁垒。对于更新周期极快的IC行业,客户需要便捷方便的设计环境,以提升生产力、缩短上市时间、尽可能实现集成化需求。2012年,Xilinx推出从2008年开始编译的集成设计环境——Vivado设计套件,该套件包括高度集成的设计环境和新一代从系统到IC级的工具,是一种以IP和系统为中心的、领先一代的全新SoC增强型综合开发环境,可解决用户在系统级集成和实现过程中常见的生产力瓶颈,并在后续逐步升级。

一方面,该套件可为客户解决集成化、组件化的设计瓶颈。例如,Vivado设计套件采用了用于快速综合和验证C语言算法IP的ESL设计,实现重用的标准算法和RTLIP封装技术,标准IP封装和各类系统构建模块的系统集成,模块和系统验证的仿真速度提高了3倍,与此同时,硬件协仿真性能提升了100倍,相对于同类竞争工具,Vivado设计套件从总体上把集成度和实现速度提高至原来的4倍。

另一方面,降低客户设计门槛、增加IC设计的便捷性。Vivado开发套件支持C语言到RTL的映射,以及支持亿门级电路设计。简单来说,一般业绩算法开发常采用C、C++和SystemC高级编程语言。在过往FPGA设计流程中,需要经过缓慢且容易出错的步骤来将采用上述语言编写的算法转换为适合于综合的Verilog或VHDL硬件描述,而Vivado开发套件系统版本中提供的Vivado高层次综合功能可轻松自动地完成之一步骤。

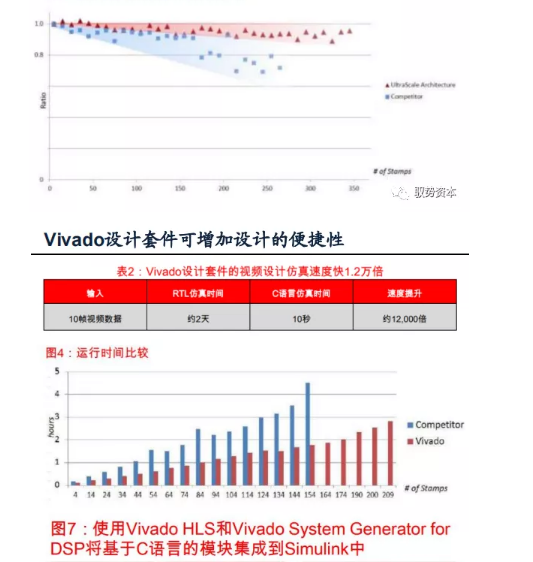

此外,更为关键的是,该功能的实现,保证了IP核的丰富程度,让系统和设计架构人员可将生产的IP硬核轻松嵌入基于RTL的设计流程中,使得硬件设计人员将更多时间投入设计领域、找出理想的设计解决方案,打破传统的RTL设计生产力的局限性。该版本在后续得到逐步更新,如在最新的Vivado HLx Editions中,因采用了基于C/C++的设计和加速复用、特定领域专用库、IP子系统、集成自动化、加速设计收敛等,相比采用传统方法而言,可将用户的生产力提高10-15倍。例如,对于视频运动估算算法,C输入到Vivado HLS这种方式能够在10秒内执行10帧视频数据,而对应的RTL模型处理同样的10帧视频则需要大概两天时间才能完成。

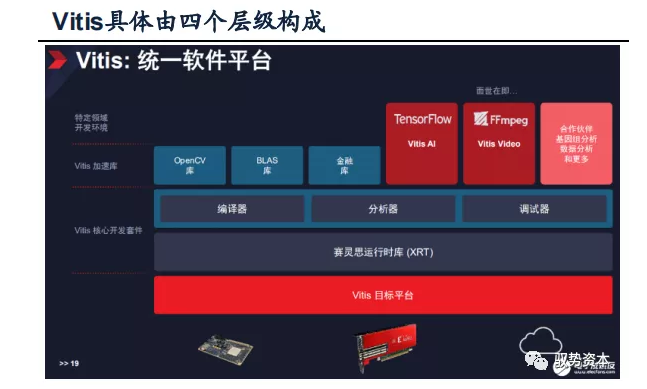

为适应人工智能与机器学习需求推出软件设计平台,免费开放加强生产系统建设,主动切入英伟达目前主导的广阔机器学习市场,并在Vivado的基础上实现覆盖硬件、软件、AI与数据科学家的开发生态系统。Xilinx历经五年、投入1000个工人年,于2019年推出Vitis统一软件平台,并宣布其重要组件Vitis AI开放下载。ViTIs统一软件平台无需用户深入掌握硬件专业知识,即可根据软件或算法代码自动适配和使用赛灵思硬件架构,并且不限制使用专有开发环境,利用丰富的、优化过的开源库,使得客户可专注于算法的开发。Vitis平台构建在基于堆栈的架构之上,该架构可以无缝插入到开源的标准开发系统与构建环境。

该平台有四个层级构成,基础层为由电路板和预编程I/O构成的目标平台;第二层为Vitis核心开发套件,并提供包括编译器、分析器和调试器等核心开发工具,这些工具设计的目的是希望将可编辑器件的开发能与业界标准的构建系统与开发环境无缝集成;第三层为由8个Vitis库提供的400余种优化的开源应用,借助此类库软件开发者可以使用标准的应用编程接口来实现硬件加速;第四层为具有变革意义的VitisAI,集成的特定领域架构为客户提供了针对AI模型的硬件实现。从最开始的硬件开发平台Vivado,到后面的OS和固件SDK,包括一些嵌入式的软件开发环境,到不同的云计算的开发,Vitis实现将各类环境、语言、库不同,针对包括云和边缘统一到平台,以适应当下AI、机器学习等对计算能力与开发能力的需求。

实现从传统硬件公司转型为软件平台公司。作为公司战略之一,Xilinx致力于“开源”,从2007年开始,成立多个开源库,如GCC、LLYM、U-Boot等。此外,Xilinx还推出了Developer.xilinx.com网站,主要将Vitis专家和相关的开发人员建立起联系,实现资源整合与开放生态系统。

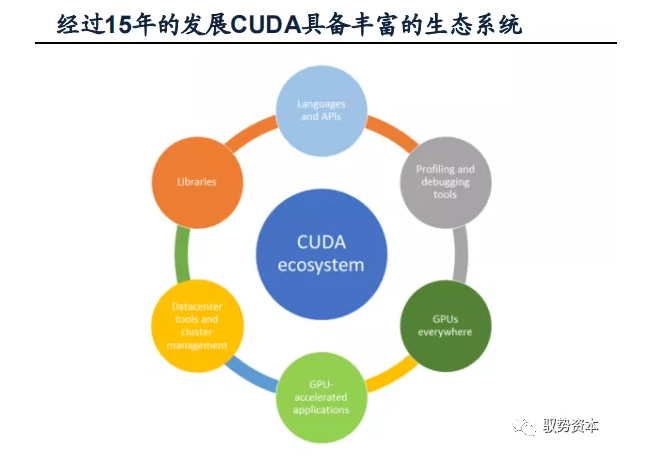

硬件+软件的平台生态是器件生产商成就卓越的必经之路,开发人员的多寡与合作伙伴生态系统的丰富程度为器件生产商平台生态丰富度的重要指标,尤其对于FPGA厂商而言(编程难度及生态系统的薄弱是FPGA拓展市场及客户的重要障碍,如FFCM对于FPGA十大预测从1996年的“We will hate the tools”到2016年时仍称“FPGA design tools will still need improvements”)。参考英伟达,GPU之所以成为目前AI与机器学习的基石,不仅仅是因为GPU强大的大规模并行计算能力,更因为其丰富的生态系统。

2006年英伟基于GPU推出基于GPU做通用计算的CUDA平台,长期经营及丰富资源逐步成为相关开发者首选。对于CUDA,除易于编程与性能提升外(采用通用并行计算架构,该架构使GPU能够解决复杂的计算问题,开发人员可以使用C语言为该架构编写程序,编写出的程度可以在支持CUDA的处理器上高性能运行,并在2010年推出的CUDA3.0支持C++与FORTRAN,目前已支持包括Python在内的多种高级编程语言),与任何新平台一样,CUDA的成功依赖于CUDA生态系统可用的工具、库、应用程序和合作伙伴。也正如黄仁勋在GTC2019技术大会上所说“生态系统是使GPU计算成功的关键”(http://dwz.date/eKUX),并在该大会上发布统一化的生态系统——全新的AI加速计算库CUDAXAI库。通过一致的环境,让NVIDIA的所有产品都能够实现最大限度的软件加速。计算性能接口的最简化,将极大地加速整个软件和应用的开发工作,显著地简化开发流程。

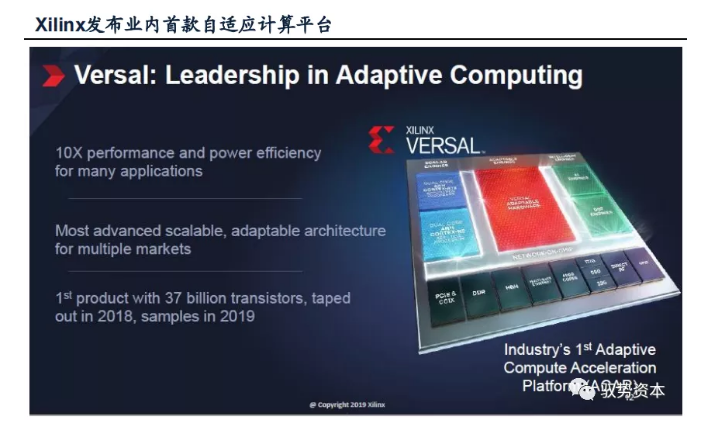

大胆创新改革传统FPGA架构,推出自适应计算加速平台ACAP,契合机器学习算法等对计算资源等需求。2018年3月,Xilinx宣布推出一款超越FPGA功能的突破性产品——ACAP(Adaptive Compute Acceleration Platform,自适应计算加速平台)。ACAP为高度集成的多核异构计算平台,采用台积电7纳米工艺技术开发,可根据各种应用的需求从硬件层对其进行灵活修改,具备在工作过程中进行动态调节的自适应能力,实现了超越CPU和GPU的性能与性能功耗比。

ACAP产品的推出积极契合大数据、AI、机器学习等迅速扩张的需求,可在视频转码、数据库、数据压缩、搜索、AI推断、基因组学、机器视觉、计算存储及网络加速等多项领域实现应用。据Xilinx中文社区2018年3月18日文章(http://dwz.date/eMHv),赛灵思总裁兼首席执行官(CEO)Victor Peng表示:“这不仅对业界来说是一项重大的技术颠覆,更是我们自发明FPGA以来最卓著的工程成就。这款革命性的全新架构是赛灵思更广泛市场战略的一部分,将帮助公司朝着FPGA以外的领域发展,并突破‘仅支持硬件开发者’的局限。ACAP产品在数据中心以及我们广泛市场领域的应用,将加速自适应计算技术的广泛普及,从而让智能、互联、自适应的世界更早成为现实。”

ACAP核心为新一代的FPGA架构,在之前的硬件集成化产品的基础上实现软件可编程,突破原有的硬件限制。据Xilinx官网介绍,ACAP历经4年研发、累计投入10亿美元,其核心是新一代的FPGA架构,结合了分布式存储器与硬件可编程的DSP模块、一个多核SoC以及一个或多个软件可编程且同时又具备硬件自适应性的计算引擎,并全部通过片上网络(NoC)实现互联。

此外,还拥有高度集成的可编程I/O功能,根据不同的器件型号这些功能从集成式硬件可编程存储器控制器,到先进的SerDes收发器技术,前沿的RF-ADC/DAC和集成式高带宽存储器(HBM)。从本质上说,ACAP的本质仍然是基于可编程逻辑阵列的异构计算芯片,但在多个架构上实现了换代与革新,并可为从云、联网至无线通信、边缘计算、端的各个市场的诸多应用提供可扩展性和AI推断功能,切入更为广阔的万物互联市场。

禀赋:IP核资源、多品类集成潜力、硬软件协同

具备IP核资源、多品类集成潜力、高效经营机制的军工FPGA企业有望脱颖而出。复盘全球FPGA巨头Xilinx成长史,且基于FPGA作为标准化IC的认知,我们认为军工FPGA厂商其核心竞争力与民品端一致性较强,核心围绕“先进技术+完整生态”,具体表现为领先的IP数据库以支撑快速的产品迭代与边际递减的研发投入、多品类及系列化的产品布局下具备提供集成化产品增强客户粘性的优势、“硬件+软件”的一站式销售解决客户开发难点及增加客户转换成本。

推荐阅读

驭势资本是一家以研究驱动的硬科技精品投资银行,深耕集成电路、5G、物联网、数据智能和汽车科技领域,为顶尖的科技创业者提供专业资本服务。核心团队在硬科技领域拥有丰富的投融资经验,先后投资及服务的项目包括翱捷科技、臻驱科技、微众银行、微医集团、宏晶科技、晟矽微电子、地大信息、曼荼罗、美林数据、事成股份.

原文链接:https://mp.weixin.qq.com/s/IxWOZauYxGXPZ2gAVtF0Vg