【嘉勤点评】华润微发明的半导体制造方案,解决了传统CMOS生产工艺中漏电路径、隔离失效的问题,通过提高阈值电压补偿区域中空穴的浓度,使得半导体器件能够避免受到辐射后产生电路漏电设置器件误开启、电路误翻转等问题,且可适应太空高辐射环境。

集微网消息,对于应用于离子辐射环境下的集成电路,比如应用于太空,核电站,环境探测等领域,辐射会对集成电路造成验证破坏。因此需要对半导体器件进行工艺加固,以提高集成电路的抗辐射性能。

目前,主流的集成电路都是采用CMOS(互补金属氧化物半导体)架构,CMOS主要有NMOS和PMOS两种类型。而辐射造成的电离损伤主要形成电离正电荷,所以对于PMOS来说,只会造成瞬间集成电路速度变慢,不会产生破坏性结果,随着复合时间拉长会自动恢复。但是对于NMOS来说,会对集成电路形成破坏性损伤。

这也是由于传统的标准CMOS集成电路制造技术制造的芯片,不具备抗辐射能力,因此,辐射产生瞬间阈值电压漂移会造成集成电路漏电甚至器件误开启,电路误翻转等问题。

为实现可应用于离子辐射环境下的CMOS集成电路,华润微在2019年5月21日申请了一项名为“半导体器件的制造方法及半导体器件”的发明专利(申请号:201910421884 .0),申请人为无锡华润微电子有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项半导体器件的制造方案吧。

如上图,为传统方案中的NMOS的平面版图,该结构包括:P阱区102、有源区104、漏极区106、源极区108、栅极区110、接触孔112、多晶硅栅114、栅氧化层116、衬底118和浅槽隔离120,其中多晶硅栅和栅氧化层一起构成器件的栅极区。

这种传统的标准CMOS集成电路制造技术制造的芯片,不具备抗辐射能力,主要原因在于辐射产生瞬间阈值电压漂移会造成集成电路漏电甚至器件误开启,电路误翻转等问题。同时,由于浅槽隔离氧化层在辐射环境下主要产生额外的正电荷,引起硅表面感生负电荷,使得器件在有源区边界区域的阈值电压大幅度降低,会形成漏电路径、隔离失效。

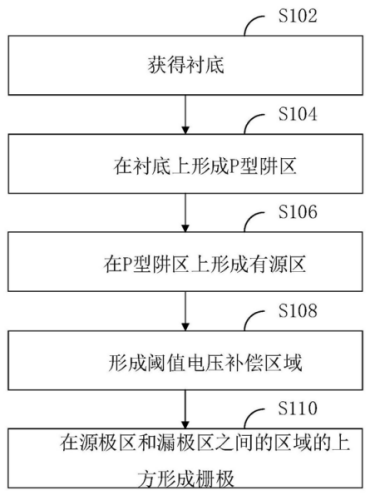

为对上述结构进行改进,该方案中发明了一种新的半导体器件制造方法,如上图所示,该为方法的流程示意图,首先,需要获得衬底,该衬底上形成有用于隔离出有源区的隔离结构。其次,需要在衬底上形成P型阱区,并在P型阱区上形成有源区。

之后,在上述结构基础上,形成阈值电压补偿区域,该电压补偿区域设置在有源区与隔离结构边界处的第一侧和与第一侧相对的第二侧。最后,就可以在源极区和漏极区之间的区域的上方形成栅极。

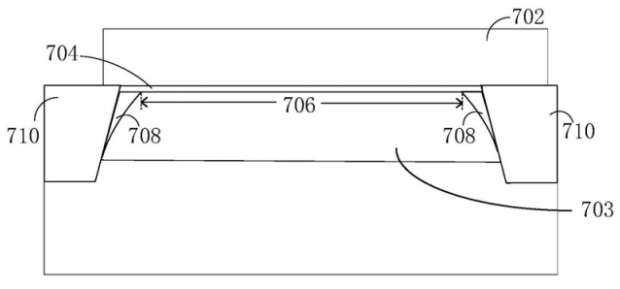

利用该工艺形成的半导体器件结构可如下图所示:

可以看到,有源区包括形成于P型阱区703中的源极区705和漏极区707,阈值电压补偿区域708形成于有源区与隔离结构710边界处的第一侧和与第一侧相对的第二侧,第一侧和第二侧的连线垂直于有源区的导电沟道方向。阈值电压补偿区域的空穴浓度大于P型阱区的空穴浓度,阈值电压补偿区域形成于正常阈值电压区域的两侧。

因此,该工艺流程通过在有源区与隔离结构边界处的第一侧和与第一侧相对的第二侧增设空穴浓度更高的阈值电压补偿区域,能够中和该区域内由于辐射感生的负电荷,从而形成了多阈值沟道结构,能够避免器件受到辐射后产生电路漏电设置器件误开启、电路误翻转等问题。

以上就是华润微发明的半导体制造方案,在该方案中,解决了传统生产工艺中漏电路径、隔离失效的问题,通过提高阈值电压补偿区域中空穴的浓度,使得半导体器件能够避免受到辐射后产生电路漏电设置器件误开启、电路误翻转等问题。