大家好,我是七点班车。记得之前跟朋友说自己撸的SPI NAND FLASH主控能够跑133MHz,朋友很诧异说:“SPI怎么可能跑这么高?”我也很愤怒——事实就摆在这,怎么可能跑不了?到底是哪里来的勇气,让他“口出狂言”,怀疑我的设计?。。。

接下来就用两篇文章来捋一捋鄙人对“源同步接口设计”的一些思考与见解。今天先上Master篇。

1.Master接口的瓶颈

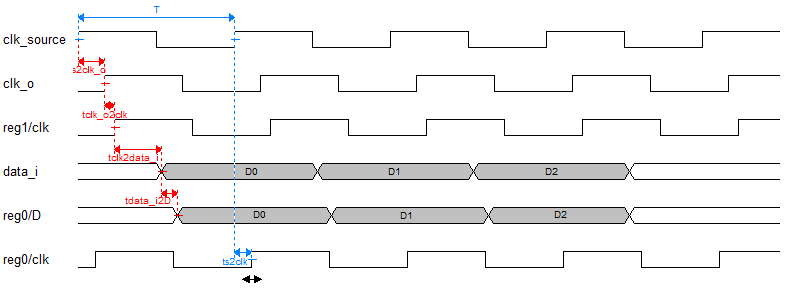

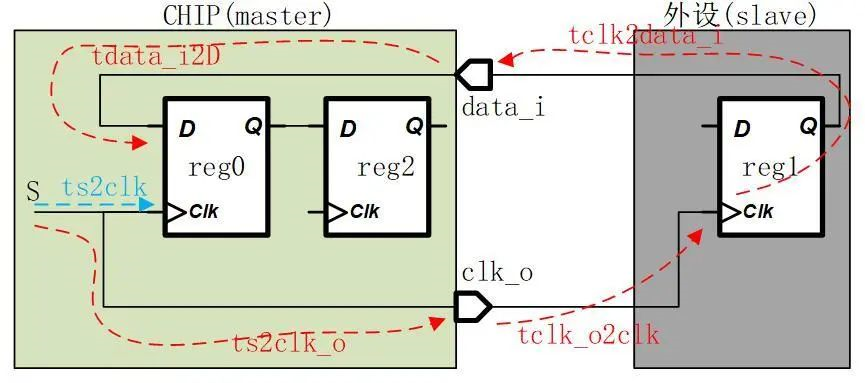

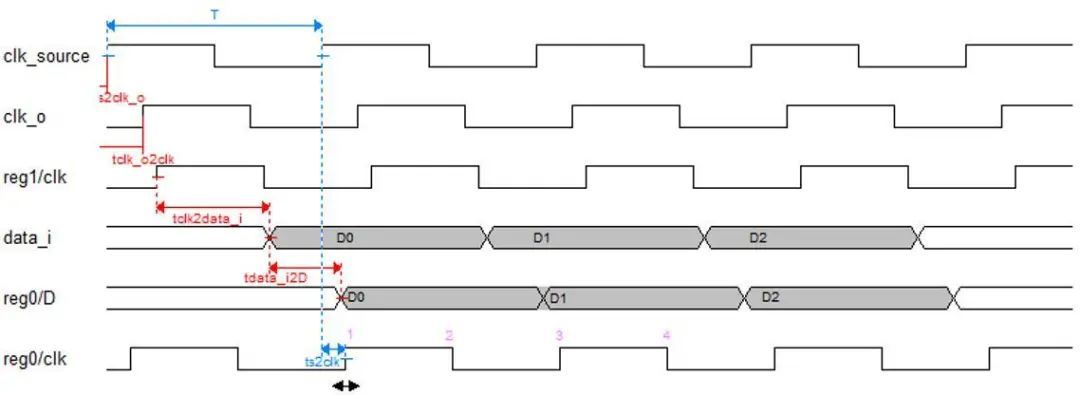

源同步接口在设计中十分常见,例如SPI接口,async NAND FLASH接口。这类接口的时钟由master生成,并经过IO发送到slave中。对master的第一级寄存器来说,有着一段非常长的launch path(如图1.1所示):时钟源S点到IO clk_o -> clk_o到reg1/clk ->reg1/clk到IO data_i -> data_i到reg0/D,如红色曲线,而capture path(时钟源S点到reg0/clk)相对比较短,如蓝色曲线。

图1.1

对于launch比较长,capture path比较短的路径,hold一般都不会有什么问题。但是setup就不一样了,launch path太长,则有可能导致下面公式不满足,从而带来setup违例。因此,接下来,我们就基于setup来讨论下这种源同步接口的设计问题。

为了能够更直观地分析,我们先来看看图1.2的波形图,其中最下面的黑色双向箭头为reg0的setuphold窗口(因为没搞懂怎么用timegen怎么画这窗口,所以只能凑合凑合了)。那么为了保证reg0能够正确地采样,D0必须在setuphold窗口之前保持稳定。用数学式来表示就是,reg0要能正确采样,必须要满足公式(1)。

tlaunch < T + tcapture - tsetup,其中tlaunch= ts2clk_o+tclk_o2clk + tclk2data_i + tdata_i2D,tcapture = ts2clk ——公式(1)

图1.2

我们将图1.1中的数值代入到公式中,可得:2+3+5+4<T+1- tsetup。由于tsetup比较小,这里暂且忽略不计。故可退出T>15ns,即接口的最大频率Freq_max=76.9MHz。天。。。。。。瓶颈在这!

2.提高频率的技巧(非设计层面)

如果要提高频率,要怎么办?我想答案已经很明显了,要么削短tlaunch,要么做长 tcapture。

- 在PCB layout中,将layout线延时tclk_o2clk和tclk2data_i做短。(由于兼容性等客观问题,这个往往不受我们控制)

- 选用延时比较小的PAD(但是,在穷逼的公司,PAD不是说有就有的——骄傲的工程师可以天马行空,但是有时候又不得不接受骨干的现实)。

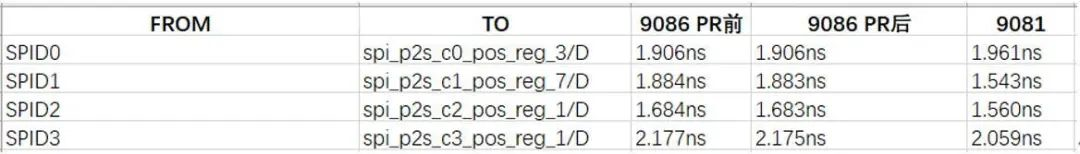

- 在SDC中,将ts2clk_o 和tdata_i2D做短,具体做法是,将clk_o的output delay和data_i的input delay设大,即留给chip内部的delay变小。在STA中,需要格外关注,并把它做短,表1.1是鄙人在项目中统计的tdata_i2D真实值。

- 在PR或者STA fix timing的过程中,将ts2clk做长。但是这样子的做法,有可能会给后面的寄存器带来新的setup问题,如图1.3的reg2。所以一般不会这么干。

表1.1

图1.3

然而,在某种程度上,IC设计上的问题就跟戴绿帽一样,发现得越晚,就越难!所以如果把问题推到STA再去解决的话,可能就是“好吃不过饺子。。。”的梗了。因此,能在设计上动刀,就动吧。

3.提高频率的技巧(设计增加采样点)

咱再来回顾下公式(1),tsetup 是寄存器的特有属性,改不了;除了上面提到的tlaunch和 tcapture,公式中还有一个“T”,我们能否在设计上将它“搞大”?

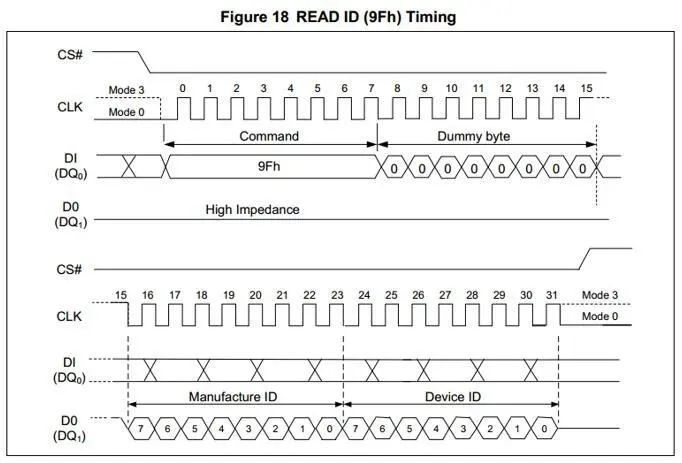

对于同源接口来说,slave就像个机器,它会严格按照协议规定来进行工作。就拿图1.4的SPI NAND FLASH(截图来自复旦微的手册)来说,在接收到命令后,经过一个dummy byte,也就是在第15个时钟下降沿,slave就必须把ID送出来。

图1.4

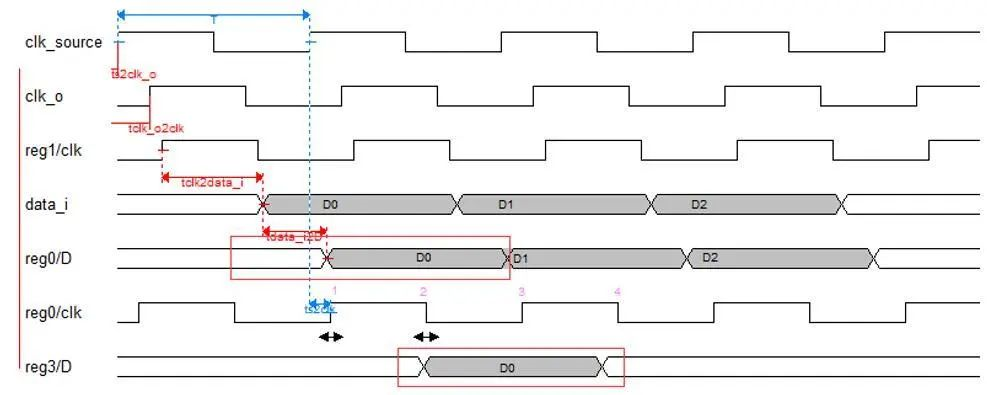

而Master占据了所有的主动权,毕竟它才是生成时钟的主。如果数据在第16个时钟上升沿到达不了,而是在第17个上升沿才到达,那Master也是可以在第17个上升沿才对数据进行采样的。因此,我们在设计Master的时候,可以适当增加一些采样点,每个采样点的间隔是半个周期,如图1.5粉色标号1/2/3/4所示。当D0在采样点1上出现违例时,可以把使用采样点2的数据,而对于采样点2来说,就增加了T/2。依次类推。。

图1.5

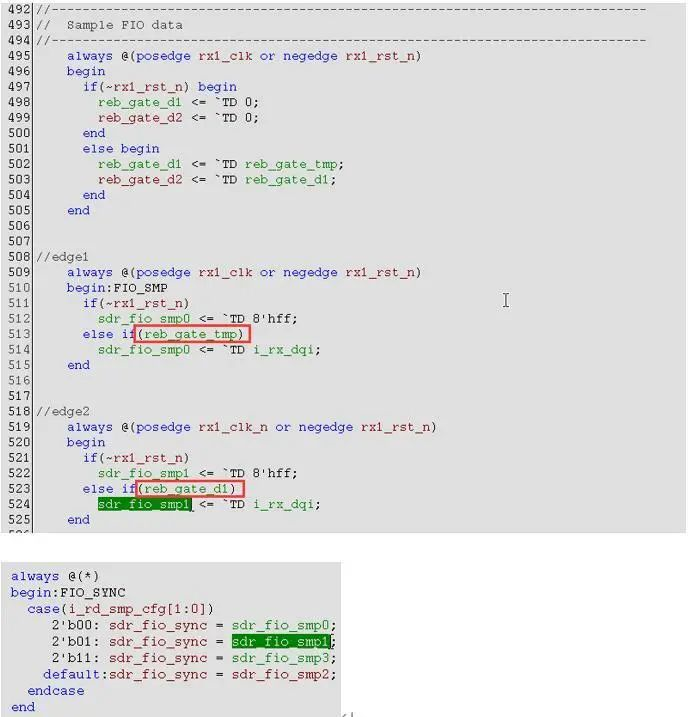

图1.6亮出了部分参考代码,自己慢慢体会吧。

图1.6

4.STA需要关注的bus对齐问题

谈到接口,就多少会涉及bus;涉及bus,就得关注对齐问题。如图1.7,假设reg0/D和reg3/D是数据bus,且这两个信号在电路上会出现重聚。从图中可以看出,无论是在采样点2,还是在采样点3中,就只能采到reg0/D和reg3/D中的一个。显然,两者重聚后,注定是个悲剧。因此,我们在STA中需要格外关注bus skew,不能让它超过半个周期。

图1.7

以上就是今天要分享的内容。谢谢大家!

END

作者:七点班车

原文链接:https://mp.weixin.qq.com/s/bXuULeSKFMsX-7Bwn-n7AA

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏