【嘉勤点评】利普芯的芯片封装专利,通过在多个芯片之间、基岛之间以及引脚之间通过键合线电性连接,能够有效提高封装体的集成度,满足芯片的散热要求,实现产品小型化,节约芯片封装框架的体积。

集微网消息,近日,四川遂宁市利普芯微电子有限公司举行利普芯智能芯片封装测试产业化项目开工仪式。

随着集成电路生产工艺的发展,越来越多的开关电源转换、LED驱动的控制器芯片采用小线宽工艺,提高集成度增强性能。然而在产品应用端要求芯片集成度高,从而实现产品小型化,在一个集成电路封装体里装载控制器芯片、功率器件则成为不二选择。比较常见的有引线框架只包含有两个基岛,分别装载功率器件和控制器芯片,不能满足装载一颗控制器芯片加多个功率器件的要求。

为此,利普芯于2020年9月4日申请了一项名为“一种多芯片封装的集成电路封装结构”的发明专利(申请号: 202021907686.X),申请人为四川遂宁市利普芯微电子有限公司。

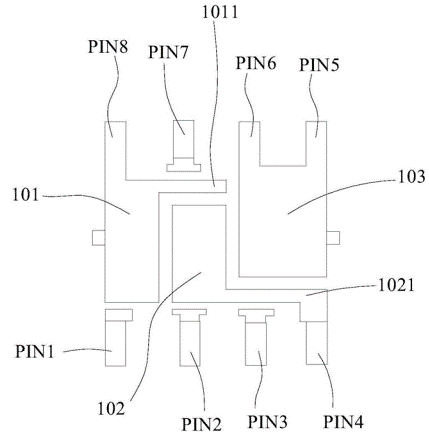

图1

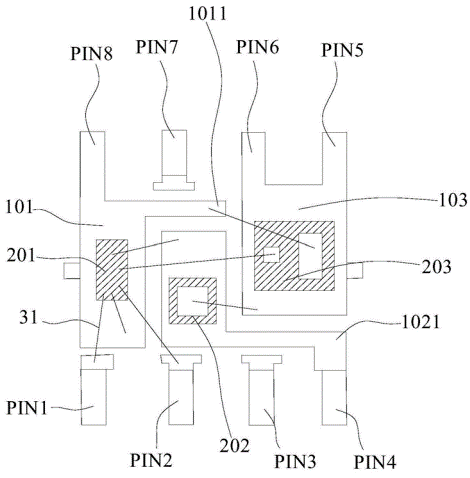

图1为本发明的封装结构框架结构以及芯片安装结构示意图,其中包括共面分布的第一基岛101、第二基岛102和第三基岛103以及多个引脚。第一基岛朝向第二基岛方向的一侧延伸有第一延伸部1011,装载有第一芯片201;第二基岛朝向第三基岛方向的一侧延伸有第二延伸部1021,装载有第二芯片202;第三基岛位于第二延伸部的内侧,装载有第三芯片203。其中,多个引脚至少包括与第一基岛、第二基岛及第三基岛直连的四个引脚,芯片之间、基岛之间以及引脚之间通过键合线31电性连接。

第一第二延伸部分别位于第二基岛的两侧且相互平行,第二第三基岛分别位于第一第二延伸部的内侧。多个引脚包括与第一基岛直连的第八引脚、与第二延伸部的端部直连的第四引脚以及与第三基岛远离第二延伸部一侧的第五引脚和第六引脚。多个引脚还包括与第一基岛分离设置的第一引脚,以及与三个基岛分离设置的第二、第三及第七引脚,第一第二引脚通过键合线与第一芯片电路连接。三个基岛全镀银或边缘环状镀银。

三个芯片分别为控制器芯片、次功率器件芯片、主功率器件芯片。第三芯片包括MOS器件或宽禁带半导体功率器件。第二芯片包括二极管、MOS器件或宽禁带半导体功率器件。其中,宽禁带半导体功率器件包括但不限于氮化镓和碳化硅。在实际使用时,MOS器件可选择使用P型MOS管或N型MOS管,基于宽禁带半导体材料的电力电子器件将具有比硅器件高得多的耐受高电压的能力、低得多的通态电阻、更好的导热性能和热稳定性以及更强的耐受高温和射线辐射的能力。要求的第三基岛的装片区的面积最大,散热面积最大,因此第三基岛的面积最大,且通过第五引脚和第六引脚引出。去掉第二、第三和第七引脚,可增加第一、第四、第六与第八引脚之间的安全间距,使得在AC/DC高压应用场合下也有足够的爬电距离,提升系统的可靠性。

简而言之,利普芯的芯片封装专利,通过在多个芯片之间、基岛之间以及引脚之间通过键合线电性连接,能够有效提高封装体的集成度,满足芯片的散热要求,实现产品小型化,节约芯片封装框架的体积。

利普芯是一家基于芯片封装、测试、设计及整体应用解决方案提供商,其核心管理人员有20年的集成电路设计、集成电路封测行业从业经历。未来,利普芯将持续创新,走向芯片封装领域的前沿。