实验设计目标

- 设计实现一个可容纳四组选手参赛的抢答器系统,每组设一个抢答按钮。答题开始后,由主持人按下“开始”键后进入抢答环节,当某个小组抢答成功时,抢答器系统发出半秒的低频音,显示该组别序号并点亮该组“选手指示灯”直至系统复位。此时进入答题计时环节,若超过30秒仍未答出,抢答器系统发出1秒的高频音示警,同时点亮“超时灯”1秒。由裁判员按下“复位”键,开始新一轮答题。

- 通过此实验学习Anlogic_FPGA开发板上的蜂鸣器的发声原理。

实验设计思路

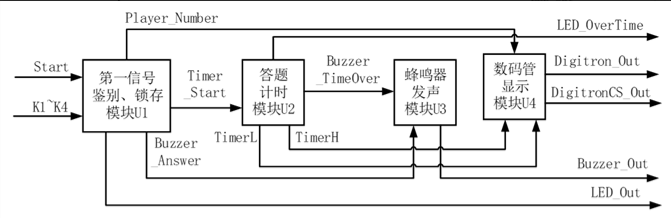

本实验设计实现一个抢答器系统,它由第一信号鉴别、锁存模块,答题计时模块,蜂鸣器发声模块和数码管显示模块组成,图7.1是该系统的示意图。

图7.1 抢答器系统示意图

第一信号鉴别、锁存模块的关键在于准确判断出第一抢答者并将其锁存。设置一个主持人“开始”按钮Start,四个抢答按钮K1、K2、K3、K4,主持人开始后,抢答信号才能被有效识别,在某个小组抢答成功后,其他组的抢答信号无效。本模块输出LED_Out[3:0]、Player_Number[3:0]、Buzzer_Answer和Timer_Start信号。LED_Out用于控制“选手指示灯”;Player_Number存储抢答成功的小组序号;Buzzer_Answer作为“抢答成功鸣笛标志位”,送到蜂鸣器发声模块,控制蜂鸣器的发声频率及时间;Timer_Start作为答题计时模块的“启动标志位”,当某个小组抢答成功后,Timer_Start变为1,启动答题计时器。

答题计时模块的关键在于倒计时的启动,利用Timer_Start信号控制倒计时的开启。在实验六中设计实现了一个加法计数器,类似的,本模块只需实现一个“30-29-…-01-00”的减法计数器即可。本模块输出TimerH[3:0]、TimerL[3:0]、Buzzer_TimeOver和LED_OverTime信号。TimerH和TimerL分别存储倒计时的十位和个位;Buzzer_TimeOver作为“答题超时鸣笛标志位”,送到蜂鸣器发声模块;LED_OverTime用于控制答题“超时灯”。

蜂鸣器发声模块用于控制蜂鸣器的发声频率、何时发声及发声时长。通过标志位Buzzer_Answer和Buzzer_TimeOver控制送到蜂鸣器上的电压值及电压变化频率。Buzzer_Out即为最终送给蜂鸣器的信号。

数码管显示模块用于显示倒计时的时间和抢答成功的组别序号,驱动原理与实验六相同。

功能模块图与输入输出引脚说明

该工程包含顶层模块responder与底层模块Sel_module、Timer_module、Buzzer_module和Digitron_NumDisplay_module。底层模块依次对应于图7.1中从左至右四个功能模块。整个工程的模块功能图参考图7.1即可。下面介绍一下顶层模块各主要引脚的功能:

- CLK:50MHz的基准时钟信号输入。在Sel_module模块中将其分频后产生标准秒脉冲CLK1。

- RSTn:系统复位输入信号。低电平有效,由裁判员控制,复位后系统回到初始状态,“选手指示灯、超时灯”熄灭,蜂鸣器不响,数码管显示“030”。

- Start:抢答开始输入信号。由主持人控制,当Start为1时,各个小组的抢答信号有效。

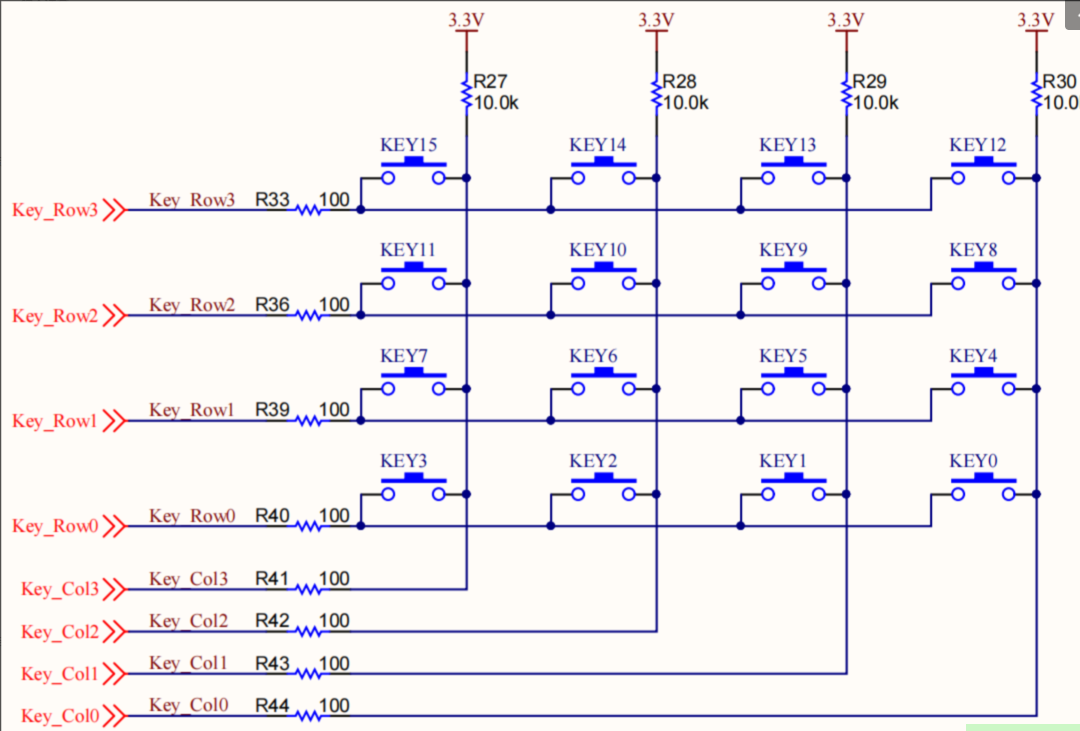

- Key_In:抢答输入信号,Key_In[3:0]连接到矩阵键盘的列信号Key_Col[3:0]上,给Key_Row[3:0]恒定输出4’b0111,当KEY[3:0]中有按键被按下,Key_Col[3:0]对应位输出低电平,表示存在抢答操作。

- LED_Out:“选手指示灯”输出信号,输出到LED灯,共有四位。LED_Out [3:0]分别连接第四组~第一组选手的指示灯,例如若第四组选手抢答成功,LED_Out [3:0]的值为“1000”。

- Buzzer_Out:输出到蜂鸣器。

- LED_OverTime_Out:答题“超时灯”输出信号。LED_OverTime_Out信号与抢答器电路的LED_OverTime相连,控制超时灯。

- Digitron_Out:七段数码管的显示输出,共有八位。

- DigitronCS_Out:数码管的片选信号,共有四位。

程序设计

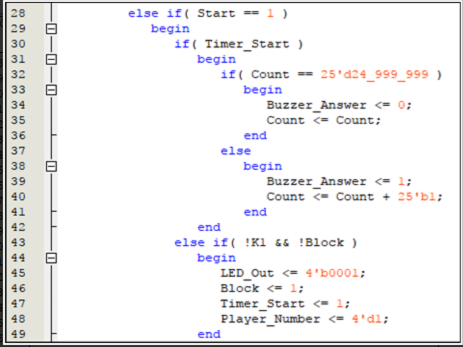

7.3是截取自底层模块Sel_module的部分代码:

图7.2 Sel_module核心代码

- 30-42:Timer_Start是“计时器启动标志位”,当第一信号鉴别、锁存模块锁存了第一抢答信号后,令Timer_Start变为1,启动答题计时器电路。当Timer_Start变为1后,30-42行代码将Buzzer_Answer(“抢答成功鸣笛标志位”)置为1,保持半秒后,再置为0。这里用到了一个很简单的计数器Count,用于控制半秒的时间。

- 43-49:判断是否已经锁存以及第一组别是否有抢答操作,Block是锁存信号,高电平表示电路已锁存。若第一组抢答,且在此之前未有其他组抢答成功(Block为0),45-48行依次为点亮第一组“选手指示灯”,锁存电路,开启答题计时器,将第一组别序号送给数码管。

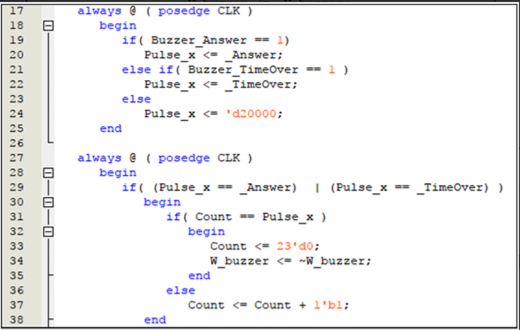

- 图7.3是截取自底层模块Buzzer_module的部分代码,请结合第一篇的1.3节中关于蜂鸣器模块的介绍内容进行理解:

图7.3 Buzzer_module核心代码

- 17-25:通过“鸣笛标志位”控制送到蜂鸣器上的电压和电压变化频率。例如,当某个小组抢答成功时,“抢答成功鸣笛标志位” Buzzer_Answer将被置为1且经过半秒后变回0,这半秒内将常量_Answer的值('d95419)赋给Pulse_x,半秒后Pulse_x的值变为'd20000。

- 29-37:这是一个小型计数器。若Pulse_x的值为“_Answer”或“_TimeOver”,则控制W_buzzer的值以一定频率在“0”和“1”之间翻转,这样便形成了一定频率的脉冲信号。W_buzzer的值即为将送给蜂鸣器的值,该脉冲信号的频率即控制蜂鸣器发声的频率。

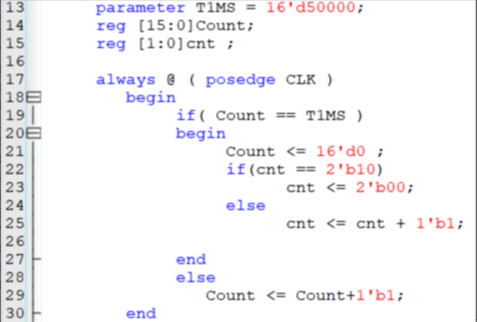

图7.4是数码管显示模块

- 13-30:分频程序,用于产生频率为250KHz的扫描信号,并在每个扫描周期对cnt在0-2循环计数。

- 32-44:片选信号DigitronCS_Out的扫描程序。W_DigitronCS_Out[3:0]信号的值将在程序的最后赋给DigitronCS_Out[3:0]信号,当它的某一位为0时,对应的数码管选中,反之则不选中。在本实验中使用数码管DIG1、DIG0显示显示倒计时数字,DIG2显示抢答号,因而DigitronCS_Out[3:0]的值根据cnt计数结果在“1110,1101,1011”之间变换,变换频率为250KHz。

- 46-76:根据SingleNum信号的值选择输送到数码管的常量,控制字码段的点亮情况。例如当SingleNum的值为4'b1000时,输送到数码管的常量为“_8”, 即Digitron_Out[7:0]的值为8'b0111_1111,字码段A、B、C、D、E、F、G全部点亮,DP(小数点)熄灭,数码管显示数字“8”。

FPGA管脚配置

Anlogic FPGA的IO 分配使用如下:DIG2(DigitronCS_Out[2])显示抢答成功组别的序号,使用DIG1(DigitronCS_Out[1])和DIG0(DigitronCS_Out[0])显示倒计时的十位和个位;复位输入信号RSTn和抢答开始信号Start分别与开发板上的SW0和SW1相连;Buzzer_Out信号输出到蜂鸣器引脚;

观察矩阵按键的原理图,Key_In[3:0]代表物理按键KEY3 - KEY0,他们分别与矩阵按键的Key_Col[3:0]相连,因此当我们给Key_Row[3:0]输出恒定的4’b1110时,按下KEY0,Key_Col[0]就会出现低电平;

LED_Out[3:0]分别输出到LED3~LED0,LED_OverTime_Out输出到LED7,LED7点亮表明答题超过30秒。

set_pin_assignment { Buzzer_Out } { LOCATION = H11; IOSTANDARD = LVCMOS33; }

set_pin_assignment { CLK } { LOCATION = R7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[0] } { LOCATION = C9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[1] } { LOCATION = B6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[2] } { LOCATION = A5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[3] } { LOCATION = A3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[0] } { LOCATION = A4; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[1] } { LOCATION = A6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[2] } { LOCATION = B8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[3] } { LOCATION = E8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[4] } { LOCATION = A7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[5] } { LOCATION = B5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[6] } { LOCATION = A8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[7] } { LOCATION = C8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_In[0] } { LOCATION = E11; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_In[1] } { LOCATION = D11; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_In[2] } { LOCATION = C11; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_In[3] } { LOCATION = F10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[0] } { LOCATION = B14; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[1] } { LOCATION = B15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[2] } { LOCATION = B16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[3] } { LOCATION = C15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[4] } { LOCATION = C16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[5] } { LOCATION = E13; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[6] } { LOCATION = E16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_OverTime_Out } { LOCATION = F16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { RSTn } { LOCATION = A9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Start } { LOCATION = A10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[0] } { LOCATION = E10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[1] } { LOCATION = C10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[2] } { LOCATION = F9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[3] } { LOCATION = D9; IOSTANDARD = LVCMOS33; }

抢答器系统IO Constraint

实验结果

当SWO和SW1均拨至“UP”时,系统进入抢答环节。若假设第二组选手抢答成功,此时蜂鸣器鸣低频音并持续半秒钟,灯LED1点亮,数码管DIG2将显示“2”,DIG1和DIG0将显示倒计时数字;若答题超过30秒,灯LED4将点亮1秒,蜂鸣器鸣高频音并持续1秒钟,DIG1和DIG0显示“00”并保持直到系统复位。因篇幅受限,其他情况请自行验证。

思考与拓展

- 新建一个工程,自行设计程序或查询相关资料,实现以下功能:①计分功能,每组开始预置5分,由主持人计分,答对一次加1分,答错一次减1分;②抢答未开始前若有人抢答则报警并点亮相应选手指示灯。

- 本实验初次使用蜂鸣器显示实验结果,请仔细理解蜂鸣器的工作方法,并新建工程,实现按键控制蜂鸣器发“Do、Re、Mi、Fa、Sol、La、Si”音阶的功能。实际上本实验中的低频音和高频音即为“Do、Si”,频率的计算方法参考实验5.3中的公式(5.3)。各个音阶的参考频率依次为262、294、330、349、392、440和494Hz。

END

文章来源:https://www.yuque.com/yingmuketang/01/gvt2t3

推荐内容

- 【安路 EG4S20 版本】基础板卡信息及使用教程:芯片和板卡简介

- 【安路 EG4S20 版本】基础板卡信息及使用教程:第一工程

- 【安路 EG4S20 版本】基础板卡信息及使用教程:使用ChipWatcher

- 【安路 EG4S20 版本】基础板卡信息及使用教程:使用Modelsim

- 【安路 EG4S20 版本】基础实验设计与实现:实验1 流水灯

- 【安路 EG4S20 版本】基础实验设计与实现:实验2 集成逻辑门及其基本应用

- 【安路 EG4S20 版本】基础实验设计与实现:实验3 译码器 编码器

- 【安路 EG4S20 版本】基础实验设计与实现:实验4 数据选择器

- 【安路 EG4S20 版本】基础实验设计与实现:实验5 触发器

- 【安路 EG4S20 版本】基础实验设计与实现:实验6 加法计数器

更多内容请关注走进FPGA专栏