简介

做FPGA开发的一般都不会使用IDE环境自带的编辑器,一是因为界面不够美观,二是自动补全功能不够完善,编码效率太低。而我经常使用的是Notepad++,支持Verilog语法高亮和最基本的关键字补全,但是对于一些经常使用的模块,需要手动重复性的输入还不够完善,最近偶然发现一款插件,可以根据输入的关键字,自动生成一部分代码片段,非常方便。它就是Finger Text,Notepad++的一款扩展插件。

通过创建多个关键字和代码片段,可以大大提高编码效率,节省编码时间,让开发人员把更多的时间投入到设计和调试过程。

支持以下基本功能:

- 触发键默认为TAB,可自行设置

- 根据指定的关键字,自动输入所对应的代码片段

- 支持系统关键字补全,日期、时间、文件名、文件路径等

- 支持触发调用系统控制台命令

- 支持自动计算数学算式

- 支持单个/所有关键字配置文件的导出和导入

官方主页:https://sourceforge.net/projects/fingertext/

安装方法

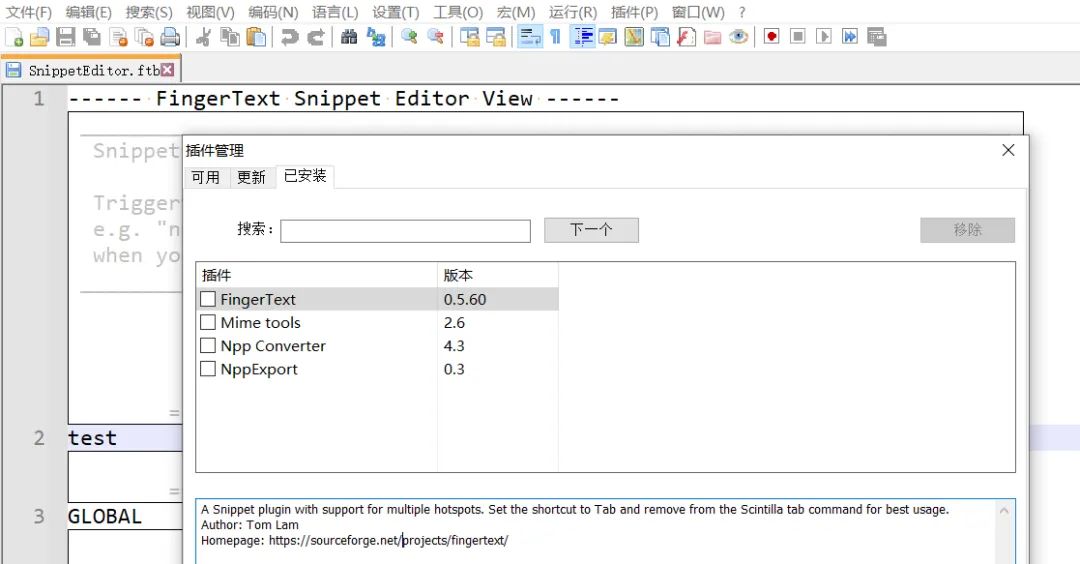

Finger Text插件目前只支持Notepad++编辑器,最新版本的Notepad++可以通过自带的插件管理方式安装。

旧版本的编辑器需要单独下载插件dll文件,然后放在Notepad++\plugins文件夹下。

使用方法

例如,我们在进行Verilog编码时,经常会用到always块,基本结构如下:

always @ (posedge clk) begin

if(!rst_n) begin

//...

end

else begin

//...

end

end虽然只有短短几行,但是每天如果要输入几百个这样的always块,所占用的时间也是非常多的。那么如何使用fingertext插件,当我们输入al时自动替换为以上格式的always模板呢?

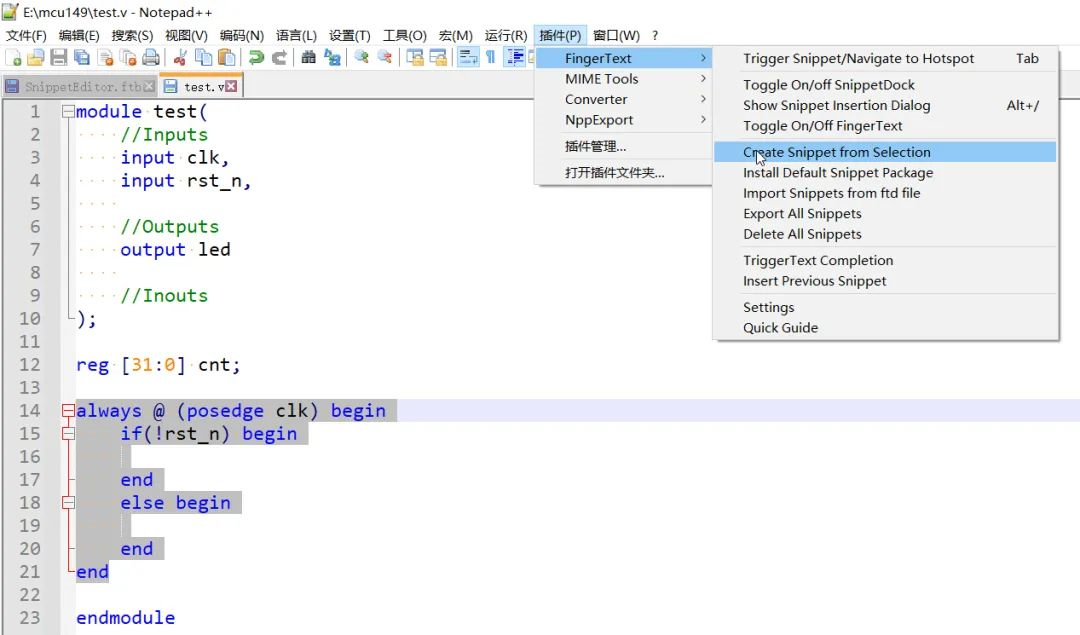

先选中一段always块,选择插件->FingerText->Create Snippet from Selection:

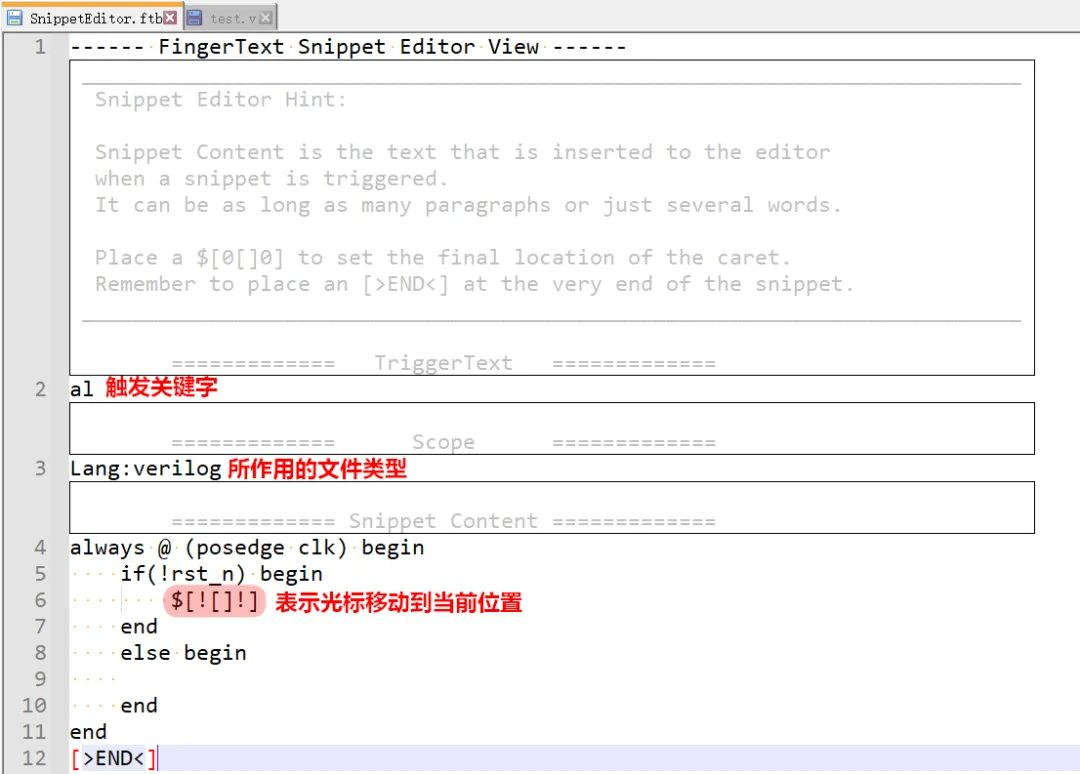

然后在弹出的界面中,设置触发的关键字,所作用的文件类型(全局/扩展名/编程语言),这里选择只在Verilog文件有效。

$[![]!]表示代码片段生成之后,光标移动的位置。

末尾的[>END<]表示代码片段的结束,在此之后,可以输入一些注释信息。

配置保存之后,在Verilog文件中,输入al之后,按下TAB键的效果:

其他的配置条件:

$[![]!] //按TAB键之后跳转的位置

$[0[]0] //光标最后停留的位置

$[![var_name]!] //所有相同名称的变量都会被同时改变

$[![(key)DATE]!] //2022年3月12日

$[![(key)TIME]!] //14:05:22

$[![(key)FILENAME]!] //top

$[![(key)EXTNAME]!] //.v

$[![(key)DIRECTORY]!] //E:\\mcu149

$[![(key)PASTE]!] //当前剪贴板的内容

$[![(run)calc]!] //执行控制台命令:打开计算器

$[![(run)explorer]!] //执行控制台命令:打开资源管理器

$[![(lis)Sunday|Monday|Tuesday|Wednesday|Thursday|Friday|Saturday]!] //下拉式字符串选择

$[![(opt)Sunday|Monday|Tuesday|Wednesday|Thursday|Friday|Saturday]!] //下拉式字符串选择

$[![(lis)Sunday|wire|reg|parameter|localparam|assign]!] //输入字符串之后,可以按TAB键触发其他关键字

$[![(opt)Sunday|wire|reg|parameter|localparam|assign]!] //输入字符串之后,可以按TAB键执行其他命令

$[![(eva)1+2-3*4/5]!] //0.6

$[![(cha)wir]!] //插入别的已经定义的关键字

关键字触发替换成普通字符串:

系统关键字,日期、时间、文件名等。

lis效果,按上下键选择,按ENTER键确定。:

opt效果,按上下键选择,TAB键确定。:

打开控制台命令,如计算器、资源管理器等。

在Verilog中的应用:

文件头,关键字head:

模块端口声明,关键字mod:

1位输入信号i1,n位输入信号ix:

1位输出信号o1,n位输出信号ox:

1位输入输出信号,n位输入输出信号:

1位wire和n位wire定义:

1位reg和n位reg定义:

1位assign和n位assign:

localparam和parameter定义:

memory定义,关键字mem:

if语句,关键字if1:

generate模块,关键字gr:

移位寄存器定义,关键字sreg:

always定义,关键字aw:

状态机定义,关键字fsm:

生成模块整体框架,关键字temp:

testbench模板:

$display,关键字dp:

function函数,关键字fc:

task模板,关键字tsk:

还可以把以上几个合并成一个关键字:

来源:电子电路开发学习

作者:wcc149

推荐阅读

更多技术干货请关注电子电路开发学习专栏。