【嘉勤点评】台积电发明的通过改进鳍片结构而完成芯片微缩化的集成电路装置方案,通过新型的鳍片结构以及利用介电质的堆叠,实现了更高尺寸的鳍片结构。不仅有利于提高芯片的性能,同时也有利于实现芯片的微缩化。

集微网消息,现代科技在集成电路材料的设计上取得了卓越的成就,并逐渐发展了好几代集成电路。每一代与上一代相比,均具有更小、更复杂的结构,在减少尺寸的同时增加了芯片的功能密度。

这个微缩化的过程,总体上是以增加生产效率与降低相关成本为目的,同时也使得集成电路结构变得愈加复杂。因为当芯片尺寸不断缩小时,芯片的性能和晶体管能效管理会变得更加难以控制。

现有技术中,通常采用鳍式场效晶体管装置来改善芯片的性能,因为在这种晶体管装置中,栅极环绕着通道的三个侧面,通常将虚置栅极形成于平行走向的鳍片结构上方,接着在栅极的侧壁上形成侧壁间隔物。在侧壁间隔物形成后,再在栅极两侧的鳍片结构上形成源极和漏极区。其中,虚置栅极可以用真实栅极取代,例如使用金属材料等导电材料。

然而,当节点的节距尺寸变得越来越小时,多个鳍片结构之间虚置栅极的空间也变得越来越狭小,在重蚀刻时可能会对鳍片结构造成损害,并因此限制了鳍片结构的节距与尺寸的小型化发展。

因此,台积电在2021年3月15日申请了一项名为“集成电路装置的结构及其制造方法”的发明专利(申请号:202110274387.X),申请人为台湾积体电路制造股份有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项方案吧。

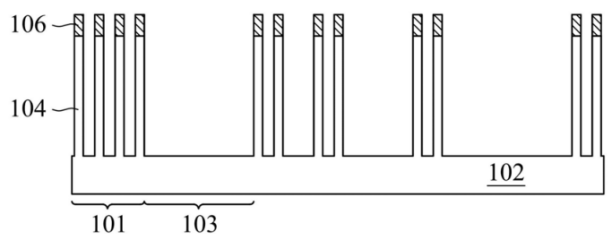

如上图,为具有改善节距微缩化的鳍式场效晶体管的结构示意图,在基板102上形成有一组鳍片结构104,可以看到,空间103将许多个鳍片结构分隔成不同的群集101。在该方案中,这些鳍片结构的节距小于24纳米,鳍片结构之间的空间距离范围为约5~10纳米,高度为50~60纳米。由此,相较于普通的鳍片,这些鳍片的高度就显得很大了,而更高的鳍片也有助于改善装置性能。

这些鳍片的结构均为伸长的鳍片状结构,其走向彼此互相平行,从上图中,我们也可以从垂直剖面的视角看到鳍片结构走向的方向。此外,该方案的半导体基板使用的是硅基板,其也是硅晶圆的一部分,在结构上是一种具有均匀组成的单一膜层的材料。在鳍片结构上,还形成有硬遮罩层106与光刻胶层,光刻胶通过掩膜暴露于光源下,紧接着就被显影以保留所需要的部分。

而在每组鳍片之间都留有大面积的空白,这部分就是鳍式场效晶体管的隔离结构,这部分结构为介电材料,用来将每组鳍片进行电性隔离。在沉积浅沟槽隔离材料后,进一步应用化学机械抛光处理使得工作件的顶表面变得平坦,同时使得硬遮罩层暴露出来。

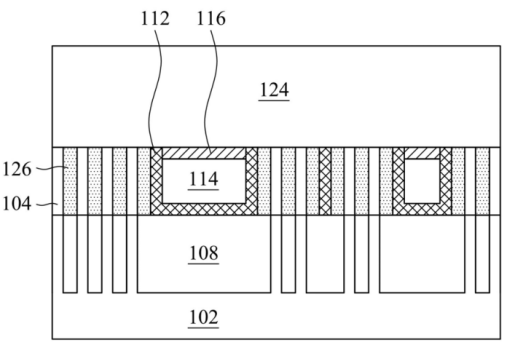

如上图,为沿着栅极间隔物展示的鳍式场效晶体管装置,栅极的侧壁间隔物由上部间隔物124和下部间隔物126组成,分别位于栅极的上部和下部。下部间隔物的顶部与鳍片结构的顶表面相挨着,二者的顶表面处于共平面。因此,上部间隔物的底表面同样与鳍片结构的顶表面处于共平面。此外,在多个鳍片群集之间的空间中,上部间隔物的底部直接接触了部分第二介电层116以及第一介电层112,由此形成了介电质堆叠。

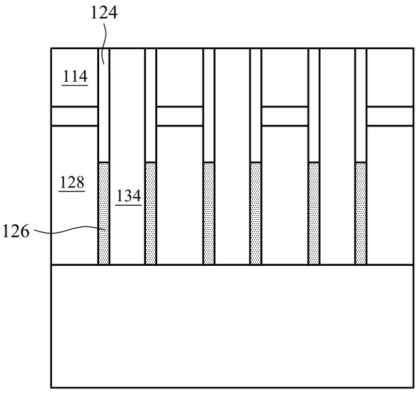

如上图,为鳍式场效晶体管装置的结构示意图,可以看到栅极装置134包括了侧壁间隔物,其具有上部间隔物及下部间隔物,并且上侧壁间隔物及下侧壁间隔物两者皆将栅极装置与源极和漏极区128进行了隔离。

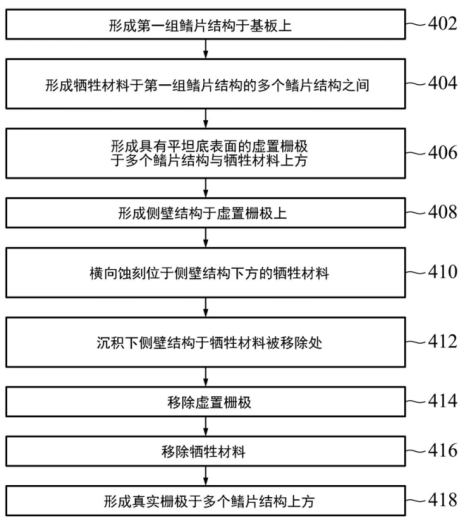

最后,我们可以看到,上图为这种具有改善节距微缩化的鳍式场效晶体管结构的制备方法流程图。首先,在基板上形成第一组鳍片,鳍片的结构可由图案化工艺处理,通过光刻的方式形成。并在多个鳍片结构之间设置牺牲材料,牺牲材料可选择氮化硅或者硅化锗,这些材料比较容易契入多个鳍片结构之间的空间。

其次,在鳍片结构和牺牲材料的上方设置虚置栅极,并在其上形成侧壁结构。通过横向蚀刻牺牲材料来在侧壁间隔物下方留下孔洞,孔洞的厚度大于侧壁结构,约为5~15纳米。最后,将虚置栅极移除并在鳍片结构上方形成真实栅极,从而得到更高结构的鳍片结构并得到更加微缩化的结构。

以上就是台积电发明的通过改进鳍片结构而完成芯片微缩化的集成电路装置方案,该方案通过新型的鳍片结构以及利用介电质的堆叠,实现了更高尺寸的鳍片结构。不仅有利于提高芯片的性能,同时也有利于实现芯片的微缩化。