【嘉勤点评】台积电发明的具有凹进结构的半导体器件方案,通过凹进结构来将栅极结构进行互连,相比于传统方案而言更加节省片上空间,达到减小标准单元的单元高度和宽度来减小芯片面积的目的,同时也不会受到现有技术遇到问题的影响。

集微网消息,目前,半导体集成电路(IC)行业经历了指数级增长。在半导体IC设计中,标准单元方法通常用于芯片上半导体器件的设计上。

这种方法主要使用标准单元作为特定功能的抽象表示,从而将数百万或数十亿个器件集成在单个芯片上。随着半导体行业生产力的提高和IC规模的持续缩小,越来越多的器件被集成到单个芯片中。

目前的主流技术是按比例缩小芯片尺寸以提高生产效率,而为进一步提高IC的微缩化和集成化,台积电在2021年2月26日申请了一项名为“半导体器件及其制造方法”的发明专利(申请号:202110216619.6),申请人为台湾积体电路制造股份有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项方案吧。

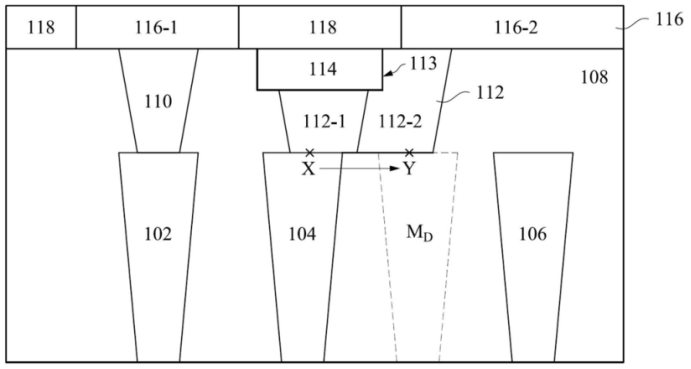

如上图,为该专利中发明的具有凹进互连结构的半导体器件的截面图,这种半导体可以为平面互补金属氧化物半导体场效应晶体管(NMOSFET)、基于鳍的场效应晶体管(FinFET)、纳米片场效应晶体管、纳米线场效应晶体管等。

上图所示半导体100主要包括第一栅极结构102、第二栅极结构104和第三栅极结构106,这些栅极结构均形成在有源区上并且嵌入在介电层108中,在相应的源极区域设置在栅极结构的侧面上以用作各自的晶体管。

在介电层上还包括有互连结构116,为了让半导体器件可以正常工作,每个栅极结构电耦接至多个后端制程(BEOL)结构。例如,栅极结构电耦接至互连结构的互连结构116-1,栅极结构电耦接到互连结构的互连结构116-2,这两个互连结构沿着相同的信号轨道形成并通过介电结构118彼此分离。

从上图的结构中可以看到,栅极结构还与不垂直对准的互连结构112相连接。与116不同的是,互连结构112的结构为凹凸组合,分为凹进112-1和未凹进112-2两部分。凹进部分112-1的位置形成了通孔结构,可以将栅极结构连接到M0层(直接在栅极结构的上方形成的包含这种互连结构的层被称为“M0”层)中的互连结构。

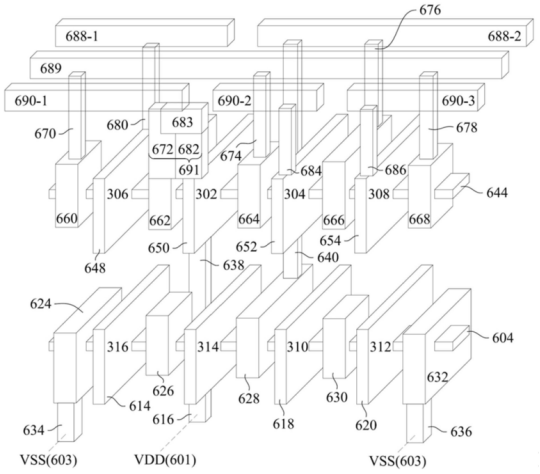

如上图,为包括凹进互连结构的半导体器件的立体图,从中可以更加直观地看到这种凹进互连结构是如何组成的。并且,过采用这种凹进互连结构可以减小布局设计600A和600B的尺寸,同时不受布线问题的影响。例如,标准单元的单元宽度和单元高度分别可以减小至与相对较少数量的栅极结构和信号轨道成比例的程度。

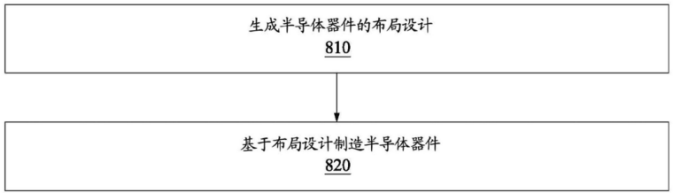

如上图,为这种半导体器件的制作工艺流程图,该工艺在开展具体的制造过程时,首先要生成半导体器件的布局设计图,布局设计通常由处理器执行合成工具而自动生成,这种综合工具可以将逻辑设计转换为相应的布局设计,并以图形数据库系统(GDSII)文件格式呈现布局设计。

其次,基于布局设计就可以进行半导体器件的制造,例如通过掩膜的方式来制造半导体器件,在制造的过程中,不断地在衬底上形成上述构成半导体器件的各个部分,从而完成半导体器件的制作流程。

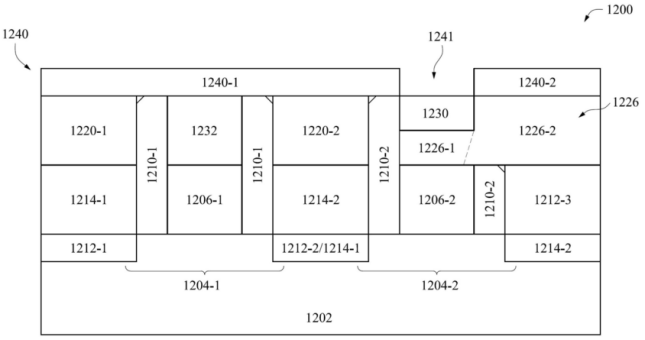

最后,如上图,为半导体器件制造完成后的截面示意图,在形成相应的M0轨道部分124-1和1240-2后,切口图案1241和介电凹进结构1230垂直对准。这样,栅极结构1206-2可以通过凹进的VD+VG 1226电耦接到M0轨道部分1240-2,同时与M0轨道部分1240-1电隔离,由此完成半导体器件的整体制作工艺。

以上就是台积电发明的具有凹进结构的半导体器件方案,该方案通过凹进结构来将栅极结构进行互连,相比于传统方案而言更加节省片上空间,达到减小标准单元的单元高度和宽度来减小芯片的面积的目的,同时也不会受到现有技术遇到问题的影响。