在智驾域控制器内,AI芯片是当之无愧的霸道总裁,直接决定了智驾域控制器的武功高低,间接反映了主机厂的地位尊卑。而可以培养霸道总裁的英伟达、地平线、高通、Mobileye等技校也是开足了马力,不断刷新霸道总裁的技能包,时刻准备为分久必合的混战局面画上一个句号。

但在已量产或即将量产的智驾域控制器中,不管是量产夭折(带L3功能的配置)Audi A8上搭载的zFAS,还是已量产小鹏P7上搭载的IPU03,在智驾域控制器PCB版上的远郊之处,我们总能发现AI芯片身边还有一颗其貌不扬但举止非凡的MCU,像极了霸道总裁身边那个平凡的灰姑娘,并直接决定了智驾域控制器的文化水平高低。

细究之下,这颗MCU承担的职责全是功能安全等级要求高的重任,有用它来承担自动驾驶功能激活期间的车辆控制功能,有用它来承担自动驾驶系统故障时的降级策略,有用它来检测智驾域内系统的运行状态,有用它来承担与车内通讯的网关功能……。

这类MCU民间喜欢称之为安全核,具有常人所不具有一些安全特性,使其默默充当自动驾驶安全的守门员。自动驾驶黑话圈第十九期,笔者就带领大家一起欣赏这颗MCU具有了什么样的特性,才让其可以承担如此重要的安全使命。

安全机制

在功能安全的圣经ISO26262中,违背硬件安全初心的故障类型包括:单点故障、残余故障、两点故障、潜伏故障和多点故障等。

单点故障:无法被安全机制探测到的硬件故障,一旦发生,将直接违背硬件安全初心;

残余故障:硬件部分设计有安全机制,但安全机制无法做到100%诊断覆盖,残余故障便是未被诊断覆盖的那部分漏网之鱼,一旦发生,也将直接违背硬件安全初心;

两点故障:某个故障,平时人畜无害,但当钟意的姑娘出现在球场边,才会变成大杀四方的詹姆斯。由于没有安全机制,也将直接违背硬件安全初心;

多点故障:一家子(>2)团聚时才生产生共鸣,引起硬件的故障,具有违背安全初心的风险;

潜伏故障:多点故障中未被安全机制诊断覆盖到的故障,具有违背安全初心的风险。

要想减少故障,提高硬件的功能安全等级,增加安全机制是一种行之有效的方案。安全机制用于探测故障,控制/避免失效,来维持预期功能,保持安全状态。但是针对硬件某一部分增加了安全机制,并不代表一定安全,安全机制也有一个诊断覆盖率的问题。

诊断覆盖率是指在硬件要素失效率中,元器件失效率可以被安全机制诊断出来 的百分比,典型值有60%、 90%和 99%。诊断覆盖率可通过硬件可能发生的残余故障或者是潜伏故障进行评估。

在《ISO26262-5 2018 产品开发:硬件层面》的附录D中,列举了处理器采用不同安全机制对应的诊断覆盖率。而在硬件冗余可采用的安全机制里,双核锁步、非对称冗余、编码计算作为三种典型的高诊断覆盖率技术被推荐使用,也是安全核在硬件层面主要采用的技术。

一、双核锁步

MCU(Microcontroller Unit,微控制单元)是一种将CPU、寄存器、存储器、定时器、中断系统、输入输出接口等整合在单一芯片上的芯片级计算机,是传统汽车分布式电子电器架构下各控制器里的大脑。而在MCU的组成部分中,又属CPU最为核心。CPU(Central Process Unit,中央处理器)是一种主要由ALU(Arithmetic and Logic Unit,运算单元)、CU(Control Unit,控制单元)、Register(寄存器)、Cache(高速缓存器)等组成的高性能通用控制器。

CPU在工作过程中,由于芯片老化、电磁干扰、时钟漂移、静电放电、电路短路等影响,CPU也有较大可能性发生行为不可控的故障。而为了解决MCU中单个CPU出现故障,导致整个系统失效的问题,诞生了CPU的硬件冗余技术—双核锁步。

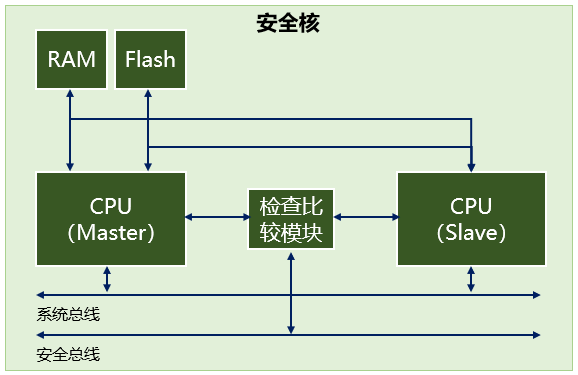

在双核锁步技术中,采用两个完全一致的CPU,一个作为Master,一个作为Slave。CPU Master通过总线访问RAM和Flash,并将从RAM和Flash中获取的指令和数据通过总线送入内部执行。CPU Slave则比较懒,直接在总线上获取CPU Master取出来的指令和数据执行。这样一来,流水线一致、指令集一致的两个完全一样的CPU在相同时钟周期内执行相同的指令。

CPU Master和CPU Slave指令执行的结果,包括数据、地址和控制结果。通过总线均发送到比较逻辑模块,比较逻辑模块检查两者之间输出的数据、地址和控制结果的一致性。检测到任何信号不一致时,比较逻辑模块输出错误标志信息,系统基于错误标志信息采取不同的应对措施。需要注意的是,双核锁步模式下,只能判定CPU出现故障,但无法确定是CPU Master还是CPU Slave。

相比使用两个独立MCU进行冗余设计,单个MCU的双核冗余设计,具有如下优势:

(1)硬件元器件数量及连接大幅减少,进一步提高了硬件的可靠性;

(2)电路板复杂度降低、尺寸减少,使得电磁干扰能力提高、电池辐射能力降低;

(3)真正从源头上进行故障检测,并且在第一次出现时即被检测到,大大提高故障诊断能力;

(4)CPU Master和CPU Slave不需要通信和数据同步,降低了软件验证的复杂度。

二、延迟锁步

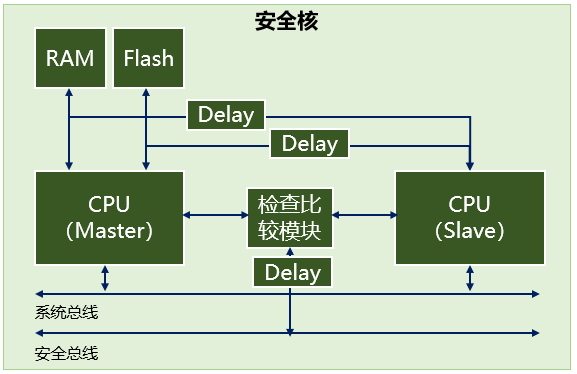

在双核锁步中,存在这样一种可能性,一个噪声脉冲以相同的方式在同一个时间点冲击CPU Master和CPU Slave,结果两个CPU发生了同样的故障,产生了相同的错误结果送入比较逻辑模块。但比较逻辑模块比较结果相同后,会认为这时没有错误,不会发出错误标志信息。

为了减少上述可能性发生的概率,延迟锁步模式诞生。CPU Master执行指令的数据、地址和控制结果延迟N个周期送入比较检查模块,同时将相同的指令延迟N个周期送入CPU Slave。这样就可保证在每个周期送入比较检查模块的CPU Master和CPU Slave结果,都是间隔N个周期但执行相同指令后的结果。

延迟锁步可以预防在同一个时间点,CPU Master和CPU Slave发生同样的错误。但由于故障检测滞后N个周期,对于实时的自动驾驶控制来说,是否可以接受,是需要功能安全团队认真评估的。

三、非对称冗余

不管是双核冗余还是延迟冗余,CPU Master和CPU Slave是完全相同的两个CPU。这意味着你出生具有的天生缺陷,我也会有。你面对无能为力的场景,我也无能为力。而为了降低两个相同CPU发生共因故障和同类故障的概率,非对称冗余技术诞生。

在非对称冗余中,CPU Slave为一个不同于CPU Master的专用内核,且性能一般要比CPU Master弱一点,两核之间通过一个专用接口紧密耦合。在CPU Master执行的关键任务过程中,CPU Slave通过专用接口选择性的复制部分关键任务同步执行,并将内部执行结果与CPU Master输入的外部执行结果进行比较。

非对称冗余中,CPU Master和CPU Slave通过专用接口相连,可以降低系统复杂性,缩短错误检测延迟。不同规格的CPU还可以改善相同硬件带来的共因故障和同类故障。但是由于CPU Slave性能比较弱,没法同步执行CPU Master的所有任务,如何从CPU Master执行的关键任务中挑选出最高安全要求的任务,是一个技术活。

四、总结

双核锁步/延迟锁步/非对称冗余架构使得CPU自检独立于应用软件,不需要专门的指令集进行自检。实际运行的软件指令在每个时钟周期都会进行比较,不会额外占用CPU的资源。但是双核冗余架不对内存和总线故障进行检测,如果想进一步提高MCU的整体功能安全等级,减少共模失效的概率,还需要同步采取如下方法。

(1)对RAM和Flash存储的指令和数据引入ECC保护,检测和纠正RAM和Flash中的数据错误;

(2)对总线进行安全保护,可将总线分为系统总线和安全总线。指令数据通过系统总线传输,功能安全数据通过安全总线传输;

(3)CPU Master和CPU Slave在布局上要满足设定界限及互斥距离,以使他们在物理上尽量分开;

(4)CPU Master和CPU Slave所用时钟树要彼此分开,避免共用时钟路径和时钟缓冲器;

(5)绕线时,设置绕线保护带,防止一个核的互连线走到另一个核所在的区域,从而避免信号串扰带来的影响。

主流安全核

一、英飞凌AURIX系列

英飞凌AURIX系列可谓是智驾域控制器里最常见的灰姑娘,成名之战便是应用在Audi A8域控制器zFAS上,与AI芯片一同助力Audi A8 L3自动驾驶功能的实现。

AURIX第三代最高端产品TC39X与TTTech Auto合作开发,设计之初便瞄准了自动驾驶领域,支持高达ASIL-D/SIL3的功能安全要求。TC39X具有6个频率高达300MHz的TriCore,带ECC保护的16MB闪存,可编程HSM,支持时钟延迟的多样化锁步核心。

二、恩智浦S32系列

恩智浦在针对智驾域的安全核开发方面颇显被动,前几代产品不仅处处透着传统MCU的气息,还处处想着一“芯”多用,2020年发布的S32G,既定位于车载中央网关芯片,同时也定位于自动驾驶芯片。两个应用场景差异如此之大的领域,用一款芯片打天下,可谓艺高人胆大。

但好在后续产品及时跟进,发布了具有高功能安全等级,高信息安全等级的S32K3系列MCU。S32K3系列MCU基于Arm Cortex-M7核心打造,共拥有12种芯片配置,支持ASIL D功能安全等级。

S32K3系列带有锁步功能的芯片有单核、双核配置。其中单核锁步配置拥有1个Cortex-M7锁步核心,频率为160MHz;双核锁步配置拥有1个Cortex-M7锁步核心和1个Cortex-M7核心,频率为240MHz。可编程HSE和ECC保护也成为可选配置。

全文小结

本文主要针对CPU的硬件冗余技术做了简单介绍,但可以想象的是,一个优秀的灰姑娘,达到如此高的功能安全等级,在软件冗余、信息冗余方面也必定将有不凡的修炼,后续文章我们再一一详解。

作者 | 11号线人

原文: 十一号组织