作者:西南交通大学研究生导师邸志雄博士。

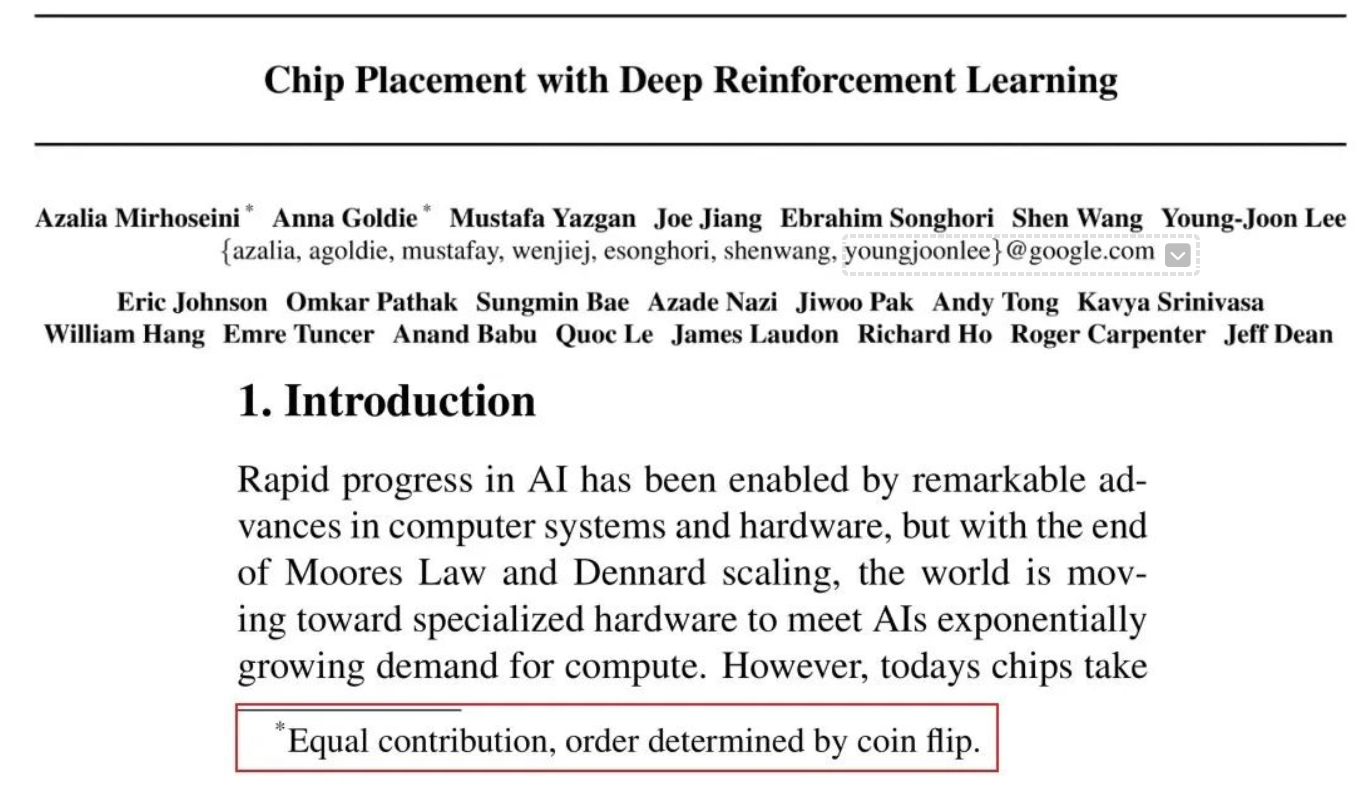

四月初,谷歌大脑团队使用 AI 进行芯片布局的一篇相关研究论文《Chip Placement with Deep Reinforcement Learning》在 ArXiv 上公布。在 Azalia Mirhoseini 这篇 ArXiv 论文中,她和谷歌高级软件工程师 Anna Goldie 表示,对芯片设计进行了足够长时间的学习之后,团队开发的算法可在不到 24 小时的时间内为谷歌 TPU 完成设计,且在功耗、性能、面积都超过了人类专家数周的设计成果。她们认为,理想情况下,新设计出的芯片应该能够很好地满足当今 AI 算法的需求,“如果 AI 能够缩短芯片的设计周期,在硬件与 AI 算法之间建立共生关系,会进一步推动彼此的进步”。

这篇论文发表之后,业界为之震动。这是Azalia本人汇总了美国科技媒体的反馈。

在国内,包括机器之心、智东西、MIT科技评论等知名媒体在都迅速发表了此项成果的评论。前期笔者也对这篇论文的背景做了简单的汇总和整理,并发表在西电潘伟涛老师的微信公众号“网络交换FPGA”上,也被“半导体行业观察”等多个公众号转载。而本篇文章主要对《Chip Placement with Deep Reinforcement Learning》做一个简要的技术解读。

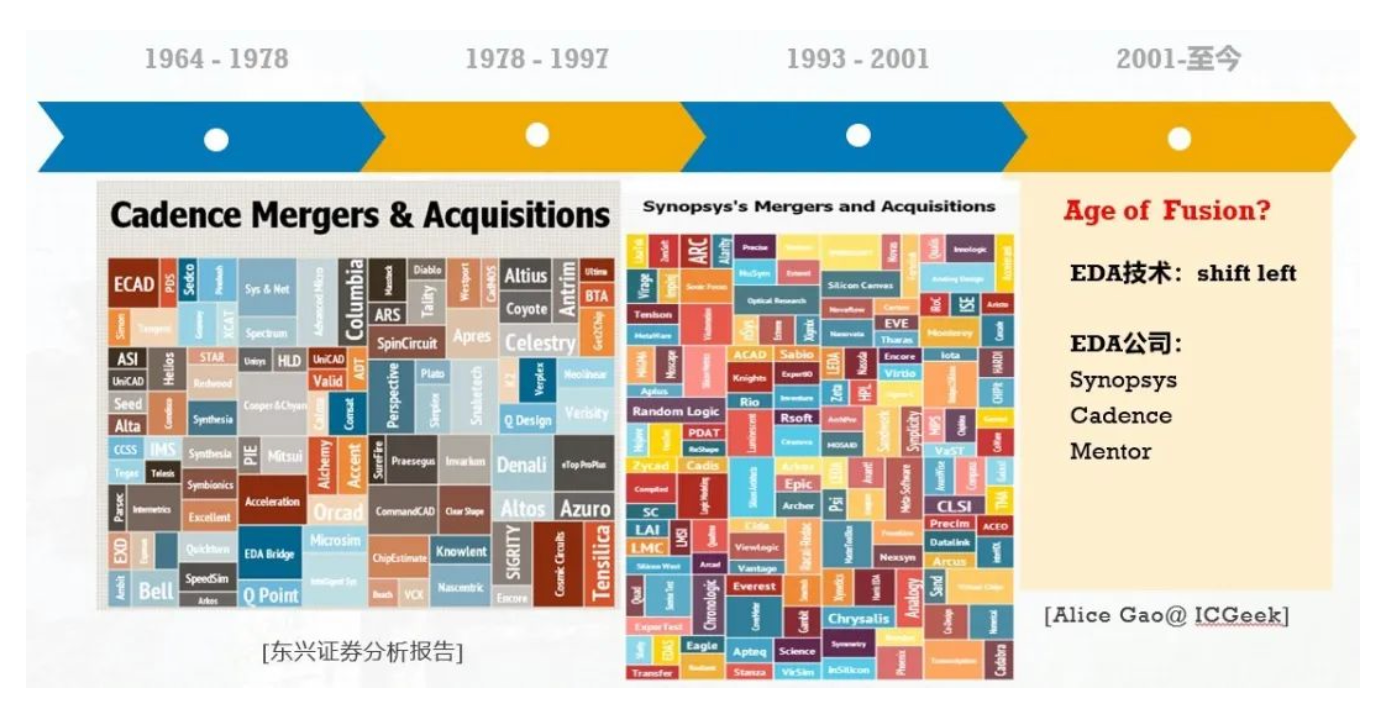

大背景:EDA发展史

1.1 EDA发展史的三个时代

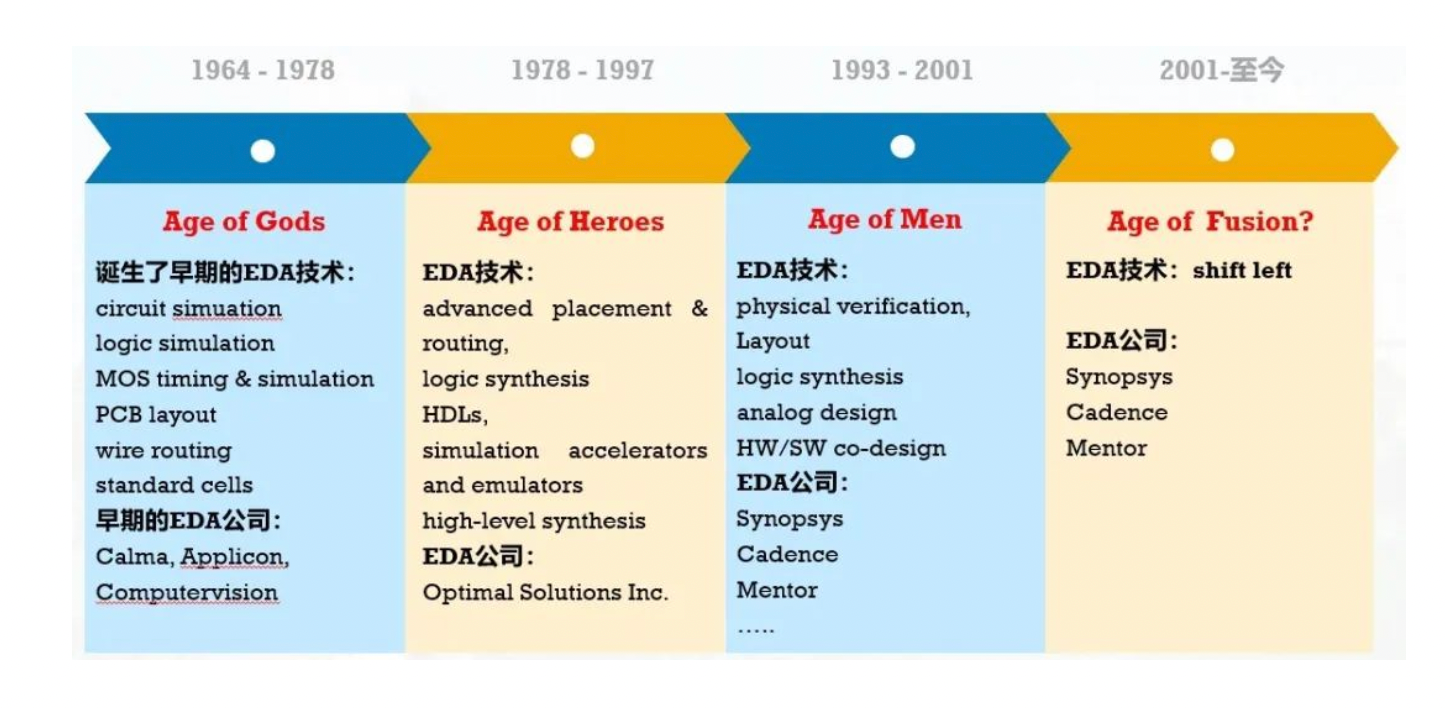

2003年,IEEE Design & Test of Computers 刊出了《EDA的潮流》这篇文章,文章将EDA的发展史总结为3个时代。

1964年到1978年,为神的时代。“神”开天辟地,开创了EDA领域,诞生了早期的EDA技术,包括circuit simuation, logic simulation, MOS timing and simulation, PCB layout, wire routing and standard cells。同时也诞生了第一批EDA公司,如Calma, Applicon, and Computervision。

“英雄时代”从1978年持续到1997年。这是“一个充满活力的创造力和扩展的时期,它见证了高级布局和布线、逻辑综合、HDLs、仿真加速器和emulator以及高级综合的诞生,奠定了现代EDA方法学的基础理论。诞生了Synopsys公司的前身Optimal Solution Inc。

1993-2001年,是人的时代,在这个时代“事情开始放缓”。互联网开始广泛使用,工程师们开始设计芯片上的系统。在物理验证、布局、逻辑合成、模拟设计和软硬件协同设计等方面的技术进步。文章指出,“人类的时代”通常会退化为另一个“神的时代”,历史的循环会重新开始。文章中也问道,我们能不能培育另一个“英雄时代”?

2001年以后,我简单做了一个不太准确的定义,将其归纳为“融合的时代”。这个阶段EDA技术细节和数据逐渐开始尝试共享与融合。首先,软硬件的设计与验证环节不再是独立的环节,而是协同推进。其次,各个环节拉通引擎,共享数据模型,提升了环节间的一致性和高并发优化的可行性,极大降低了环节间复杂的数据交互所造成的资源浪费,能够为设计工程师提供更丰富的接口和更具有灵活性延展性的流程构建方式,从而综合提升了从综合到签核的整体工程效能[引用自:ICGeeK]。EDA 公司也逐渐被并购为现在三巨头的格局,挑战者逐渐减少。

未来,有可能是AI的时代吗?

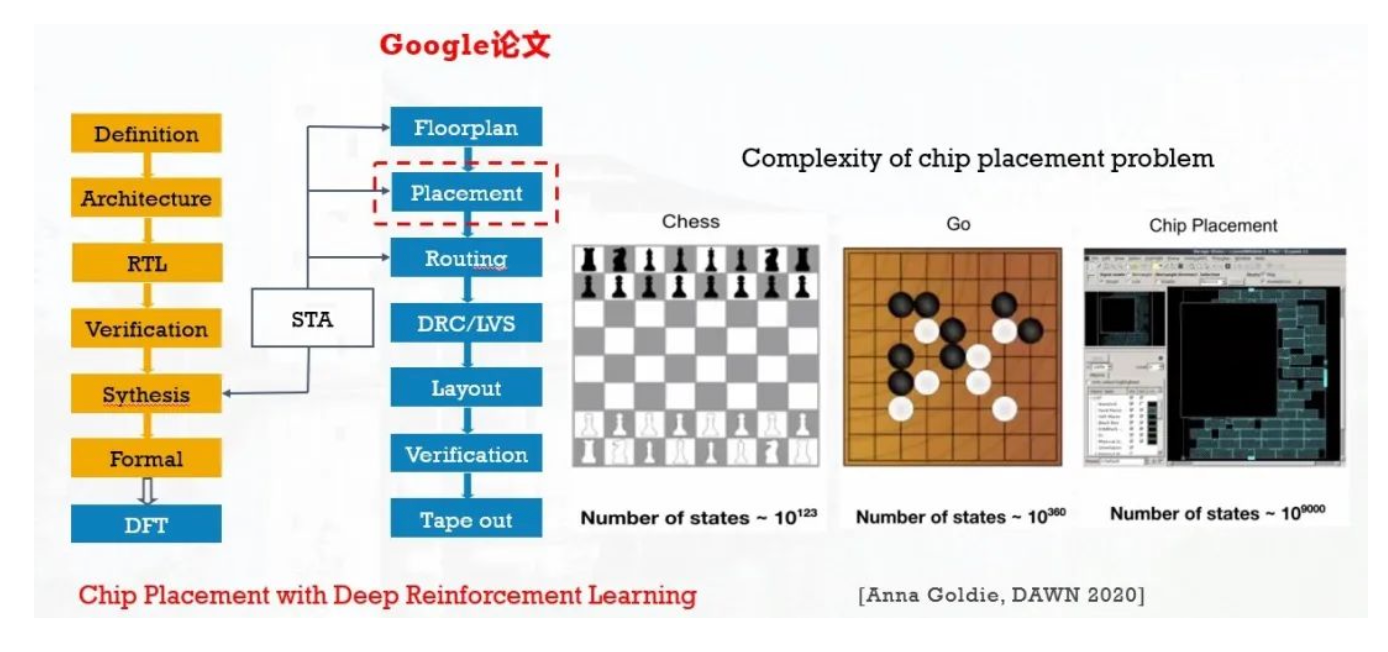

Google想解决EDA中的什么问题?

Google提出了一种基于DRL的芯片布局方法,这是芯片设计过程中最复杂,最耗时的阶段之一。尽管对此问题进行了数十年的研究,人类专家仍然有必要使用现有的放置工具进行数周的迭代,以产生满足多方面设计标准的解决方案。问题的复杂性来自网表的大小(数百万到数十亿个节点),放置这些表图的网格的粒度以及计算真实目标指标所需的高昂成本。即使在将问题分解为更易于管理的子问题(例如,将节点分组为几千个群集并减少网格的粒度)之后,状态空间仍比最近成功的基于强化学习的方法所能处理的问题大几个数量级。

Google的核心工作

众所周知,Google在强化学习领域做出了很多声誉卓著的工作,本论文作者Azalia也在前期发表了多计算引擎任务分配方面的论文,这次将强化学习应用于芯片布局阶段。主要工作包括:

① 提出了一种基于Deep Reinforcement Learning芯片布局方法,这是芯片设计过程中最复杂,最耗时的阶段之一。(需要人工干预最多,最依赖工作经验的阶段)。

② 完成macro和标准单元的布局,以优化功耗,性能和面积(PPA),同时遵守对布局密度和布线拥塞的约束。

③ 采用端到端的方法,可以产生媲美或优于人类专家产生的布局,会在6小时内生成芯片布局。

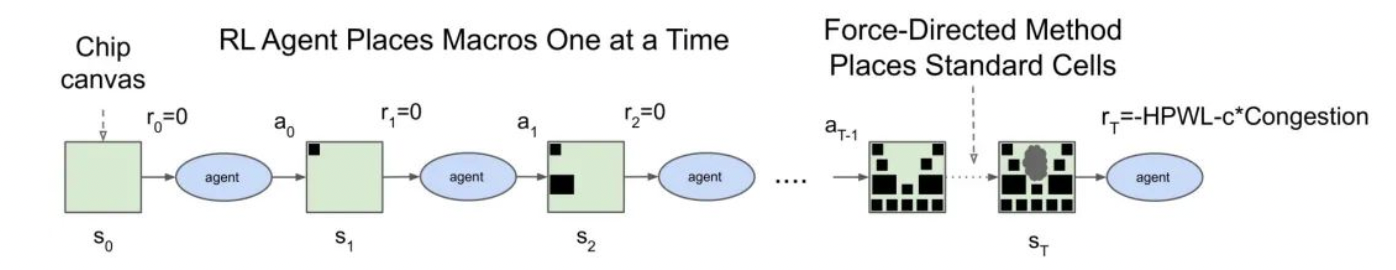

3.1 采用的方案

针对强化学习的四个关键要素,本文做了如下映射:

① s(state):包含网表,节点特征, 边特征, 线网分配, 总线数, Macro, 标准单元

② state transition:布局方案调整

③ r(reward):总线长和拥塞加权和、density

④ a(action):当前Macro在布局中放置的概分布

强化学习中非常重要的是奖励函数的设置,因为它会决定强化学习算法的收敛速度和程度。reward如果构建比较差,RL就很难实现预期的结果,而且容易出现作弊的情况。本文采用总线长和拥塞的加权总和作为reward,其中权重可用于探索两个指标之间的权衡。同时,将拥塞视为软约束,将density视为硬约束,即布局过程中必须满足density的要求。强化学习策略需要大量训练数据才能有效学习,因此至关重要的是要快速评估奖励功能,理想情况下可以在几毫秒内运行。为了更有效,这些近似的奖励功能还必须与真实奖励正相关。因此,采用总线长和拥塞作为奖励,不仅能够快速获得,而且能够反映PPA。

① 在具体设计中,本文采用了半周线长(HPWL)来估算线长,这是最常用的线长近似值。

② 为了选择Macro的放置顺序,按大小降序对宏进行排序,并使用拓扑排序打破平局。通过首先放置较大的Macro,我们减少了以后的Macro没有可行放置的可能性。

③ 为了放置标准单元,使用与经典的force-directed力导向方法相似的方法(Shahookar&Mazumder,1991)。将网表表示为一个弹簧系统,该弹簧根据权重x距离公式对每个节点施加力,从而使紧密连接的节点彼此吸引。还引入了重叠节点之间的排斥力以降低布局密度。

④ 为了便于商业EDA工具评估布局质量,论文采用了最后也补充了布局合法化步骤。

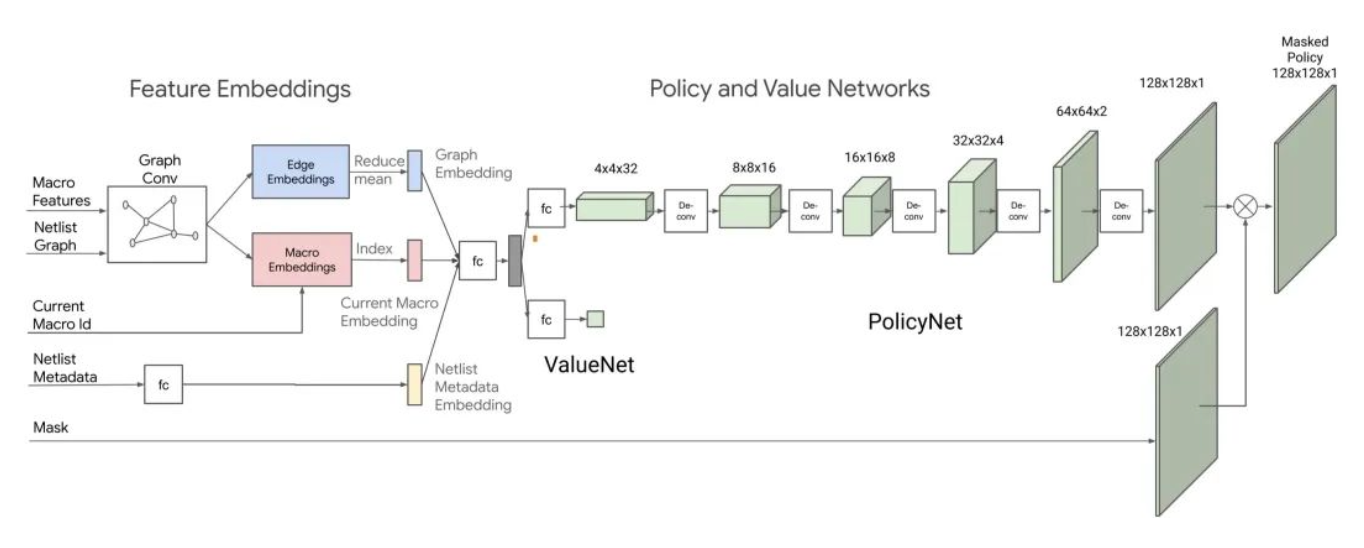

整体的网络架构主要分为两个层次.

首先,本文设计了一种新颖的图神经网络架构,该架构嵌入了有关网表的信息。通过串联节点特征来创建每个节点的矢量表示。节点特征包括节点类型,宽度,高度以及坐标。GCN还将节点邻接信息作为输入传递。GCN的作用是将有关大图内节点类型和连通性的信息提炼成可用于下游任务的低维向量表示。最近几年,也陆续看到GCN出现在了一些EDA领域的论文中。图神经网络比较适合处理电路网表这种非欧几里得空间的数据,但是也有泛化能力弱等缺点。我们常见的人脸检测等,都是欧几里得空间,所以一般采用CNN等网络架构。

其次,本文提出了一种训练神经网络架构的方法,该结构能够预测新网表上的奖励,其最终目标是使用这种架构作为策略网络的编码器层。在训练中,采用了5个block,每个2000种布局,创建了一个10,000个芯片位置的数据集,其中输入是与给定位置相关的状态,而标签是该位置(线长和拥塞)的奖励。为了处理与不同的行和列选择相对应的不同网格大小,将网格大小设置为128x128,并对小于128行和列的网格大小遮盖未使用的L形部分。

3.2 实验结果

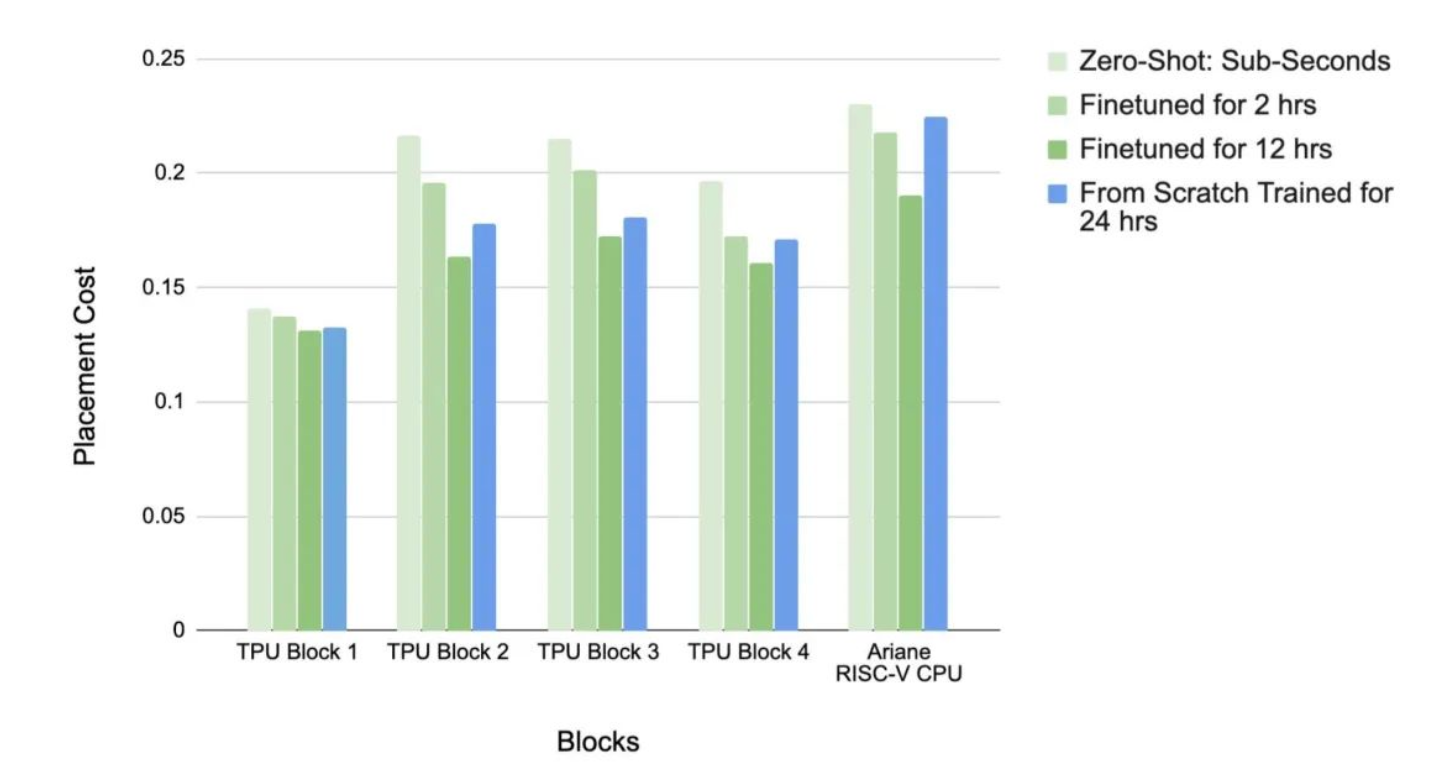

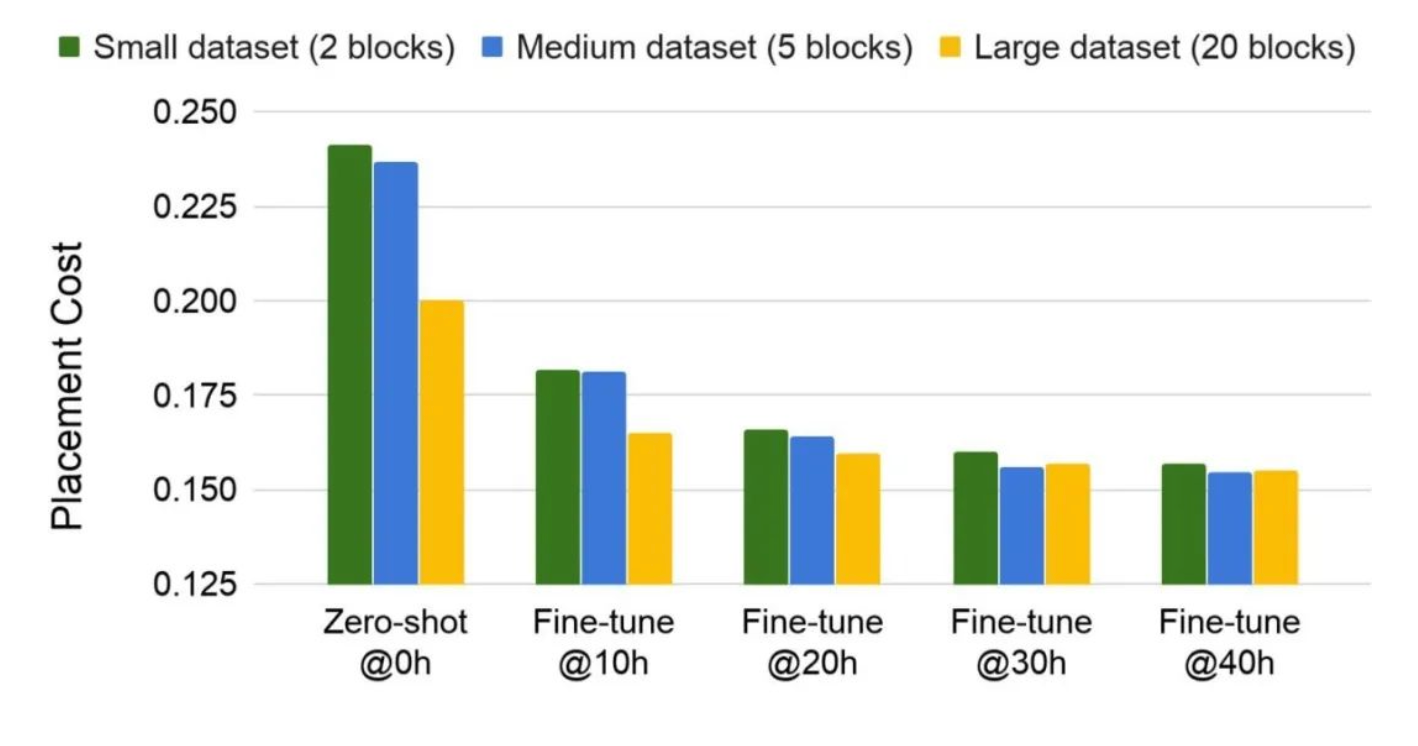

论文将没有经过精细调优的、经过预先训练的策略网络生成的布局位置称为zero-shot布局。这样的布局可以在不到一秒钟的时间内生成,因为它只需要预先训练的策略网络的单个推理步骤即可。然后可以通过优化策略网络来进一步优化布局质量。这样能够灵活地使用预先训练的权重或进一步微调这些权重以针对特定芯片网表的属性进行优化。

通过上述实验结果可以看到,从头开始训练的策略网络需要花费更长的时间才能收敛,即使在24小时之后,结果也要比经过精调的策略网络在12小时之后达到的结果更差,这表明训练形成的网络权重能够实现在较短的时间内为新设计提供高质量的布局的目标。预先训练的策略网络始终优于从零开始训练的策略网络,这表明从离线训练数据中学习的有效性。随着增大训练集数据,能够加快训练过程并更快地产生更高质量的结果。

本图为Ariane RISC-V CPU的布局结果。左侧zero-shot结果,右侧显示了经过微调的布局结果。Zero-shot将标准单元放在中心,这已经非常接近人工手动布局的结果。在微调之后,macro布局变得更规则,并且中心的标准单元区域变得不太拥挤,congestion也大幅减少。同样的结果,还可以在下图中看到与人工做布局的对比,本文算法布局结果要更紧凑一些:

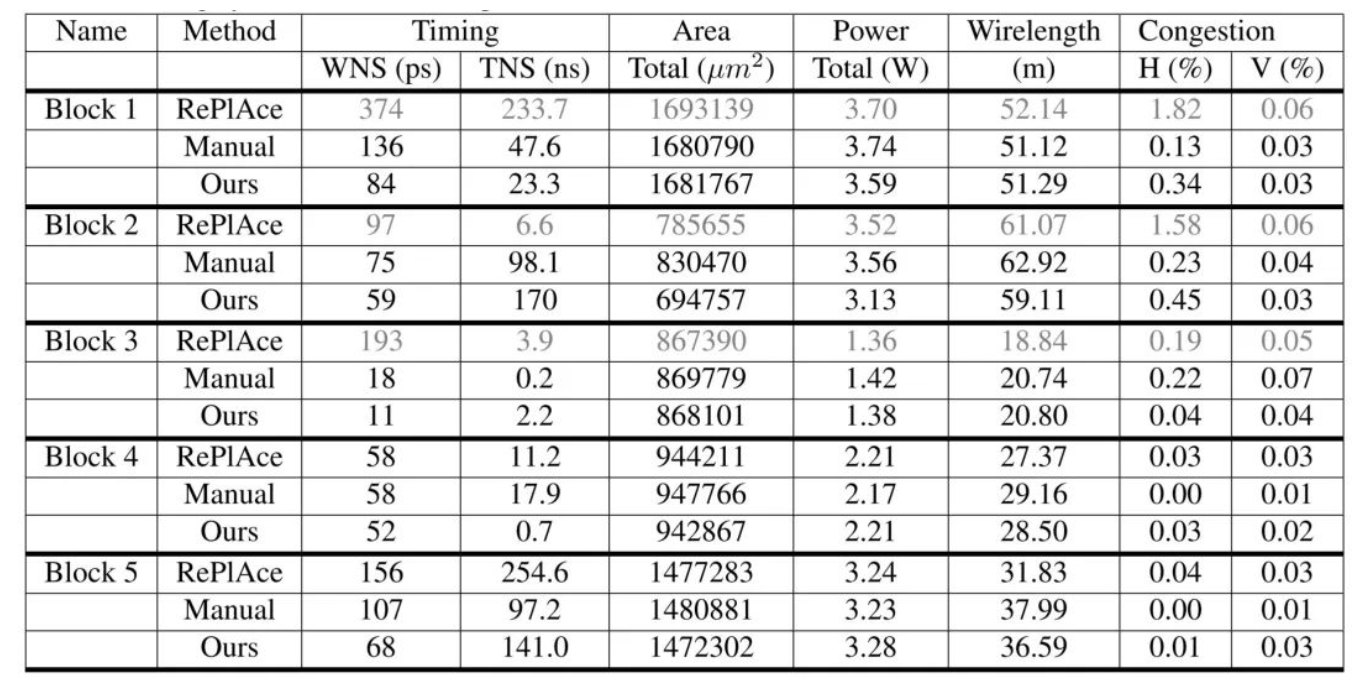

为了实验结果对比更为严谨和公平,本文还与模拟退火方法和RePlAce进行了对比,如下图:

论文还与模拟退火方法进行了比较,模拟退火(SA)是一种功能强大但速度缓慢的优化方法,在EDA算法是经常被使用。本文用SA替换了RL策略网络,对SA设置了不同的参数,论文给的数据显示,SA花费18个小时才能收敛,而谷歌的方法花费不超过6个小时。如表中所示,与谷歌的方法相比,即使花费额外的时间,SA仍难以生产出高质量的布局。

论文还与RePlAce(Cheng等,2019)和手动基准的比较。手动方案由生产芯片设计团队生成,涉及了布局优化的多次迭代。在实验方案设计中,采用了商业的EDA工具输出数据作为统一的比较尺度,如总线长,时序,面积和功耗。同时采用了商用EDA工具使用该工具的默认设置来进一步优化标准单元布局。从实验结果能够看出,本文的方法拥塞感知方法可有效地生成符合设计标准的高质量布局。在计算时间方面,RePlAce在1至3.5小时内收敛,而本文结果在3至6小时内达到。

Google工作的分析

1、亮点

本文的亮点主要包括:

① 采用了端到端的结构,减少人工干预。实现一个完整的placement功能,包括摆放macro、STC,预测congestion、总线长等等。整体工作量比较大。

② 训练集非常大,共1万种布局。而且,每个block的规模也很大,包含很多macro,芯片规模基本上能够反映物理设计的实际应用需求。

③ 采用了DRL,DRL通常在游戏中有着优异的表现,但是在其他领域鲜见有成功应用案例。本文采用DRL能够达到各种指标的均衡,很不容易。

④ 在STC、wirelength、congestion等几个点上采用了简化的算法,重点设计核心网络结构;如果采用更好的算法,有可能会收到更好的性能,当然也有可能使计算时间变慢。

⑤ 采用图神经网络对电路网表进行表示。图神经网络在EDA领域应用还比较少。

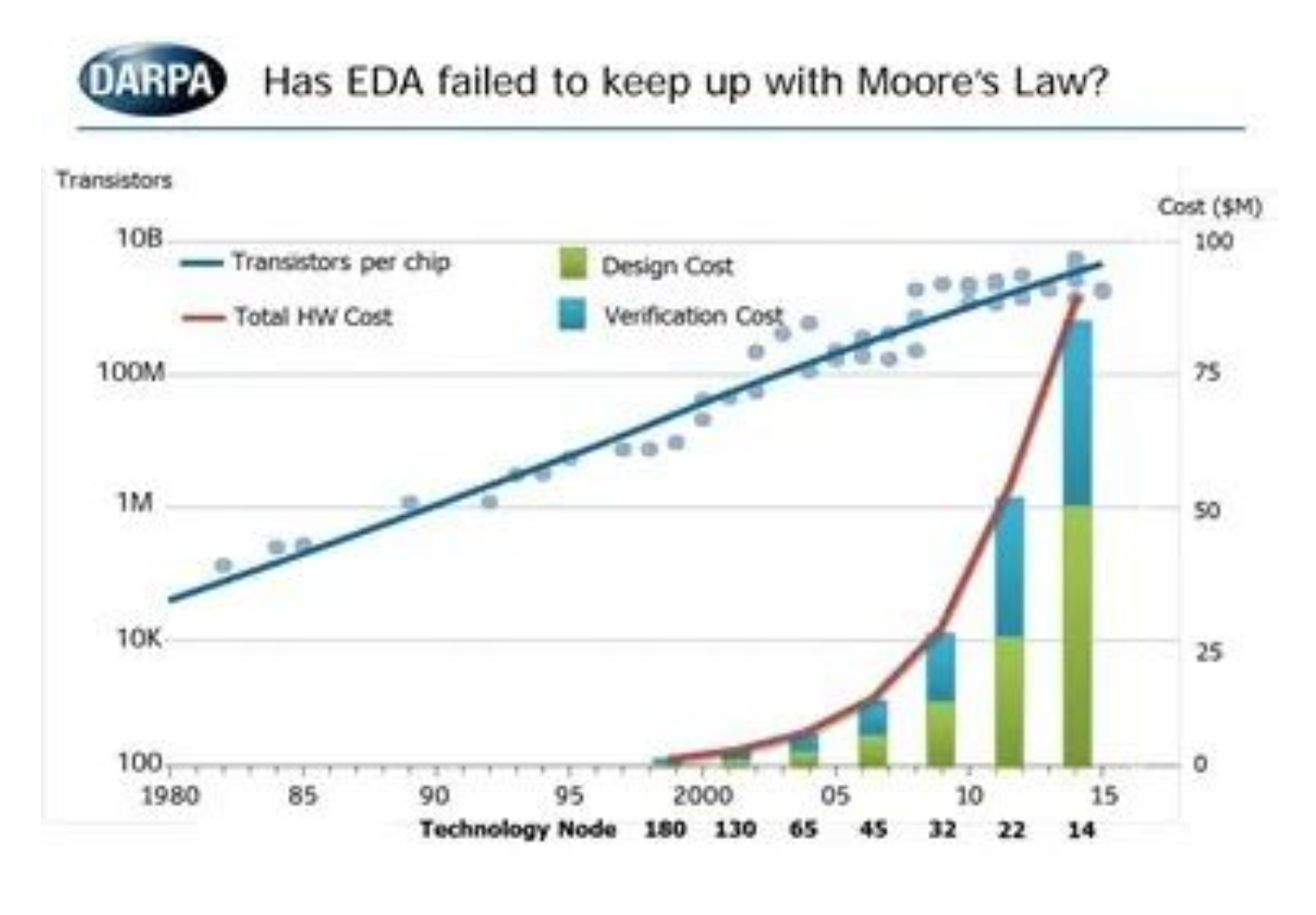

DARPA经过大量的数据调研得出当前典型的芯片设计周期为12-36个月,特别是在数字集成电路(IC)领域,先进技术节点的芯片设计极其复杂,自动化布局已经非常庞大,即使在最先进的公司也无法在短期内逾越。基于此,DARPA资助Synopsys和Cadence分别启动了POSH和IDEA项目,期望通过提出一种芯片敏捷设计平台克服芯片设计日益复杂化和成本的问题。作为DARPA IDEA计划的一部分,由加州大学圣地亚哥分校Andrew B. Kahng教授、高通、ARM领导的的OpenROAD项目于2018年6月推出,如图所示,以寻求数字芯片敏捷设计EDA工具链,期望实现24小时完成芯片设计的一种自动化解决方案。

国内也有中科院计算所包云岗教授领衔的开源芯片项目,和北京大学罗国杰教授领衔的开源EDA项目。

2、复现难点

我认为存在以下难点:

① DRL对数据量要求极大;DRL的几大缺点均无法避免。

② DRL在EDA领域鲜见成功应用的案例。

③ Macro和STC摆放位置解空间大。尤其是macro的摆放,人工的经验值很重要。

④ density只有0.6,导致congestion等情况比较缓和,而0.6往往是实际芯片物理设计中起步点,很难证明在实际工程中的有效性。

3、本篇文章最调皮之处

图文排版丨高璐

图文校对丨高璐

责任编辑丨潘伟涛

原文链接:网络交换FPGA

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。