【嘉勤点评】鸿海的半导体专利,通过调整多个牺牲层的锗浓度分布、多个半导体以及牺牲层的厚度分布,能够避免蚀刻牺牲层后可能发生的半导体层形状不均问题,使剩下的半导体层形状一致,具有类似的厚度及宽度。

集微网消息,鸿海近日宣布,与印度Vedanta集团携手成立合资公司,计划在当地投资制造半导体,鸿海持有合资公司四成股权。据悉该半导体厂已进入选址阶段。

随着集成电路技术朝着更小的技术节点发展,已经发展出多闸极元件,例如:全环绕闸极场效晶体管(GAAFET)。相较于平面晶体管,GAAFET能够更好地控制通道,并能够降低短通道效应。然而,制造GAAFET的蚀刻工艺可能会造成通道发生形状不均的问题,从而对其性能造成不利影响。

为此,鸿海于2021年10月8日申请了一项名为“半导体结构的制作方法”的发明专利(申请号: 202111170622.5),申请人为鸿海精密工业股份有限公司。

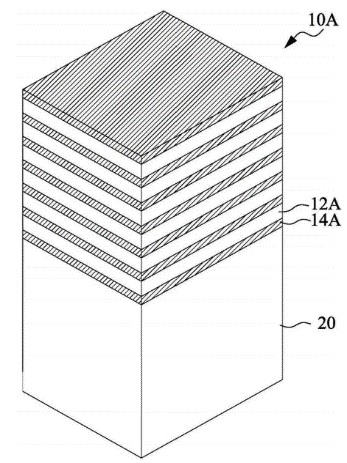

半导体制作过程结构示意图1

图1为本发明提出的半导体制作过程结构示意图1,首先形成多层堆叠10A于基板20上,多层堆叠包括交替堆叠的复数个半导体层12A和复数个牺牲层14A。多层堆叠的形成方式如下:首先在基板上形成第一牺牲层,其上形成形成第一半导体层,然后再形成第二牺牲层于第一半导体层上,其中第二牺牲层的锗浓度低于第一牺牲层的锗浓度。重复进行上述操作,可形成锗浓度由下往上递减的这些牺牲层。多层堆叠中的各层具有小的厚度,例如在约5nm至约30nm范围内。在多层堆叠的形成方式中第二半导体层的厚度大于第一半导体层的厚度,因此可形成厚度由下往上递增的半导体层。

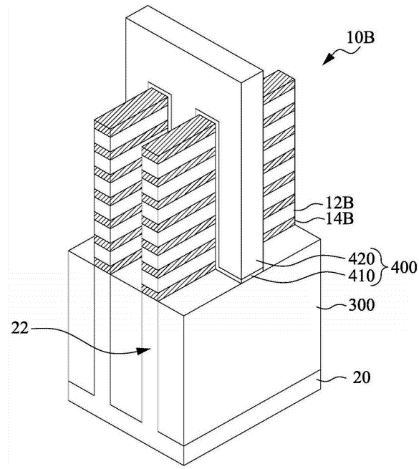

半导体制作过程结构示意图2

然后对多层堆叠及基板进行图案化,形成堆叠结构10B及鳍片22。堆叠结构包括复数个半导体层12B和复数个牺牲层14B。鳍片为在基板中图案化的半导体带。半导体层12B及牺牲层14B分别包括半导体层12A及牺牲层14A的剩余部分。再形成浅沟槽隔离区域 (STI)300于基板上及相邻鳍片间。STI区域围绕鳍片的至少一部分,使堆叠结构的至少一部分自相邻的STI区域突出。之后形成虚拟闸极结构400于堆叠结构上。虚拟闸极结构包括虚拟介电层410及虚拟闸极420。虚拟介电层全面覆盖堆叠结构及STI区域,其上形成图案化屏蔽于虚拟闸极层上,将图案化屏蔽的图案转移至虚拟闸极层及虚拟介电层,以形成如虚拟介电层及虚拟闸极。

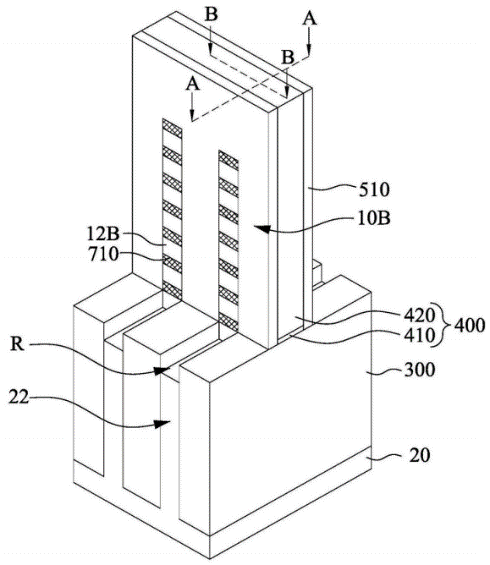

半导体制作过程结构示意图3

在虚拟闸极结构的两侧形成间隙壁510,移除未被虚拟闸极结构及间隙壁覆盖的的堆叠结构的部分且移除鳍片的上部以形成凹槽R。蚀刻堆叠结构中牺牲层14B暴露的侧壁,以在相邻的半导体层12B之间形成凹陷,其中形成内部间隔物710,可在后续蚀刻牺牲层14B的操作中,预防源极/汲极区域受损。

简而言之,鸿海的半导体专利,通过调整多个牺牲层的锗浓度分布、多个半导体以及牺牲层的厚度分布,能够避免蚀刻牺牲层后可能发生的半导体层形状不均问题,使剩下的半导体层形状一致,具有类似的厚度及宽度。

鸿海是全球3C代工领域规模最大、成长最快、评价最高的国际集团,鸿海坚持创新稳健扎实,希望透过提供全球最具竞争力的“全方位成本优势”使全人类皆能有享用3C产品所带来的便利环保生活。