本文源自知乎,链接如下:

https://www.zhihu.com/question/59057984/answer/163253727。以下是对这篇文章的几点看法。

作者为华为鲲鹏架构师夏晶晶博士。芯片设计行业内资深知名大佬级人物,在几年前就道出了国内芯片行业人才培养中的不足和缺陷。作者在知乎上发布了一个简单的独热码识别的面试题目,要求用(组合)逻辑实现,结果几百条回复的帖子里愣是没有一个正确的。虽然近几年芯片的概念比较热,但即便是在很多高校里,仍然存在着很大的误区,认为Verilog或VHDL语言是跟C、C++之类的语言是一样的软件编程语言。我非常认同夏大佬的观点,硬件描述语言的学习是建立在对硬件电路结构甚至是体系结构熟悉的基础之上的,也就是说,HDL语言是一种用来描述电路结构的语言,虽然它跟C之类的软件编程语言很像。

1、数字电路芯片的设计是有门槛的。

这几年,笔者作为高校里做IC设计的研究人员,也切身体会到了在灯塔国各种制裁下很多企业甚至是风投都开始做芯片了,但具体效果却不尽理想,比如某些企业投入数亿都没有做出来一款能用的商业芯片。这里面虽然有还需要数代产品结合市场反馈不断迭代的因素,但我认为这里面其实很多人都存在着一些对芯片设计的误解,误认为做芯片跟设计FPGA差不多,写Verilog代码跟写C代码差不多。实际上,数字电路芯片的设计跟模拟芯片的设计一样,也是有门槛的。有人讲,芯片设计人员的黄金年龄是35岁到45岁,这个年龄段的IC从业者大多已经具备了十年芯片电路设计经验,35岁到45岁的十年是芯片设计创造力最强的十年,比如夏大佬。这些人对HDL来表达电路结构已经相当的熟悉,真正做到了心中有电路,而且在写代码的同时就已经考虑到了芯片后端甚至流片后的方方面面。举个例子,再引用夏大佬帖子中对亚稳态处理的一句话:菊花司的规范简单粗暴,“异步处理以接收端时钟频率算,1GHz以内打两拍,以上打三拍,打拍寄存器在PR最后阶段替换为工艺库中专用的防亚稳态寄存器”。对于打拍操作解决亚稳态问题的事情,笔者深有感触,也深刻的体会到不同专业对HDL语言的理解偏差,对于没有底层晶体管级甚至器件行为等微电子基础的同学,很难解释,这也是我从微电子毕业后到通信工程专业继续做芯片遇到的第一个问题。好在可以引用别人做研究的结果来解释(见本公众号之前帖子:带有同步器的NoC结构是解决FPGA高速时序收敛的关键原因吗?)。有时候,那种隔行如隔山的感觉真的无法用语言来形容。我认为,HDL仅仅只是工具,HDL在实际设计芯片时,该怎么写是完全取决于实际要做的芯片的具体行为,尤其取决于底层物理电路的特性。

2、HLS语言的个人理解。

从上面介绍的内容来讲,最近几年爆火的HLS语言的作用就一目了然了。HLS语言只是用来快速验证某种设计思想是否可行一种语言,其作用类似于前些年的SystemC。举个例子,一个乘法器,硬件实现结构几十种,在不同的场合下需要选择适合具体场景的哪一种,这就需要HLS具备场景判断的能力,HLS编译器有这么智能吗?再比如,像上面夏大佬所说的1GHz以内打两拍,以上打三拍的操作,HLS编译器能知道吗?还有,本文下面所引夏大佬出的题目,采用HLS语言去实现后,能够综合出来跟HDL代码一样高效的电路吗?因此,笔者认为,HLS目前还只是比较适合学术界和工业界探索研究过程中的快速验证使用。但真正要做商用化的芯片,在PPA指标竞争白热化的战场上,把所有希望都寄托于编译器,只是一味的贪图快是会付出代价的。当然,也不排除,若干年后,HLS的编译器已经进化的足够厉害,生成的HDL代码人类可以看懂并修改,那就是另外一回事了。

3、数据结构课是一门硬件设计基础课。

做数字芯片设计,最重要的一门入门级课程应该就是数据结构课了。这里面详细介绍了FIFO、堆栈、链表、哈希等等几乎所有的基本操作,而这些在HDL设计电路中是最基础的功能单元。有同学可能会说,这门课明明是一门软件基础课啊,其实,现在的软件编程语言工具哪里还能让你看到底层的信息啊,除了C还有指针的概念,其它软件编程语言中队列等都是现成的,直接调用就可以了。

好了,啰嗦的挺多了,下面就转载一下原文并给出题目的简单解析。同学们可以自己做一遍亲身体会一下,感觉还是不一样的。也可以在知乎上看一下回帖中大家给出的方法,再感受一下什么是软件设计思想,什么是硬件电路的设计思想。另外,笔者认为,编码是最能体现硬件设计思想和软件设计思想不同的一种场景。大家还可以参考另外一篇文章,也比较容易理解编码在硬件设计中的重要意义,点击链接可见:《FPGA中有限状态机的状态编码采用格雷码还是独热码?》。

以下引用知乎原文:

好不容易放假一天,趁坐着洗脚按摩的功夫怒答一波。看答案讲没用的人挺多啊,挺不解的。我主要做架构,兼一个80人规模世界顶尖的处理器设计验证实现团队的manager,指导兄弟们最多的就是苦口婆心劝大家看《计算机体系结构量化研究方法》和《数据结构与分析》,前者是理解系统的基础,后者是编码的基础。收效甚微,嗨 (ノ=Д=)ノ┻━┻

你们知道现在招聘正统一个体系结构背景,IC方向硕士或者博士多难么……有钱都招不到啊。嗨(┯_┯)

数据结构也是,‘’16bits位宽寄存器,用五(六也行)级逻辑判断其中有15个0和1个1‘’,这么道题目,面试无数,几乎没有人能答出来,连给我衍生‘’14个0和2个1‘’的机会都没有。

回想一下,我是怎么学的呢?数据结构是大学本科课程,比较感兴趣,是少数几个认真学习的课程之一,体系结构,原则上和我专业(通信)无关,但研究生老板恰好是2000年左右国内一大批EE类国外图书翻译版的评委,实验室一套全有,处于个人兴趣自学了体系结构一书。回想起来,这两本书贯穿了整个职业生涯。

表面上,体系结构很虚,确实像是装逼专用,实际上,这是一种系统分析的语言和理解的基础,学过的人和没学过的人要聊起来,要达成理解的一致,光铺垫热身就要很久。要类比的话,学了牛顿三定律的人,通常就认为世界是酱紫了,而学过相对论甚至弦论,看待一件事物时会有另一种视角,就是跟一个认为两个铁球同时落地的人讲光速恒定的赶脚。

体系结构就是如此,他用传统CPU为视角,对最本质的基础架构:冯诺依曼,进行了详细的量化分析。我常常问手下的兄弟,为啥我们要做通用CPU,这个和做个GPU或者DSP,甚至火热的TPU有啥区别呢?为啥要有CACHE呢?为啥要有MMU呢?MSI和线中断又是啥区别呢?这些问题的答案,汇聚到最终,也就是对冯诺依曼的理解了,看明白这点,面对火热的TPU、寒武纪什么的,很大程度就能理解他们本质上是在冯诺依曼的基础上,在数据的时间性和空间性取了什么巧了。对实际工作来讲,体系结构也是重要的,以ST验证为例,不懂体系结构的人,看待一个系统,就只知道CPU在取指,错一个bit就跑飞了,数据在总线上流动,乱七八糟,一个地址变化好几次,定位起来困难死了,分不清MEMORY或IO属性,不理解中断嵌套的层次,更勿论虚拟化和docker…… 这样的同志定位一个芯片系统性问题,得半年。

嗨,昨天还有人问我如果软件写错程序,会不会践踏堆栈,硬件要不要做一层地址判定保护…………这里的同志觉得呢?

有时候我还在想,国内好的体系结构的学生少,是学校不教呢,还是老师不合格啊…… 举个栗子,intel的skylake相比haswell一个大变化就是cache层次从inclusive变成exclusive,这个变化无论工业届还是学术界都是重要的吧。那么exclusive相比inclusive的优劣是什么?谁都知道exclusive会有效增大cache容量,那为啥不第一天就用呢?面试国内体系结构相关的硕士博士,结果是知道这个变化的人就少之又少了,更勿论……

2017-05-02,更新提到的题目,16bits寄存器找1的verilog表达,回复中依旧无人答对。如下图看上去无人明白这个答案的意义,还是在讲什么加法器、迭代、二叉树之类,哎╮(╯_╰)╭

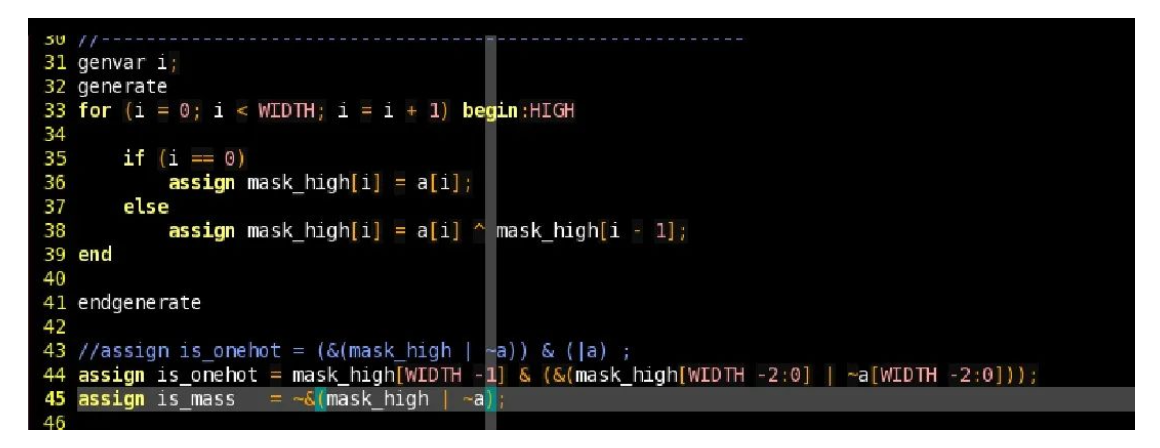

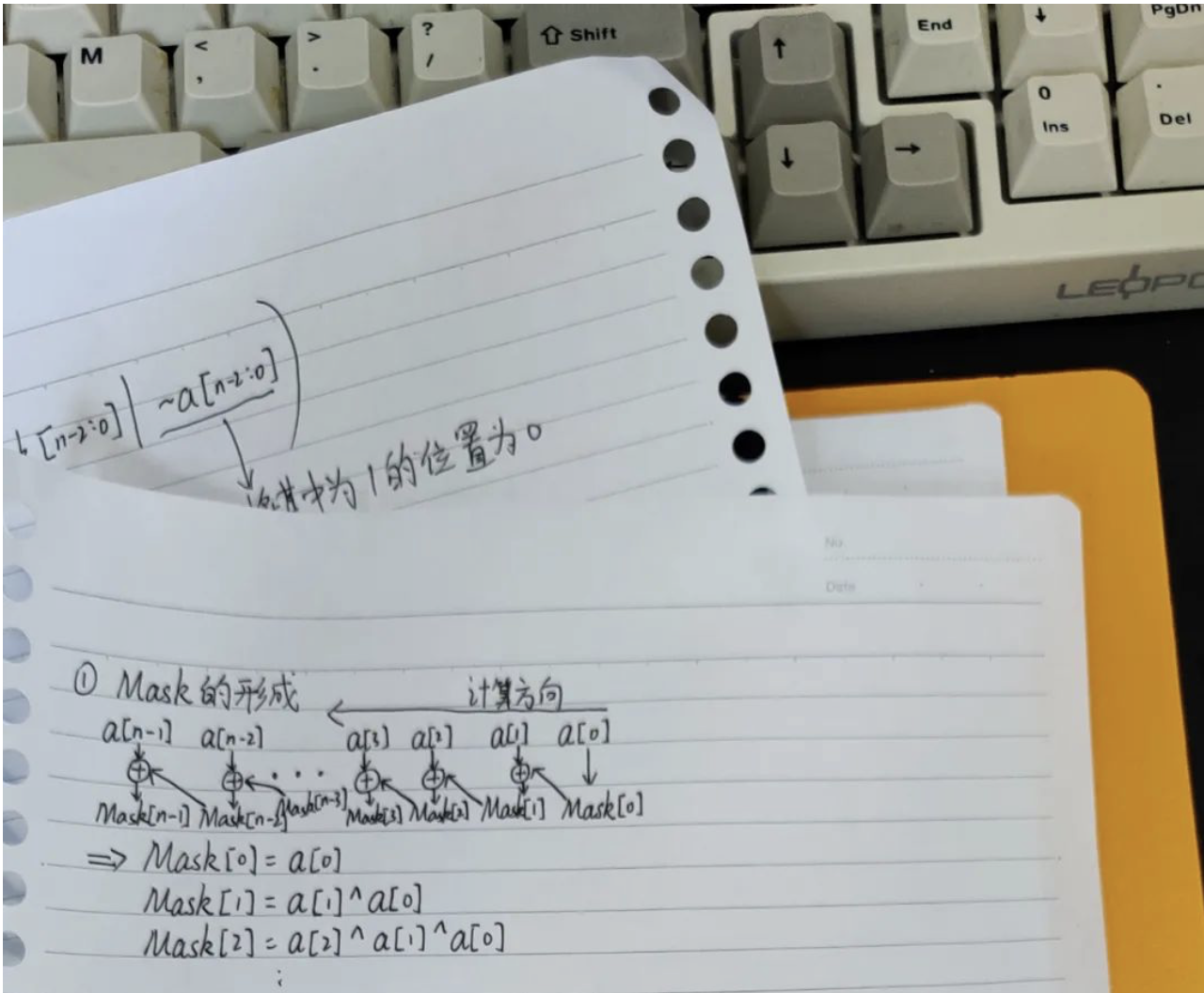

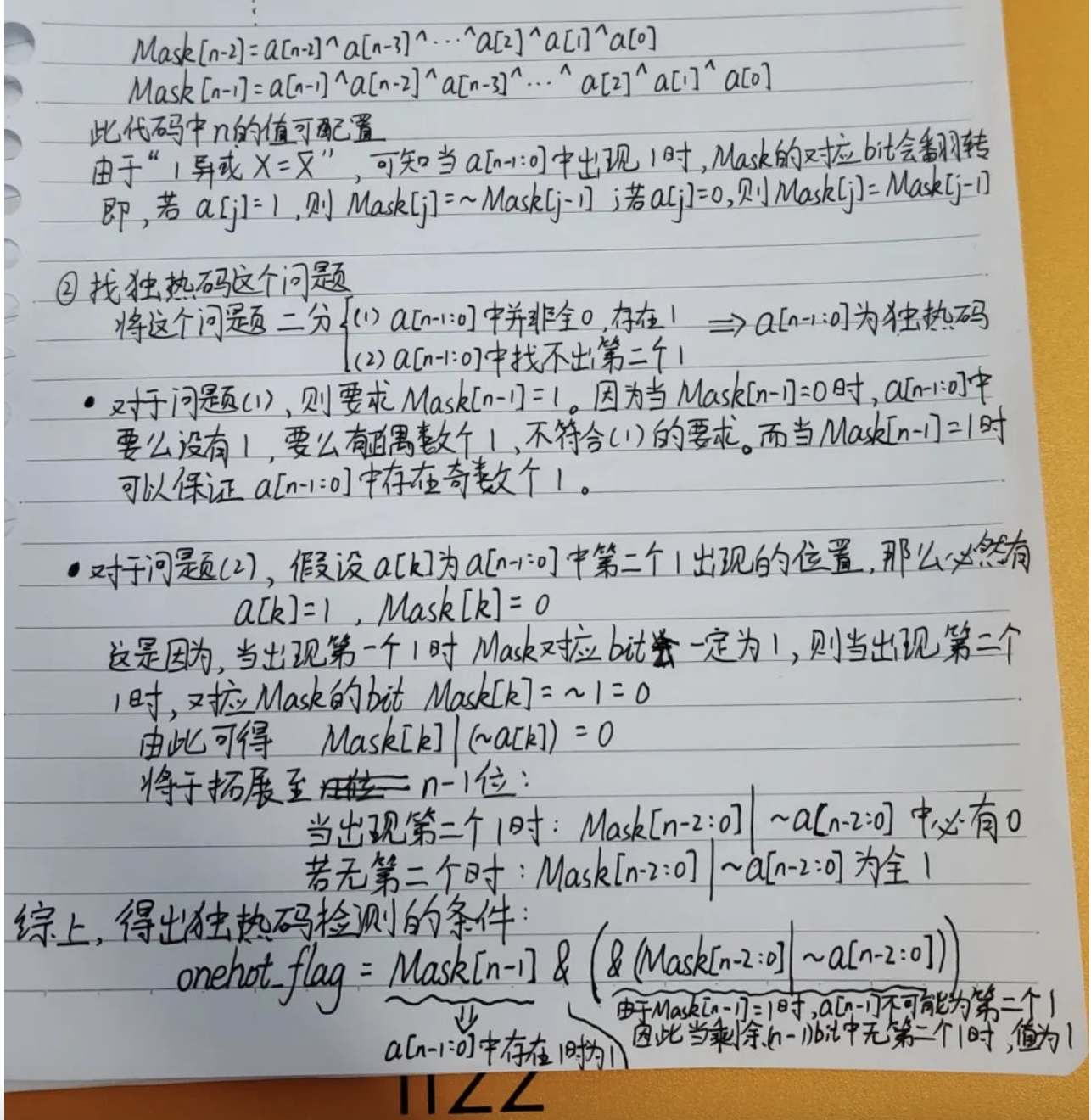

以下是高璐同学整理的张仲禹同学的推导过程:

Mask的形成

此代码中n的值可配置

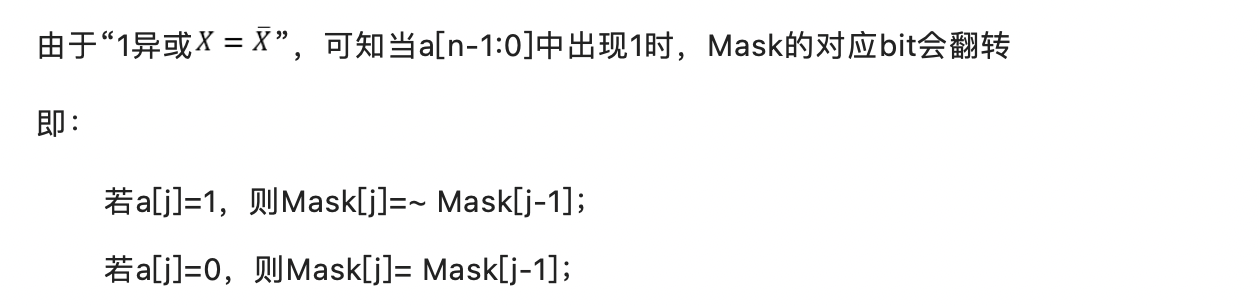

找独热码这个问题

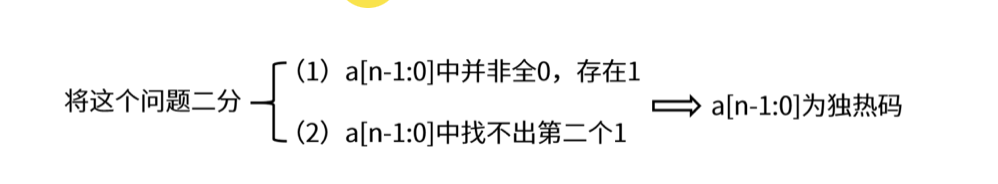

- 对于问题(1),则要求Mask[n-1]=1。因为当Mask[n-1]=0时,a[n-1:0]中要么没有1,要么有偶数个1,不符合(1)的要求。而当Mask[n-1]=1时,可以保证a[n-1:0]中存在奇数个1。

对于问题(2),假设a[k]为a[n-1:0]中第二个1出现的位置,那么必然有a[k]=1,Mask[k]=0

这是因为,当出现第一个1时,对应Mask的bit Mask[k]=~1=0由此可得 Mask[k] | (~a[k]) = 0

拓展至n-1位:

当出现第二个1时:Mask[n-2:0] | (~a[n-2:0])中必有0

若无第二个时:Mask[n-2:0] | (~a[n-2:0])为全1

综上,得出独热码检测的条件:

onehot_flag=Mask[n-1]&(&(Mask[n-2:0]|~a[n-2:0]))

其中:

- Mask[n-1]:当a[n-1:0]中存在1时为1

Mask[n-2:0]|~a[n-2:0]:由于Mask[n-1]=1时,a[n-1]不可能为第二个1,因此当剩余(n-1)bit中无第二个1时,值为1

以上推导过程由张仲禹同学提供,手稿如下:

图文排版丨高璐

图文校对丨高璐

责任编辑丨潘伟涛

原文链接:网络交换FPGA

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。