【嘉勤点评】高云半导体发明的FPGA单粒子反转校验电路方案,由FPGA的内部产生校验码,因此无需对额外的校验码进行处理。不仅使得FPGA配置文件变小,而且也能缩短FPGA的配置时间以及提高配置效率,从而满足系统的实时性要求。

集微网消息,现场可编程逻辑门阵列(FPGA)被广泛地应用到各个领域中,如工业控制、嵌入式系统、密码学、航空飞船和网络环境等。由于FPGA具有性能高、一次性工程费用成本低的特点,其也适用于大电路的实现以及快速研发新产品。

但是随着系统性能和容量的指数增长、集成电路的噪声容限减少、电源电压降低以及低能量的粒子诱发单粒子反转(SEU)的可能性增大,使得FPGA内部的配置文件容易受SEU影响而发生软错误。

针对SEU问题,现有的方案采用错误检查和纠正(ECC)校验来改善系统稳定性。首先,在FPGA外部的处理模块使用软件生成配置文件的ECC校验码。然后,把ECC校验码写到配置文件中,再把包含校验码的配置文件写入FPGA内部。由于FPGA配置文件中包含额外的ECC校验码,需要先对配置文件中额外的校验码进行处理。

一般来说,如果配置文件较大,就会增加FPGA配置的时间,并降低FPGA配置的效率。特别是在设计规模较大、配置文件较复杂的应用场景下,现有方案中的FPGA配置效率下降较为明显。为此,高云半导体在2019年11月13日申请了一项名为“一种FPGA单粒子反转校验电路和方法”的发明专利(申请号:201911106828.4),申请人为广东高云半导体科技股份有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项技术方案吧。

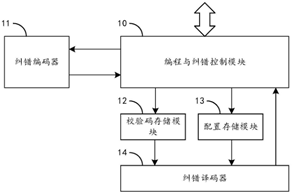

如上图,为该专利中发明的FPGA单粒子反转校验电路的示意图,该电路包括集成在FPGA内部的编程与纠错控制模块10、纠错编码器11、校验码存储模块12、配置存储模块13以及纠错译码器14,这些模块均集成在FPGA的内部。

编程与纠错控制模块用于从FPGA外部读取配置文件,配置文件用于对FPGA进行配置,其通过编程IO接口与外部处理模块连接,例如能够处理信息的于单片机或者CPU等。纠错编码器用于根据FPGA配置文件生成校验码,包括汉明码(ECC)校验、奇偶校验以及CRC校验等。

其中,汉明码是一种线性分组码,线性分组码是将信息序列划分为长度对k的序列段,在每一段的后面附加r位校验码,且校验码与信息码之间构成线性关系,即它们之间可有线性方程组联系。这样构成的码字称为线性分组码,标准汉明码可实现1bit的纠错或2bit的检错。

校验码存储模块和配置存储模块分别用于写入校验码和FPGA配置文件,这两个模块均可由编程与纠错控制模块或其他模块控制校验码存储模块写入和读出信息。纠错译码器用于利用校验码存储模块写入的校验码和配置存储模块写入的FPGA配置文件进行单粒子反转校验,其可以通过校验来判断FPGA中信息是否被低能量的粒子诱发单粒子反转。

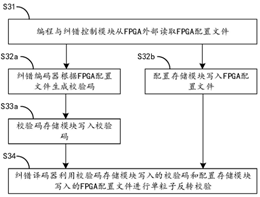

如上图,为该专利中发明的FPGA单粒子反转校验方法的流程图,首先,由编程与纠错控制模块从FPGA外部读取FPGA配置文件,纠错编码器根据FPGA配置文件生成校验码。接着,校验码存储模块写入校验码,并由配置存储模块写入FPGA配置文件。最后,纠错译码器利用校验码存储模块写入的校验码和配置存储模块写入的FPGA配置文件进行单粒子反转校验。

从上述的流程中可以发现,这种方案的实施过程中,无需对额外的校验码进行处理,这就使得FPGA的配置文件变小,实现了FPGA配置时间的缩短,从而提高FPGA的配置效率。该方案尤其适用于FPGA设计规模大、配置文件复杂的应用场景下。

此外,该方案还增加了对分布式SRAM的保护功能,把分布式SRAM比特信息修改为预置值。从而消除了分布式SRAM比特信息对校验的影响,进一步提高了校验的效率,具有较好的抗SEU能力。

以上就是高云半导体发明的FPGA单粒子反转校验电路方案,该方案由FPGA的内部产生校验码,因此无需对额外的校验码进行处理。不仅使得FPGA配置文件变小,而且也能缩短FPGA的配置时间以及提高配置效率,从而满足系统的实时性要求。