曾经有人在 Reddit 上问,应该如何学习 AXI 协议?

ZiPCUP(学习网站链接)上的大佬针对此问题总结了自己的学习路线,尤其针对一些网上的学习资料,针对性的提出了一些批评性的建议,下面开始大佬讲解AXI学习路线(大佬的评判语言比较过激,我已缓和处理)~

分割线

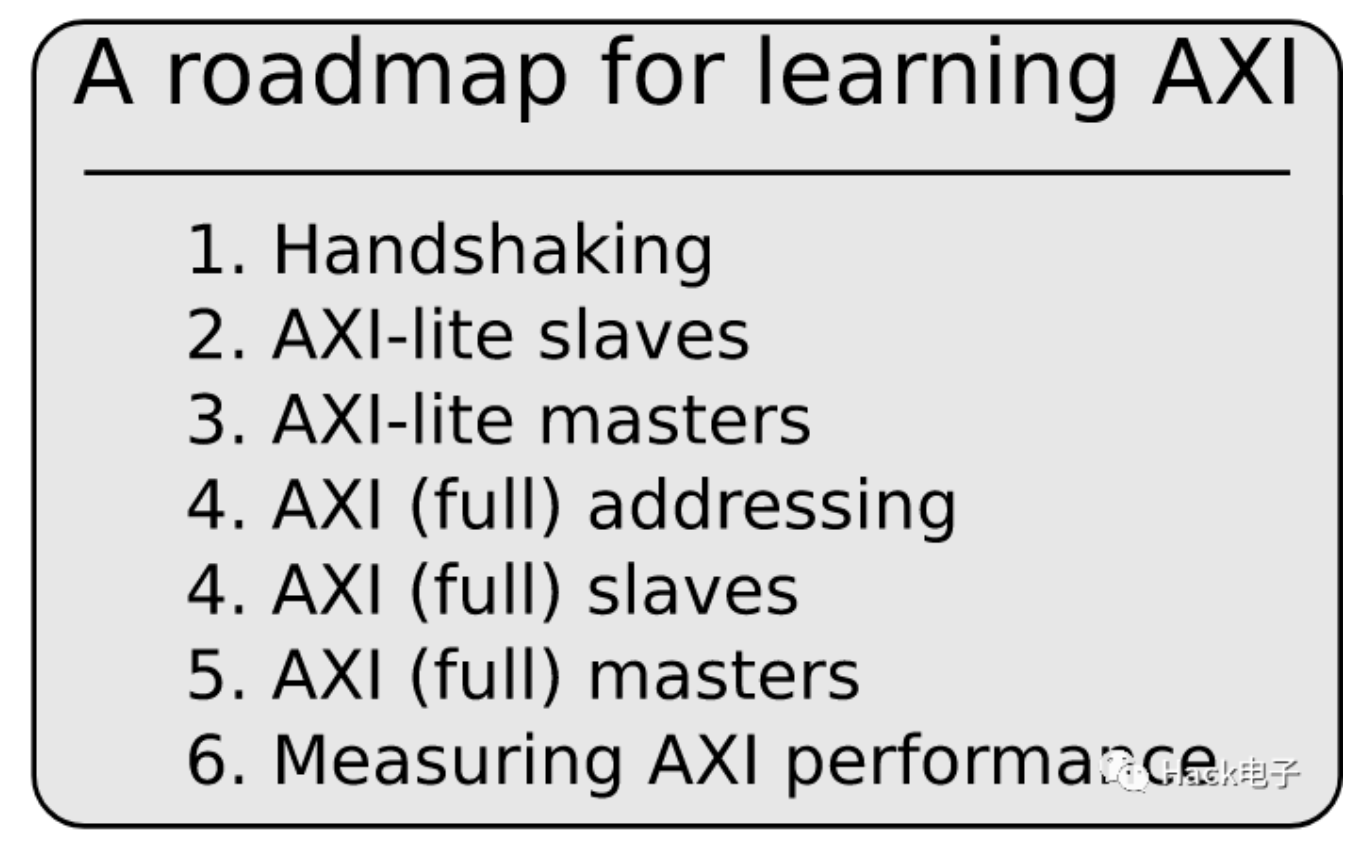

以下总结了我的基本答案。

首先,不要从 Xilinx 的示例设计开始。虽然历程很不错,对不起,但他们的例子非常糟糕。甚至他们的AXI Stream master 设计极其糟糕。遗憾的是,他们既没有修复这些设计,也没有更新他们的培训材料。

图 1,学习 AXI 的基本路线图

很多人建议最好从学习握手开始,而大多数 AXI 流协议就是这样:握手。这一点我非常同意。因此,我建议任何人从学习 AXI 的握手规则开始。正如那篇文章(AXI 握手规则:http://zipcpu.com/blog/2021/0...)解释的,AXI 流协议只不过是简单的握手,可以(大部分)忽略 TID、TSTRB、TKEEP 和 TDEST 信号。并且还可以在那篇文章了解 Xilinx 是如何弄乱他们的示例:AXI Stream master,并且将了解修复它是多么容易。

一旦了解了AXI 握手,我建议学习有关 skidbuffers的知识(其他文章将会解释)。没有它们,在不违反 AXI 规范的情况下,你的设计吞吐量永远不会超过 50%。

我要去的下一个地方是:研究 AXI-lite。它让Xilinx(和其他未命名的公司)头疼不已,并构成了他们示例设计中许多错误的背景。建议查看这篇文章,描述如何修复 Xilinx 的(糟糕的)AXI-lite VHDL 示例(http://zipcpu.com/blog/2021/05/22/vhdlaxil.html)。

对于可能需要完整 AXI 规范的事情,可以找到可行的示例开源或供应商设计。(DMA、 MM2S、 S2MM、 虚拟FIFO、 视频帧缓存读取、 视频帧缓存写入等)(https://github.com/ZipCPU/wb2axip/tree/master/rtl)。

如果有兴趣超越 AXI-lite,那么是时候了解AXI寻址,以及各种 FIX、WRAP 和 INCR 寻址模式以及 AxSIZE 字段如何影响它们。这个很重要。Xilinx甚至没有尝试在他们的示例中做到这一点,而且我看到很多 ASIC 设计甚至把这个寻址搞砸了。在开始构建第一个完整 AXI slave之前,需要了解这一点。事实上,我已经在我自己的许多设计中使用了在那篇文章中构建和介绍的下一个 AXI 地址模块(https://github.com/ZipCPU/wb2axip/blob/master/rtl/axi\_addr.v)。

一旦了解了寻址,或者至少在将其简化到足以使用之后,下一步就是构建一个功能齐全的 AXI slave。

通过在 AXI-Lite slave上编写 AXI slave,您将获得什么?不多。与通过构建 AXI-Lite slave已经获得的性能相比,构建 AXI(完整)slave并没有太多的性能提升——至少,对于大多数用途来说没有太大的提升。会看到什么性能差异?好吧,在良好的 AXI 到 AXI-lite 桥接之后,可能会发现自己在每个事务中损失了大约 2 个时钟的延迟。在 AXI 到 AXI-lite 桥接不良之后?在这种情况下,可能会在每个事务中损失 4-8 个时钟的吞吐量。当然,你总是可以切换回更好的桥 恢复这个损失的吞吐量——所以从 AXI-lite 从机切换到 AXI(完整)从机并没有太多好处。

然而,对于 AXI master,情况就不同了。不过,我同样建议从AXI-Lite master开始。从技术上讲,这样的master应该能够与 AXI master一样快。实际上,可悲的是,许多设计削弱了他们的 AXI-lite 实现。(你好,Xilinx?)

对 AXI master的全面讨论变得困难。我还没有(还)想出如何简化材料来写一篇关于如何构建通用 AXI master器的帖子,这已经够难了——通常来说,寻址就是那么难。

在这些AXI master示例中,有两个值得一提,因为我已经写过关于它们的文章。第一个讨论如何使用 AXI-Lite 协议为 ZipCPU 构建内存控制器(http://zipcpu.com/zipcpu/2021/04/17/axilops.html),而第二个讨论将内存控制器升级到 AXI(完整)所需的修改(http://zipcpu.com/zipcpu/2021/09/30/axiops.html)。第二篇文章介绍了AXI 独占访问协议(AxLOCK 和 EXOKAY),然后介绍了如何构建使用它的master——尽管我只真正了解这种协议的 CPU 用例。它还讨论了 AxADDR 和 AxSIZE 之间的一些具有挑战性的交互。

如果真的要深入研究 AXI 协议,那么了解如何测量 AXI 性能就会变得很重要。

以上将为您提供大部分内容。但是,它也会留下关于 AxCACHE、AxPROT 和 AxQOS 的用途,或者何时应该使用 AxID 字段的问题。实际上,可能还会对 AxSIZE 感到疑惑,以及为什么它是协议的重要组成部分。对于这些的讨论,让我指出我自己在一段时间前的一个 reddit 问题:AXI 太复杂了吗(https://www.reddit.com/r/FPGA/comments/egkrce/is_axi_too_complicated/)?

正式验证 AXI

不久前,有人问我是否有可能编写一门关于如何验证 AXI 组件的课程。当时,我为这样一门课程勾勒出以下大纲——一个主要与上述大部分进展相匹配的大纲。

该课程将从对形式方法的快速回顾开始:什么是断言和假设,以及与归纳相关的一些独特挑战。

图 2,可能构成正式验证 AXI 组件课程的课程

AXI 设计练习

在学习任何新主题时,在学习过程中锻炼新知识很重要。因此,这里有一个列表,其中包含一系列难度越来越大的练习,在学习 AXI 时可能会发现这些练习很有价值。

图 4,练习练习,用于学习 AXI

- 构建并验证 AXI Stream 组件。

- 其他示例包括流处理网络数据包——例如可以识别、加密或解密 UDP 数据包的流组件。

- 构建和验证 AXI-lite 总线

- 一个更复杂的 AXI-lite 总线主控器,当然也是一个更感兴趣的主控器,可能是向CPU 指令获取单元添加一个小型 FIFO。

然而,我对这些练习的最大问题是它们到最后变得相当具有挑战性。我不确定我将如何将 DMA 的验证融入仅几天的 AXI 形式验证课程中——尤其是因为我花了几周时间来验证我自己的 DMA。所以……我会继续睁大眼睛寻找更好(更简单)的例子来使用和使用。在那之前,这仍然是一个非常好的练习列表,任何学生都可以使用它来学习他或她自己的基本 AXI 概念。

结论

我不确定我是否在网上看到过很多好的 AXI 培训材料。到目前为止,我所看到的大部分都是Xilinx的材料——这些材料会让你从一个"破损的设计"开始并修改它。此外,讨论如何正式验证 AXI 设计的材料并不多。

同时,我提供了上面学习 AXI 的路线图。并非每个人都需要上述所有课程或练习。但是,上面概述的课程和练习应该足够彻底,任何人都可以完全学习该主题。

总结

上面文章是摘自ZipCPU上大佬的博客(http://zipcpu.com/blog/2022/05/07/learning-axi.html)因为整篇文章偏于口语化所以一些翻译不太准确,强烈建议自己去看下原文,下面总结一下主要内容:

- AXI学习路线,从握手协议开始,然后学习Skid Buffer;

- 学习设计AXI-LITE SLAVE,不要从xilinx官方历程开始,学会自己设计;

- 学习AXI寻址方式以及AXI SLAVE设计;

- 学会验证自己设计的AXI模型;

- 跟着练习题学习AXI,包括FIFO的使用及验证;

- 最后,这篇文章是总结性文章,所以有些写的很乱,建议阅读原文,里面有大约几十个链接,包括之前大佬写的关于AXI的文章和资源。

作者:比特波特

来源:Hack电子

相关文章推荐

更多AMBA协议相关知识请关注</span>Arm AMBA 协议集专栏欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。。