提纲:

1. AXI基本概念

- AMBA总线中APB,AHB,AXI的关系

- 读操作

- 写操作

2. AXI Ordering

- Outstanding。

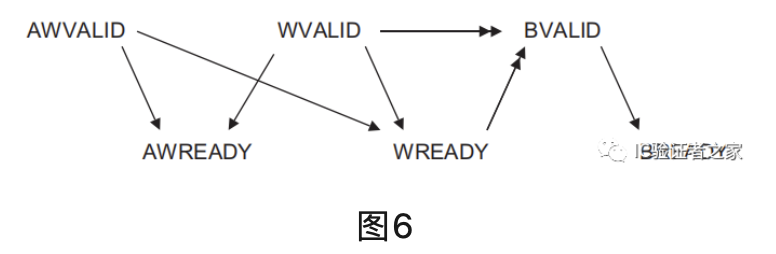

- Aw-W-B的valid/ready依赖关系

- AR-R的valid/ready依赖关系

- 相同ID数据保序,不同ID支持out of order

- valid与ready的依赖关系

- 通道内的Ordering

- 通道之间的Ordering

3. AXI Burst数据量的约束

- 不能跨4K

4. 总线异常

- Error Response的处理方式

- 总线挂死的相关场景和处理方式

- 复位总线

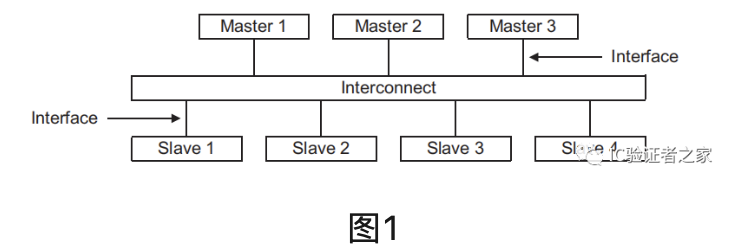

在SoC芯片中,信息的传递离不开NoC(Network on Chip, 片上互联网络)。通过该网络,可将多个Master端口和Slave端口连接起来。如图1所示。而当前比较流行的NoC是ARM定义的AMBA(Advanced Microcontroller Bus Architecture),其中包括3种:APB(Advanced Peripheral Bus),AHB(Advanced High-performance Bus)和AXI(Advanced eXtensible Interface)。

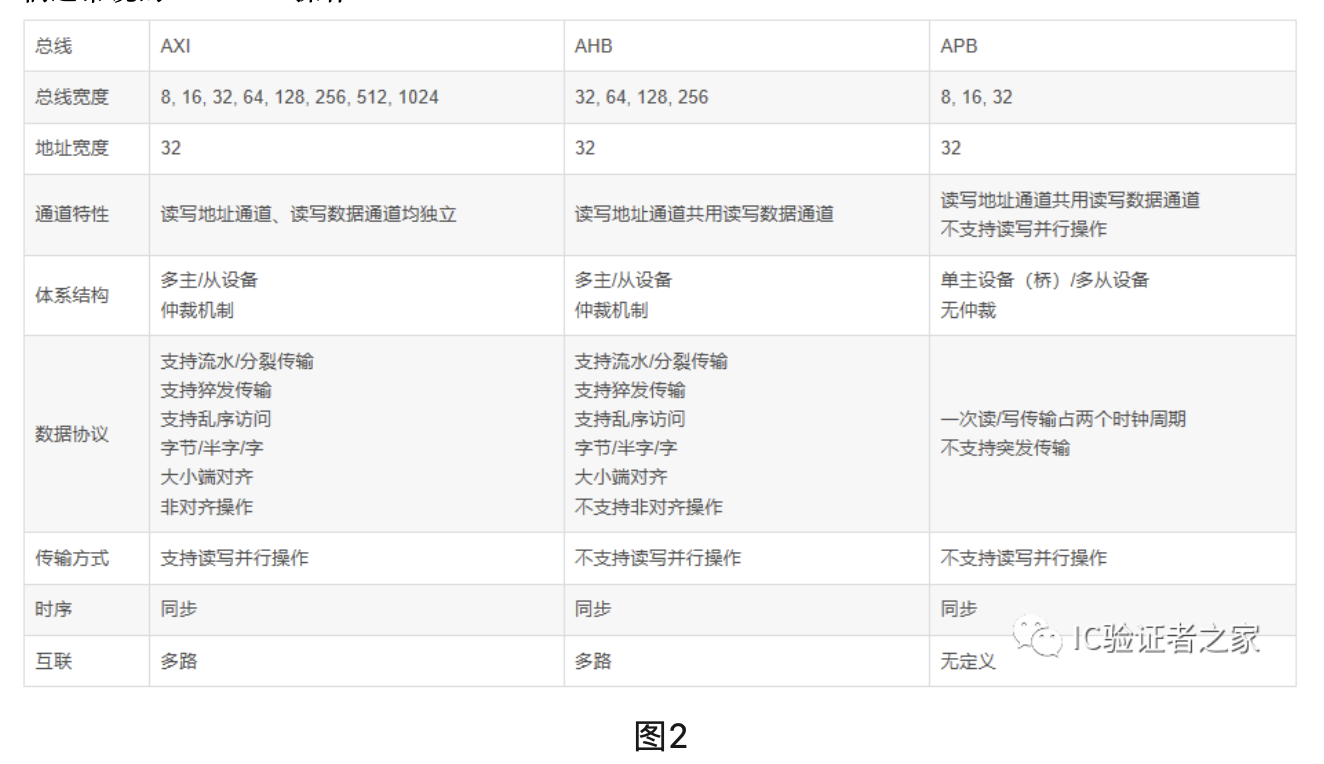

图2罗列了三种总线接口的特性,其中的猝发传输就是指1拍传输命令,对应多拍传输数据,即我们通常说的AXI Burst操作。

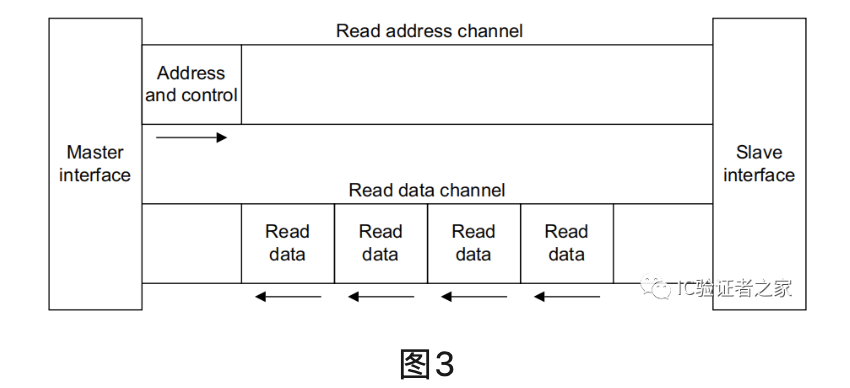

读写操作是AXI总线的基本操作。读操作是指获取到缓存或者寄存器中的数据的操作,如图3所示。

写操作是指将数据写入到缓存或者寄存器的操作,如图4所示。

从图2可知,在传输较多数据时,AXI的效率是最高的,因为他不仅支持Burst操作,也支持乱序和outstanding。并且通过五路独立通道分别执行读和写操作,实现了读写并行执行。但是AXI逻辑复杂读最高,消耗的逻辑资源也是最多的。APB的效率是最低的,因为APB不仅不支持Burst传输,而且读写公用同一组接口。他的每个读或写操作只能串行进行,一个操作只能携带一拍数据。好处是逻辑功能最简单,消耗的逻辑资源也最少。AHB的传输效率和效率资源都介于两者之间。

下面我们窥探一下AXI高效传输的原因吧。

首先,AXI的高效率传输与AXI各个传输通道内和通道之间的Ordering机制是分不开的。

Out-of-Order(乱序)是指在AXI写数据通道或读数据通道内部,可以将属于不同AXI Burst的每拍数据(AXI Transfer),进行乱序传输。这样大大增强了NoC的灵活性,不需要串行的传输每个AXI Burst的全部读数据或写数据了。通过RID或WID来标识每一拍数据(AXI Transfer)属于哪个AXI Burst,各个AXI Burst的数据都可以间插着乱序的在NoC上传输,提升了NoC的传输效率。

同时,Out-of-Order机制会增加逻辑的复杂读,尤其是当AXI Burst的数据量(AXI Burst Length)很大时。根据AXI协议规定,AXI3.0支持最大AXI Burst Length是16,而AXI4.0是256。为了降低设计复杂读,AXI4.0的写操作就不再支持Out-of-Order了,WID也就没有存在的意义了。

相同ID的写数据或读数据,AXI认为其数据之间的order是依次顺序进行传输的,而这也是需要整个NoC来保证的:

- Master要保证相同ID的各个写操作的写数据是依次顺序发送出去的。

- Slave要保证相同ID的各个读操作的读数据是依次顺序返回的。

- 在网络传输中,相同ID的各个读或者写操作的数据依次顺序传输的。

在每个AXI通道内部,每一拍信息的传输都需要进行valid和ready握手。信息发送方先将valid信号拉高,表示信息有效。信息接收方输出的ready信号表示是否可以接收信息。在信息传递的发送方,中介和接收方,都需要valid和ready信号同一个时钟沿都是1,才表示当拍信息传递完成。若接收方的ready信号是0,则发送方应该将信息和valid信号保持不变,直到信息被成功接收。

在NoC上,通常会关联多个AXI Master,然而AXI ID的宽度是有限的,尤其是当每个AXI Master发出的AXI Burst不是固定ID时,那么NoC要传输各个AXI Master的AXI Burst,只靠AXI ID是不够的,那么在NoC设计中,可以把AXI Burst的User信号使用起来,这需要软件为每个加速器的AXI Master配置唯一的user信息。也可以在NoC传递报文时,为每个AXI Master的ID做bit位的扩充,例如将4bit AW ID扩展为8bit AW ID。数据或相应返回时,由NoC自己剥去增加的bit位。这是纯硬件行为,软件不感知。AXI协议推荐后一种方式。

AXI实际上有5个通道,其中读操作2个,写操作3个。各个通道之间的关系也很有意思。

其次是Outstanding机制。

AXI的每一个读写操作的地址和数据也是有独立的通道进行传输。因为是独立的通道,地址和数据的传输可以并行进行,即各自传输各自的,而不用串行的传输每一个AXI Burst。这个就是AXI的Outstanding机制。

通道之间的valid和ready信号也有一定的关联。

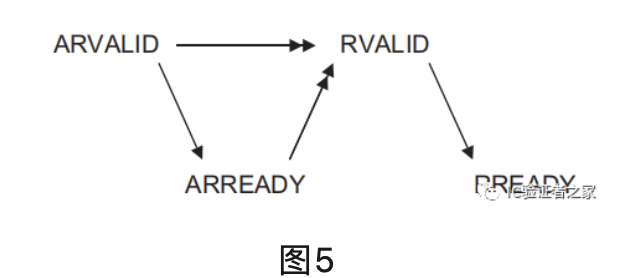

其中读地址通道和读数据通道的关联如图5所示。ARvalid和ARready是独立的,没有任何关联。Rvalid和Rready也是独立的,没有任何关联。但是Rvalid必须是ARvalid和ARready握手成功之后,才能拉高。

写地址,写数据和写响应的关联如图6所示。AWvalid, AWready是独立的, Wvalid, Wready是独立的, Bvalid, Bready是独立的,AWvalid和Wready是独立的,Wvalid和AWready也是独立的。但是Bvalid必须是相关AXI Burst的写数据的全部Wvalid和Wready都握手成功之后,才能拉高。在开发AXI 的BFM时,关于valid和ready的握手信号要覆盖到valid先于ready拉高,valid于ready同时拉高和valid后于ready拉高的情况。

AXI Burst的数据,在memory空间中,不能跨域4KB边界。通常情况,系统memory空间设置是按照4KB划分为不同的page, 当一个访存操作涉及到memory区间分别属于不同的Page,该访存操作消耗的资源会大幅增加,带来的时延也会大幅增加。通常情况,跨Page的访问都是软件的寻址发生了错误。因此AXI协议规定了一个Burst操作涉及的memory区间不能跨4KB。

对于每一次AXI Burst操作,AXI Slave都会反馈response信息,告知Master相应的AXI操作是否成功。

两比特信号表示4种response信息。其中0表示访问成功,1,2,3分别表示Exok,SlvErr和DecErr。在验证看来,除了0之外,其余3中都是表示AXI操作有异常错误发生,逻辑应该能够做出相应的输出,例如上报中断,上报错误类型和上报错误地址等等。在仿真中,可以在参考模型中产生error response,放入队列,在发送到AXI slave VIP中,AXI Slave driver在驱动response信号时,可以从队列中取,这样可以实现对error response的自动化比对。

AXI总线的异常处理是需要十分的稳妥和小心的。因为AXI通常和NoC对接,而NoC是SoC的交通网络,就像人体的血管一样。如果处理不好,则会直接影响NoC的功能,进而影响整个芯片的功能。例如一个加速器的设计缺陷导致某种场景下会挂死总线,那么整个芯片就报废了。

所以,对每一个AXI Master的复位首先应该确保该Master发出的全部AXI Burst的传输都已完成,即所有相关的response和data都已返回。尤其是当软件想要复位某一个Master时,要首先保证他发出的全部AXI操作都已经完成了。如果因为异常,导致该AXI Master已开始传输的AXI Burst不能完成传输,那么就需要复位整个NoC和与之关联的全部Master和Slave了,甚至于要复位整个芯片。而这取决于系统工程师的分析和决策了。

最近诸事不顺,心情颇坏。想到里昂的话,“生活的艰辛不只在童年,生活的艰辛一直都在”。精辟。生活不易,且行且珍惜。

作者:一只特立独行的猪

文章来源:IC验证者之家

推荐阅读

- IR Drop 对芯片性能及功能的影响

- PCIE,USB,SATA ,Ethernet 都在用的SerDes到底是个啥?

- 搞芯片,不懂逻辑综合是啥?

- IC各细分领域公司简介以及薪资调研(GPU篇)

- 会写VIP,会提取testplan,GPT进化的太快了!!!

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。