【嘉勤点评】胜科纳米的堆叠封装集成电路芯片专利,通过匹配数据库,无需对待测3D堆叠封装集成电路芯片进行研磨,就可以推断失效位置所在层,达到失效分析准确定位的目的。

集微网消息,近日由胜科纳米牵头组织的集成电路分析测试及关键材料装备技术研讨会在福建晋江召开。本次会议通过开展集成电路产业论坛活动,探讨集成电路分析测试及关键材料装备技术方面的重要话题。

随着半导体晶圆制造趋向先进制程,摩尔定律面临巨大挑战。传统的覆晶封装、层叠封装等技术已不符合部分高性能芯片的要求,因而2.5D/3D先进封装技术需求逐渐增加,成为解决高端产品应用和延续摩尔定律的核心技术之一。但是,3D封装技术的发展,也给失效分析带来新的挑战。因此如何对3D堆叠封装集成电路芯片进行失效定位,成为亟待解决的技术问题。

为此,胜科纳米于2022年4月11日申请了一项名为“一种3D堆叠封装集成电路芯片及其失效定位方法和装置”的发明专利(申请号: 202210371179.6),申请人为胜科纳米(苏州)股份有限公司。

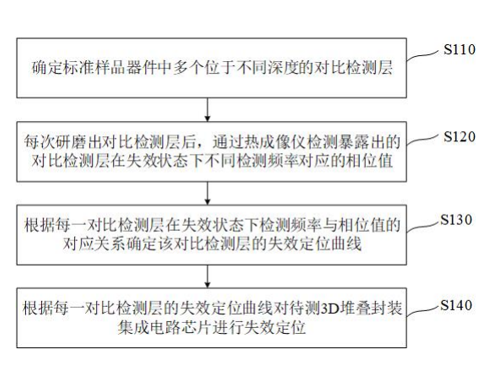

图1

图1为3D堆叠封装集成电路芯片的失效定位方法流程图,该方法主要包括以下步骤:

首先确定标准样品器件中多个位于不同深度的对比检测层(S110)。 具体的,标准样品器件为待测3D堆叠封装集成电路芯片同类型未失效的3D堆叠封装集成电路芯片。其中同类型为标准样品器件的组成膜层以及每一组成膜层对应的位置与待测3D堆叠封装集成电路芯片的组成膜层以及每一组成膜层对应的位置相同。不同的膜层位于器件中不同的位置,即对应不同的深度。3D堆叠封装集成电路芯片发生失效可以理解为,3D堆叠封装集成电路芯片中某一位置的膜层发生短路等异常情况,从而影响了芯片正常工作的情况。

每次研磨出对比检测层后,通过热成像仪检测暴露出的对比检测层在失效状态下不同检测频率对应的相位值(S120)。例如3D堆叠封装集成电路芯片短路失效后,发生短路的位置会产生较高的温度成为热点,基于材料热传递性质,短路位置产生较高的温度会随着时间往低温处传递出去,进而传递到器件的外表面。

然后根据每一对比检测层在失效状态下检测频率与相位值的对应关系确定该对比检测层的失效定位曲线(S130)。具体的,在获取不同层对比检测层的检测频率与相位值的对应关系时,采用的检测频率可以相同也可以不同。优选的,采用的检测频率相同。最后根据每一对比检测层的失效定位曲线对待测3D堆叠封装集成电路芯片进行失效定位(S140)。

简而言之,胜科纳米的堆叠封装集成电路芯片专利,通过匹配数据库,无需对待测3D堆叠封装集成电路芯片进行研磨,就可以推断失效位置所在层,达到失效分析准确定位的目的。

胜科纳米是世界顶尖的独立第三方实验室,公司的材料分析和失效分析实验室配备全套的高端分析仪器,搭建开放式的专业分析平台,公司拥有世界一流实验设备,将成为科学研发及制造业首选的分析服务提供商。