集微网报道,无人驾驶、边缘智能、智慧城市、万物互联、元宇宙等概念和应用不断涌现,创新应用需求的多点爆发,推动半导体产业进入技术融合时代,芯片的后摩尔时代已经悄然而至。

芯片技术高速发展,并呈现出更高的集成度、更复杂的电路设计等特点。而无论是单颗芯片的复杂程度还是先进封装技术实现的异质集成,都对芯片在前道至后道测试上提出了更高的测试挑战,测试需求也更复杂。

第五十八期“集微公开课”于8月5日(周五)上午10:00直播,邀请到了爱德万测试(中国)业务发展总监葛樑带来《后摩尔时代IC测试的挑战与创新》的主题分享,从应用场景及芯片的构成出发,详细解释了IC测试面临的各项新挑战以及爱德万测试最新的测试解决方案,为大家在后摩尔时代的芯片测试的创新提供一些新思考。

本次直播全网在线累计观看人数:40042,其中爱集微官网&APP 35900,集微官方微博3380,B站122,视频号640。

进入技术融合时代的芯片测试挑战

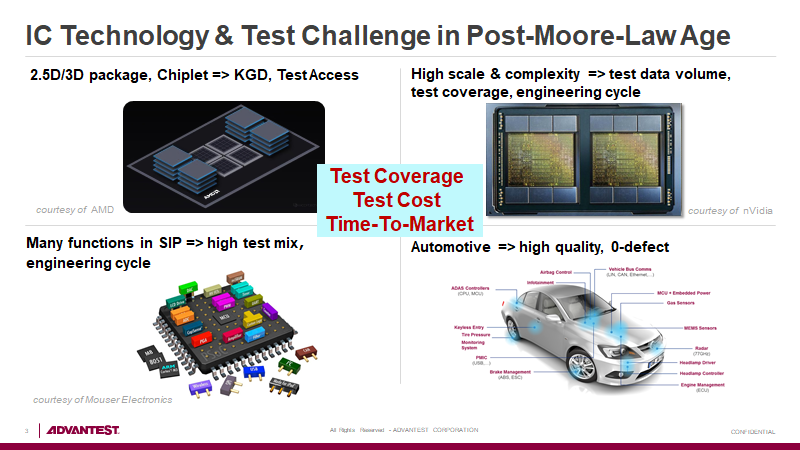

葛樑指出,芯片技术的发展进入后摩尔时代,更多的应用市场在同时推动半导体技术的发展,“这是一个技术融合汇聚的时代,摩尔定律已经不再是唯一的发展方向。”

先进封装技术是后摩尔时代等其中一个重要方向。他举例,自动驾驶、元宇宙、数据中心等应用的背后是对高性能计算芯片(HPC)的需求越来越大。而对高性能计算芯片而言,2.5D/3D封装等先进封装技术已经是标配,它通过芯片的堆叠以及横向的纵向堆叠,把好几颗芯片放在一个package里面,实现更好的性能和更优的成本。

但这些都对测试提出新挑战。葛樑介绍,首先,2.5D/3D芯片堆叠技术等先进封装技术带来的高集成度是的复杂度大大提升,而IC测试要保证Package里所有的Die都是KGD(Know good die,已知合格芯片),就意味着在晶圆级测试阶段,就需要非常高的测试覆盖率。另外,由于2.5D/3D封装中将原来芯片之间在PCB板级的连接放到了封装级,这对测试需要的对芯片的访问能力也造成了一些变化。

其次,由于先进封装技术使得在同一个封装里面的芯片规模前所未有地上升,比如用于服务器的GPU芯片的晶体管规模直冲千亿级,并且在整个封装里面不管是Die的数量还是IP核的数量也都大大增加。葛樑指出,这对测试而言意味着测试数据量的猛增,同时也对测试覆盖能力提出挑战,相应的测试方案开发周期也会更长。

葛樑还特别提到,随着汽车智能化、电动化的推进,越来越多种类的芯片开始进入车内,而汽车芯片的测试比消费类和工业类芯片在质量和可靠性要求要严苛得多,对于芯片提出零缺陷(0-defect)的要求。这就要求测试有非常高的稳定性和覆盖率,可以保证把所有有缺陷的芯片都过滤出来。

葛樑认为,这些新技术趋势下对IC测试提出的挑战,归结起来主要是,芯片集成度、复杂度和质量要求的提升要求测试覆盖率的提升,同时又无可避免会推高测试成本,测试方案开发周期也相应拉长从而会影响产品上市时间,因而在如何在提升覆盖率的同时,平衡好测试成本以及产品上市时间周期,是IC测试厂商面临的主要挑战。

应对挑战 IC测试厂商如何不断创新?

那么IC测试厂商具体要如何创新技术和方案,来满足这纷繁复杂的多元应用时代所带来的测试需求的复杂化?

首先的提高测试覆盖率。葛樑介绍,目前业内的测试解决方案主要从结构化测试、功能测试、模拟测试3个领域着手。

结构化测试,针对的是芯片内部制造缺陷。结构化测试里面最常用的就是Scan测试。2.5D和3D封装技术让Scan 接口的引脚数受限。这迫使Scan传输从原本的大量但低速的IO通道向更少的引脚数更大带宽发展。例如通过内部MUX(multiplexer,多路复用器)的方式让给原本传输率100M提升到 200,400,或800M。或者进一步,通过高速接口(HSIO)的技术让传输测试向量,速度能够提升到几个Gbps。

“这些芯片结构的改变对ATE测试设备来说,意味着要求更高的速度和更大的测试向量存储能力。” 葛樑指出。

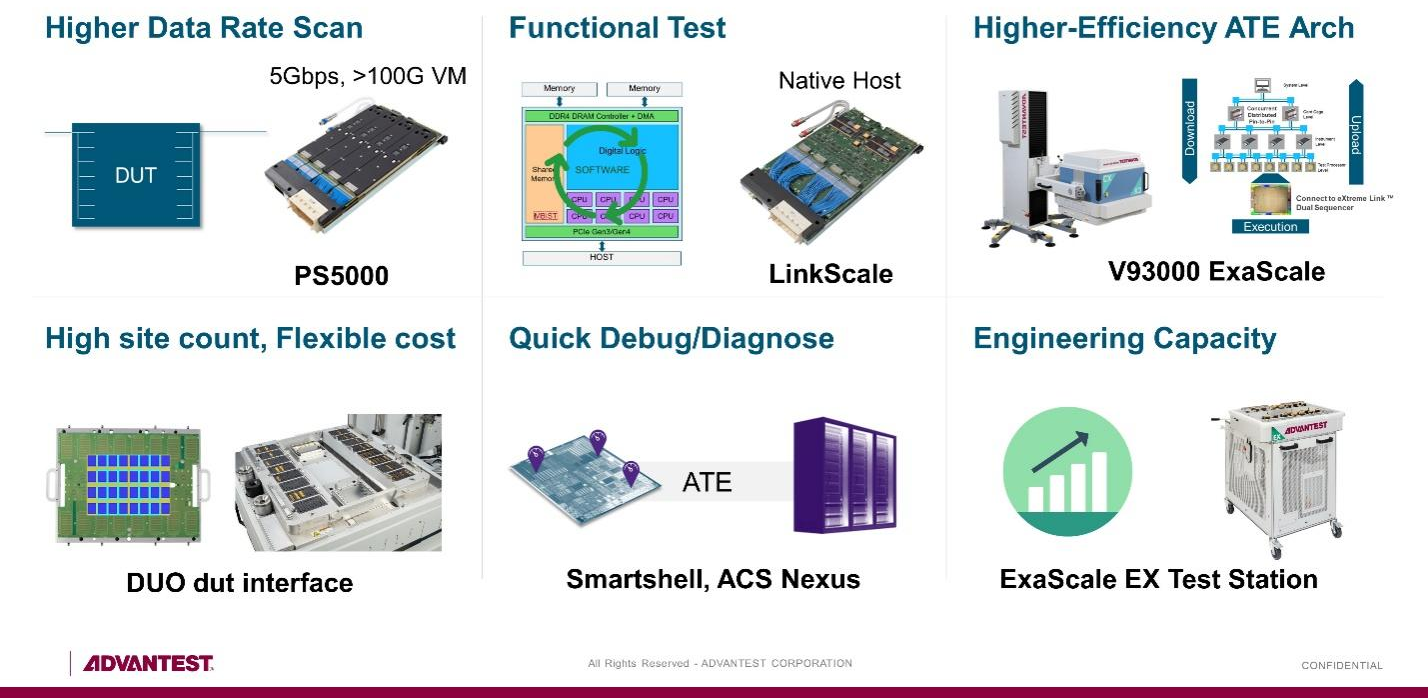

针对此,爱德万测试在去年推出的新一代V93000 EXA Scale平台,能够轻松应对目前市面上所有主流的AI,HPC芯片的测试需求。随平台发布新的通用数字板卡 PS5000,提供了最大5Gbps的速度和远超100G以上的测试向量存储能力,非常好的支持了包含Scan-Over-HSIO在内新的Scan接口技术。满足了未来Scan 测试演进的要求。”

葛樑也同时提到,结构化测试虽然能在单核层面做到高缺陷覆盖率,但无法完全覆盖多核多die交互的部分。而系统级测试,是对芯片在其应用工作模式下的功能测试,正好可以补充。对于2.5D/3D封装的情况,需要在CP的时候增加系统级功能测试,提高测试覆盖率,保证KGD。

据介绍,爱德万测试在去年推出的Link Scale板卡,是业界的一款创新的测试仪器,这块板卡里面装有内建了完整的主控能力可以通过高速接口和Device进行交互。通过Link Scake在ATE设备中加入面向系统级的测试功能,满足了更复杂芯片在CP、FT 中进行功能测试的需求。

模拟测试,这里我们说的是各种非数字测试,比如电源,混合信号,射频,等等。针对模拟功能越来越多的SIP,需要在最少测试次数下更快的实现所有不同的模拟测试。V93000,作为业内测试能力覆盖最广的机台,一站式的解决SIP里面所有不同类型的模拟测试需求。

不过测试覆盖率的提高以及复杂度的提示,势必推高测试成本和拉长测试周期。那么如何通过创新手段来控制成本?这对ATE的架构提出哪些要求?

葛樑指出,第一是要提升ATE的效率,来降低芯片测试的时间;第二是要让ATE能够支持更高的并测数,这样就可能降低单颗芯片的测试成本。

基于上述要求,爱德万测试新一代的V93000 Exa Scale除了加入新板卡之外,其整个总线结构也是全新的,内部总线高速网络的带宽达到几十个Gbps,使数据下载时间减少了40%,上传速度提升了好几倍,其架构优化使测试时间可以额外再减少8%~10%,整体上大幅优化了测试时间和效率。

并测数方面,V93000 Exa Scale平台的全新的DUO Dut Interface,可以对两种不同大小芯片测试板(Dut Board)进行一键切换,满足不同场景下多site并测的需求。

除了测试设备的性能对于测试成本的影响,测试环境的搭建成本也是目前产业内比较关注的点。如何帮助客户可以在有限场地和资金条件下,提高其工程开发的能力,达到快速上市的要求。“爱德万测试在V93000平台上推出了EX工程测试站。其娇小的体积,可以在同样的面积下面放置4倍的机台数,并实现同普通V93000平台同样的能力。同时可以搭配同样小巧的工程handler,也可以做到自动化的运行。”

挖掘测试数据的价值,打通前后道数据

葛樑指出,随着芯片技术的发展,IC测试厂商的角色也在不断转变,并且进一步向产业链两端延伸扩展。

“传统上ATE的角色更多是扮演量产的角色,但现在测试需要往设计端多走一步。”葛樑举例,比如用ATE来进行design validation,打通ATE设备和EDA软件,同时和EDA以及设计厂商密切合作,共同开发新的测试方案。比如V93000 Smartshell 就可以和EDA debug工具联动,在V93000上实现

对芯片内部IJTAG网络和IP的访问和调试。

同时,葛樑还指出,在芯片生产过程中产生的大量测试数据对芯片的工艺、设计、测试都有很高的挖掘价值,因为这不仅可以带来测试效率的提升,保证产品良率,更能通过数据分析优化芯片设计和测试方案,控制成本。“将ATE上的数据和半导体前道后道的数据打通,找到互相之间的关联性,并且能够挖掘出更大的价值反馈到芯片设计和制造上,也是最近业内很重视的方面。”

通过云计算、AI、机器学习等先进技术,挖掘半导体测试的数据价值和潜力,也是下一个产业聚集的重要趋势。

过去一两年来,爱德万测试在数据分析、云端布局方面做了很多创新探索。比如,Advantest ACS测试方案中的ACS Nexus和 ACS TE-Cloud,前者ACS Nexus提供了实时的数据接口,其他的第三方的分析工具可以接入并做出各个角度的数据分析。后者ACS TE-Cloud(Test Engineering Cloud)云平台服务,作为一站式的在线测试平台,客户不仅可以通过网页登入进行offline的测试程序开发,爱德万测试还整合了各个合作伙伴的测试资源,为客户提供完整的online测试程序开发环境,以及全方位测试外包服。

后摩尔时代的ATE厂家要如何通过创新来应对这纷繁复杂的应用时代所带来的一系列测试挑战。针对不同场景下的测试需求,通过软硬件的创新乃至测试流程的改善为用户提供全方位,多样化的测试解决方案。同时高速迭代的应用市场使得ATE厂商需要有长远化的技术判断力和洞察力。爱德万测试给我们提供了一个很好的方向,针对不同的测试场景和需求都有其对应的解决方案,真正做到点到点的测试覆盖。

后摩尔时代的IC技术将如何发展,ATE设备又将需要怎样的创新?创意不停,创新不止。