讨论要点

- 从SAN存储池化到CXL内存池化

- CXL的应用范围有多大?

- 内存分层:没有了PMem,CXL DRAM会便宜吗?

- CXL内存厂商:SMDK、HMSDK这些如何形成生态合力?

在Intel提出放弃3D XPoint Memory和Optane时,我看到新闻里有人提出CXL对前者的冲击。其实对这一点我不太认同,我反而认为SCM(存储级内存)和CXL更多是互补的关系,具体在下文中会有讨论。

不过CXL方面确实传来好消息:继Gen-Z并入之后,由IBM和AMD牵头的OpenCAPI一致性内存访问技术,连同OMI串行内存也宣布将资产转移至CXL财团。

Intel和AMD即将发布的下一代多路服务器平台,都将支持PCIe 5.0和CXL。这里我也感谢下MemVerge,近日美国FMS闪存峰会上的CXL FORUM论坛的ppt和视频,已经分享在https://memverge.com/cxl-forum。同时为了方便墙内的朋友,我也传到了下面的网盘:

链接:https://pan.baidu.com/s/1UeKhsgsYqwA71YxI65TxCQ?pwd=uxwm

提取码:uxwm

背景阅读《CXL、GenZ、CCIX架构以及未来的PM、内存和SSD形态》

《_AMD EPYC Genoa‘7004’:若DDR5换OMI,CXL.mem服务器内存池化_》

从SAN存储池化到CXL内存池化

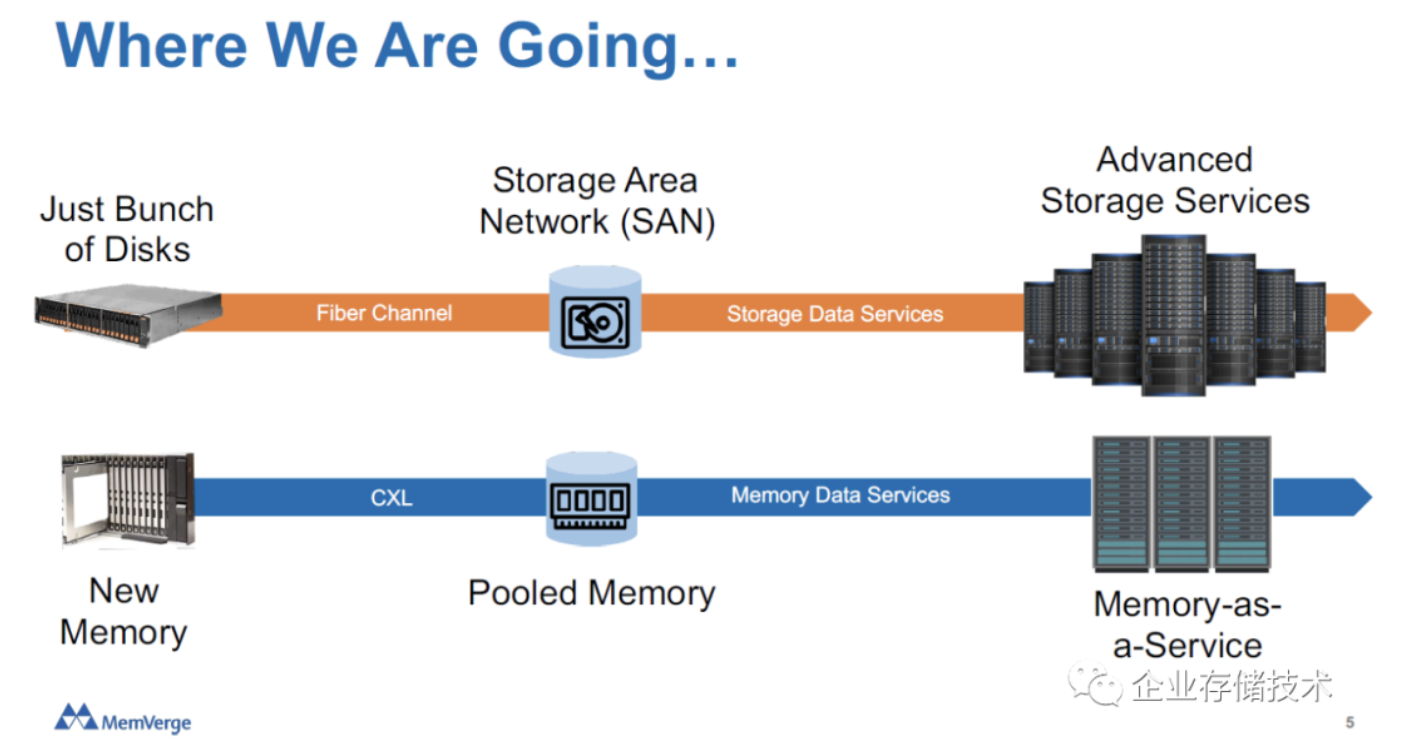

在一周之前国内的闪存峰会上,Charles Fan先生就在他的分享中提到了30年前出现的光纤通道和SAN存储网络。当时我还没仔细思考,这次也是看到AMD的ppt中的以下几张图,有了同感。

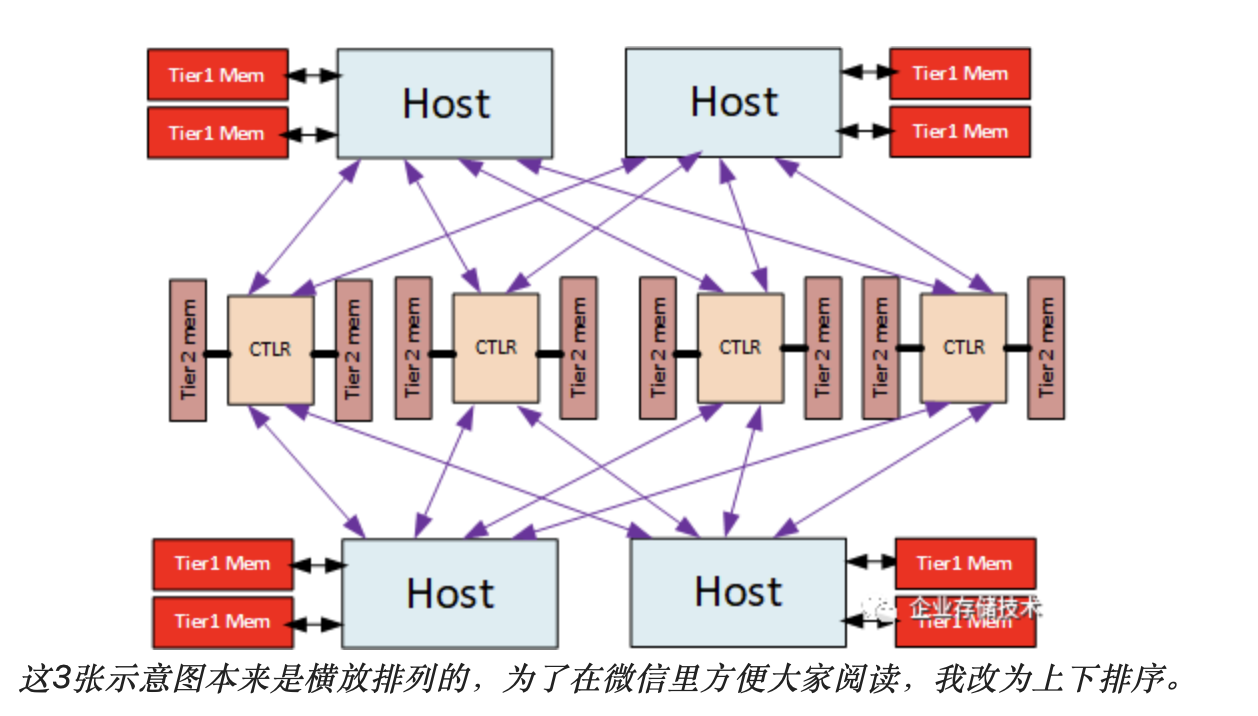

这3张示意图本来是横放排列的,为了在微信里方便大家阅读,我改为上下排序。

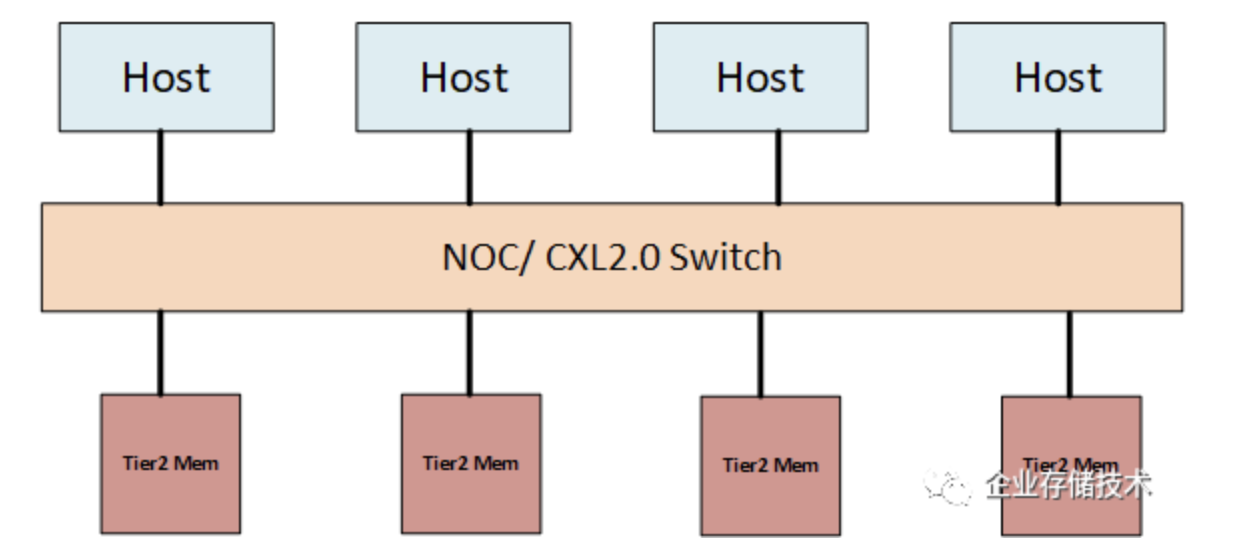

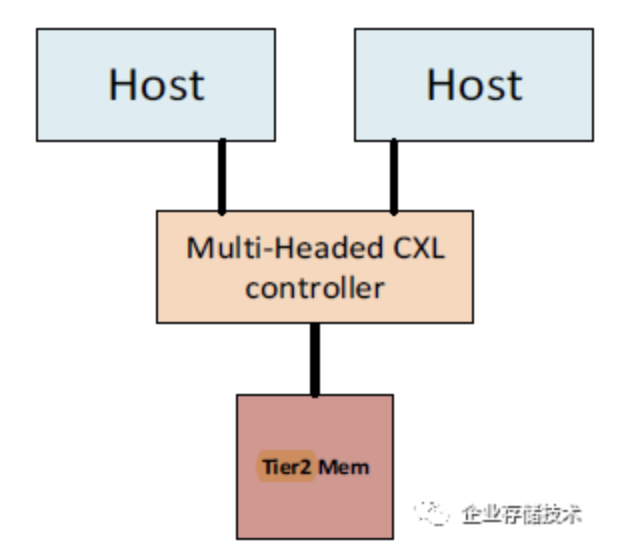

上图位于中间的CTLR,应该就是服务器外部机箱里的CXL内存控制器。这有点像DAS共享存储阵列的连接方式,4台主机可以同时连接到每个CTLR;如果换成20-30年前,还是服务器到盘阵RAID控制器之间的SCSI连线,当时典型的用途是双机热备集群。

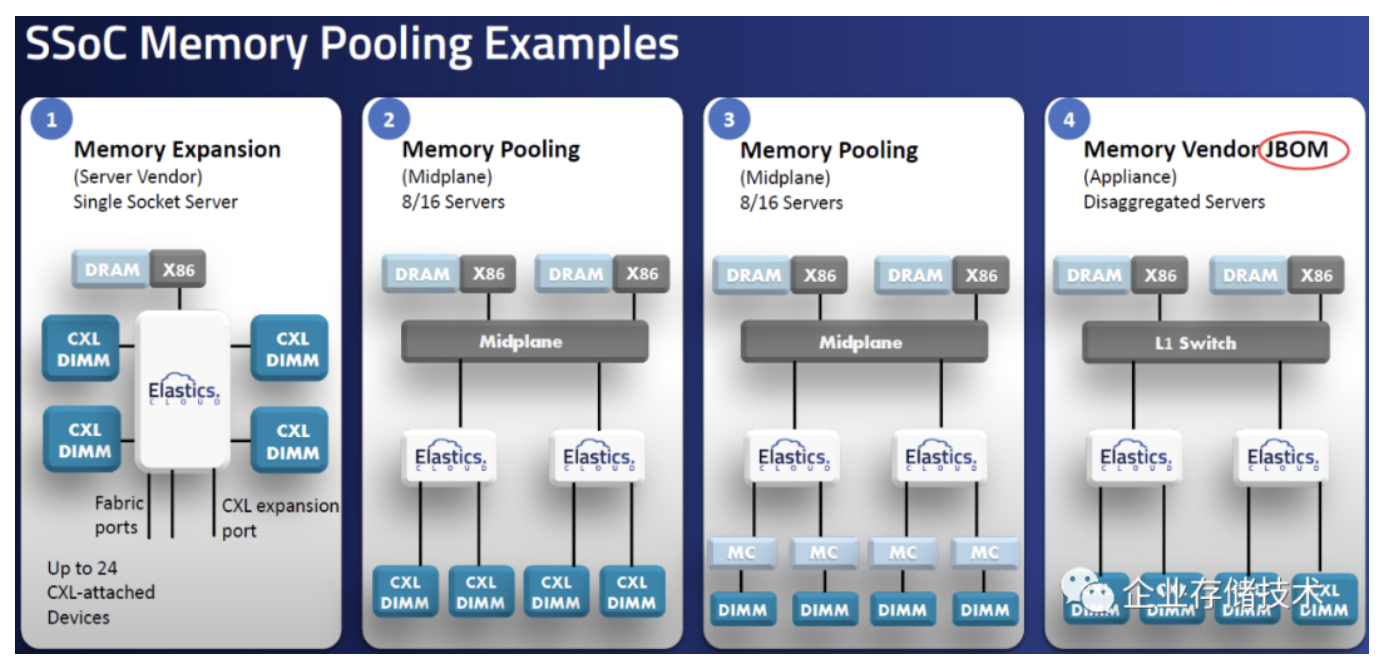

当服务器和CXL外部内存模块,通过CXL 2.0 Switch互连到一起时,是不是就有点SAN的感觉了。

第三种拓扑我没有重点研究,有点像曾经的MR-IOV?

而在一家做CXL ASIC(SSoC)的公司Elastics Cloud分享中,更是提出了JBOM的概念。大家都知道JBOD(Just Bundle of Disk)和JBOF(Flash闪存)吧,JBOM就是针对内存了。

CXL的应用范围有多大?

前面刚提到了CXL的资源共享和池化。传统存储网络强调的是高可用、磁盘/SSD也都是非易失介质外加RAID/镜像副本冗余保护;可相比之下内存池化不具备这些,原本支持持久化的Intel傲腾还停掉了。这样我们就要去看看别的方面价值。

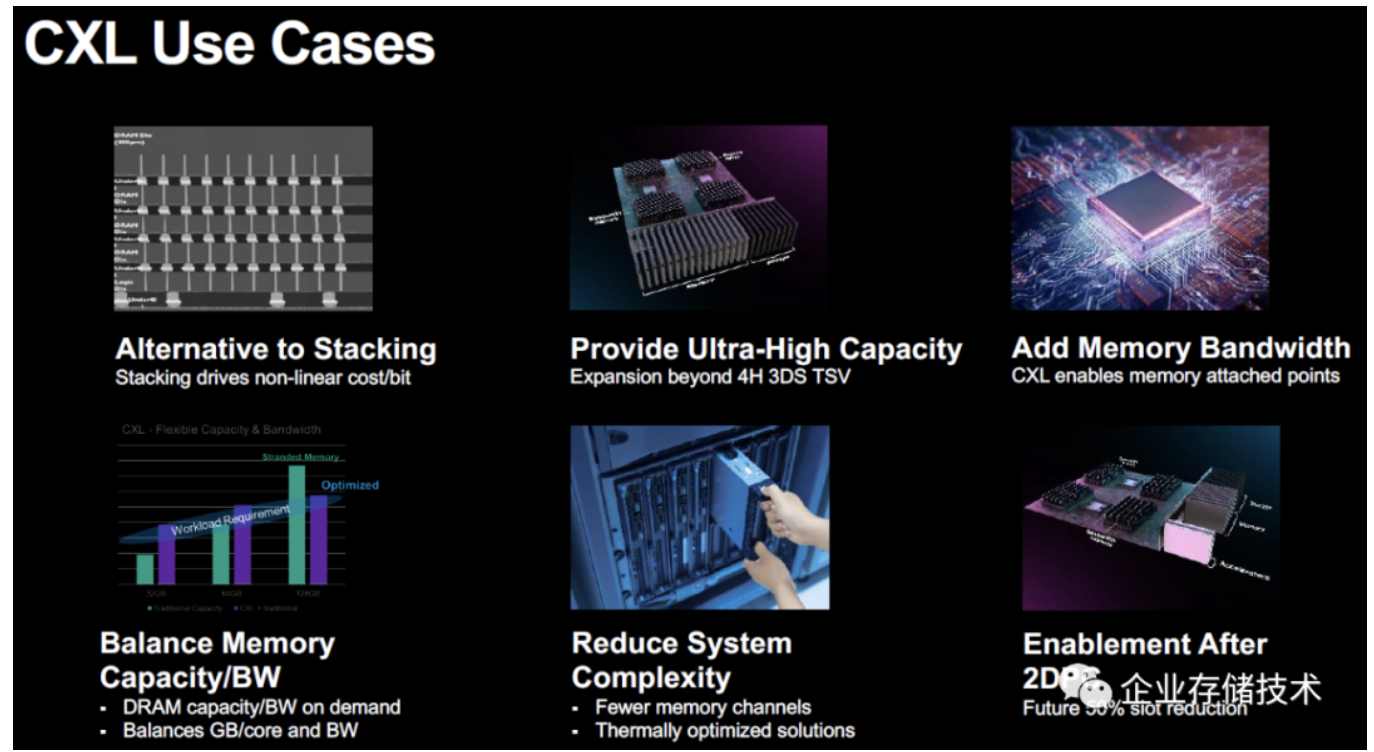

Micron的分享中列出上图。似乎除了扩展内存容量、带宽,就是容量/带宽一起均衡扩展。还是要看具体的应用场景,比如Redis、Spark等。

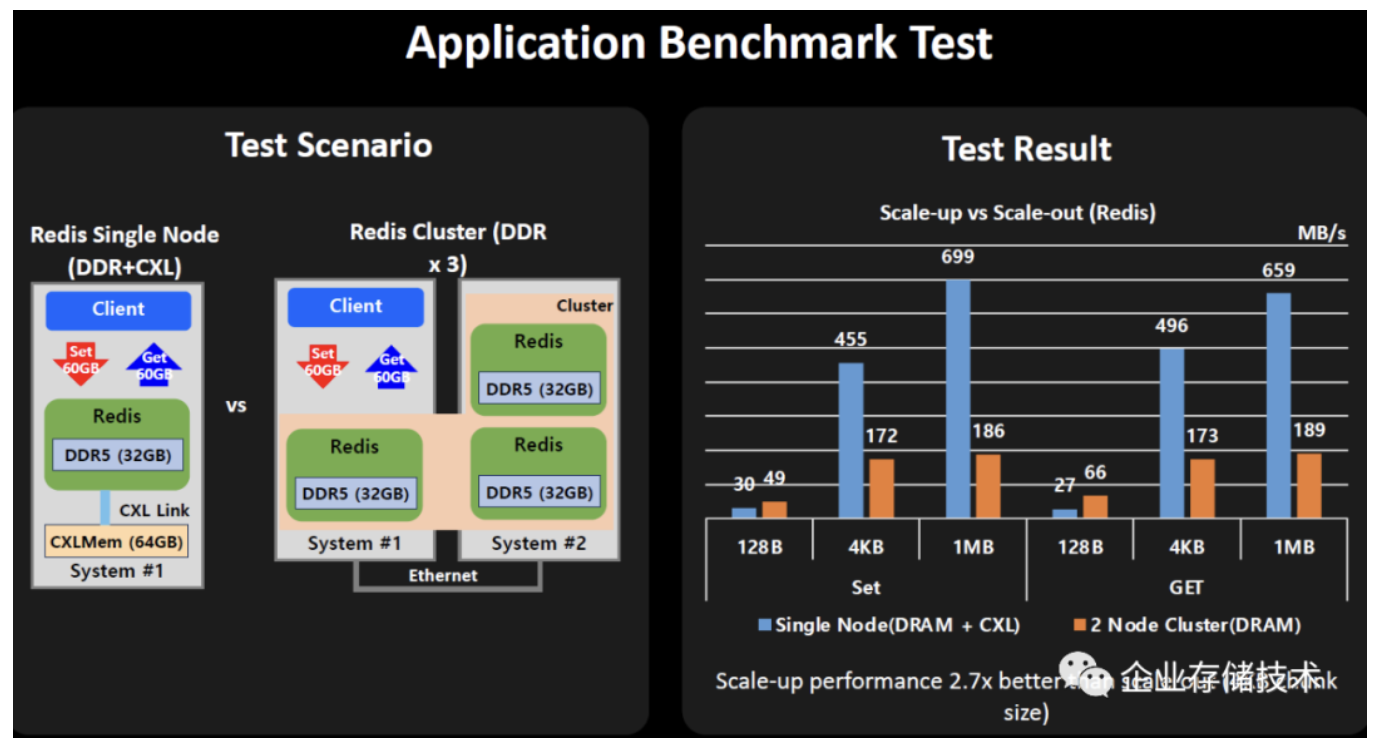

上图引用自三星的ppt。之前Optane DIMM持久内存也把Redis缓存服务器看成重点应用,并利用比DRAM内存的价格优势来提高性价比。而CXL与Redis的结合点在于单节点大内存(SAP HANA是不是也需要这个?)测试数据反映出,以前需要多个节点达到的内存(缓存)总容量,如果由一个节点实现,在进行4KB和1MB较大的Set和Get Key-Value操作时,带宽可提高很多。估计是减少了网络传输开销吧。

这个是不是由Scale-out转向Scale-up了?与此同时,缓存的单点失效风险也集中了吧。

内存分层:没有了PMem,CXL DRAM会便宜吗?

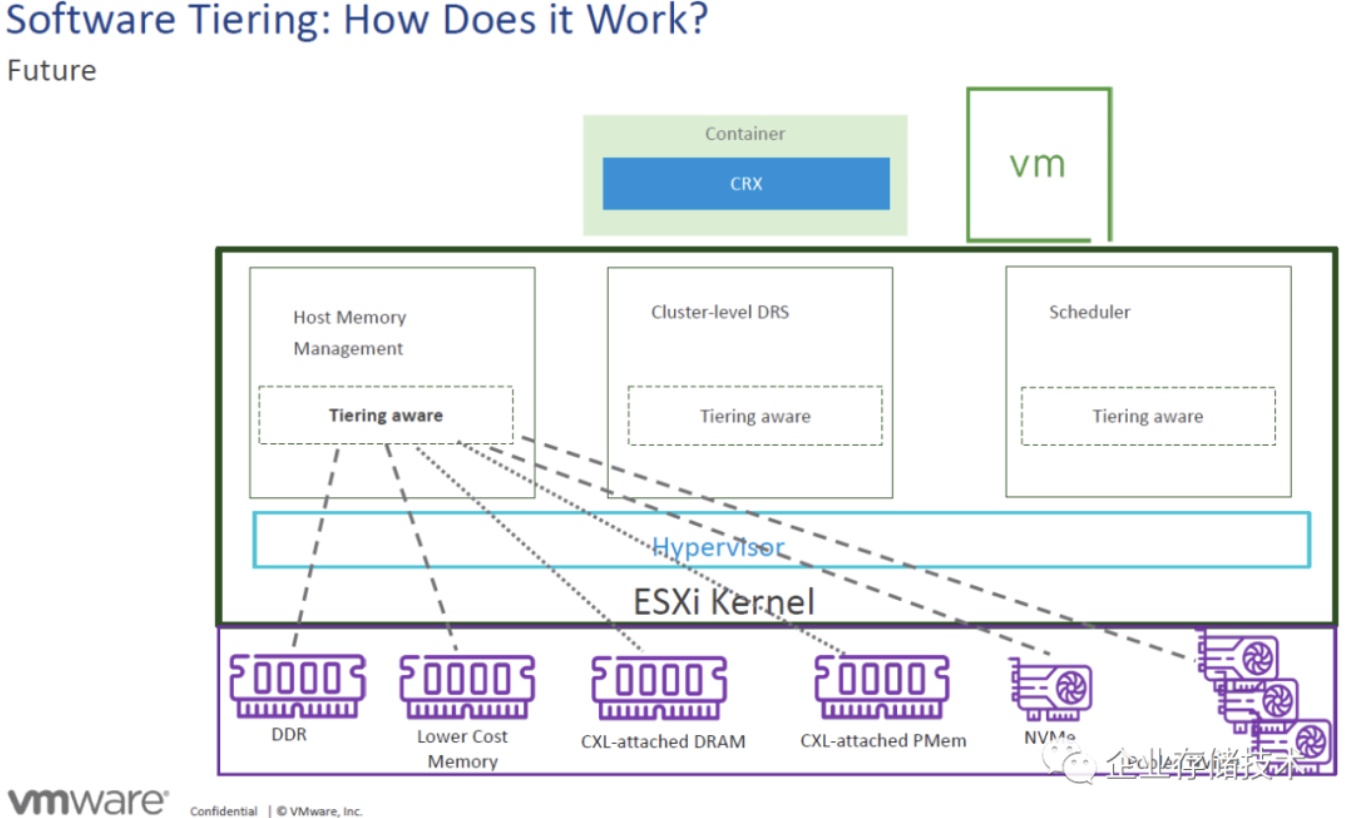

上图来自VMware的分享。首先对于这里的Lower Cost Memory我不是很清楚;其次CXL-attached PMem在Optane DIMM退出之后前景暂时不明。那么对于CXL DRAM来说,比传统DIMM内存条还要增加一颗控制器,价格肯定更贵啊,这里的内存分层怎么降低成本呢?

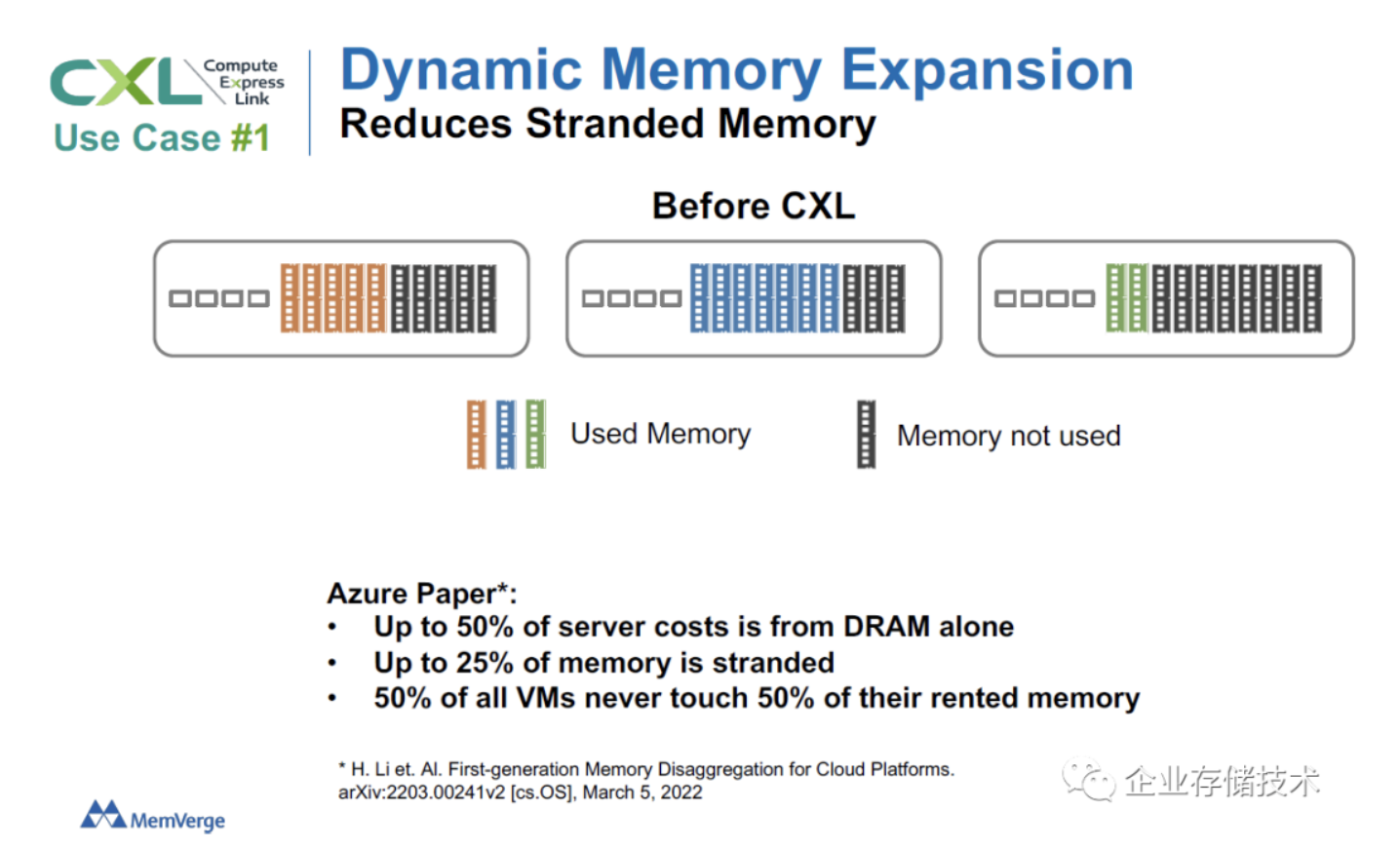

MemVerge提出的服务器内存超配这一点,我倒是认同的。在业务规划时,由于不确定因素,较多时候只能按可能性的上限来申请内存硬件。如果池化到外部机箱之后,在不同主机之间重新分配内存就灵活多了。

CXL内存厂商:SMDK、HMSDK这些如何形成生态合力?

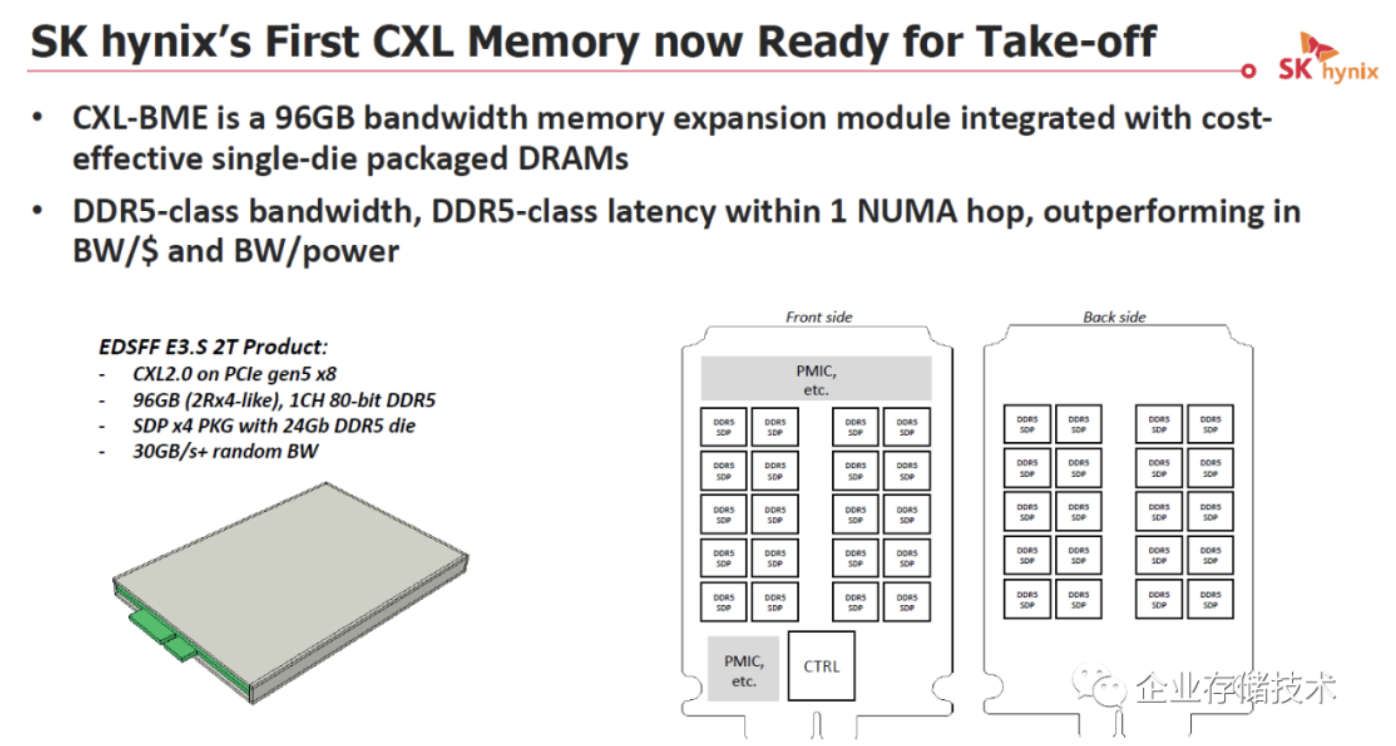

就在三星可以提供最高512GB的CXL DDR5模组之后,SK Hynix宣布的96GB容量CXL 2.0内存倒显得并不突出。EDSFF E3.S的物理接口也是PCIe Gen5 x8,单通道80-bit DDR5相当于2个32+8(ECC)子通道。之前我在《移动工作站DDR5__内存频率之殇:怎么破?》里介绍过的都是16Gb DDR5颗粒,这里提高到24Gb,在PCB正反两面各有20个DDR5内存芯片。

扩展阅读:《DDR5__支持On-die ECC__,但为什么服务器内存价格会提高?》

如果增加E3.S的厚度,放多块PCB不是不能把容量做大,但价格也会像内存一样感人,反而不如多插几个模组提高带宽?

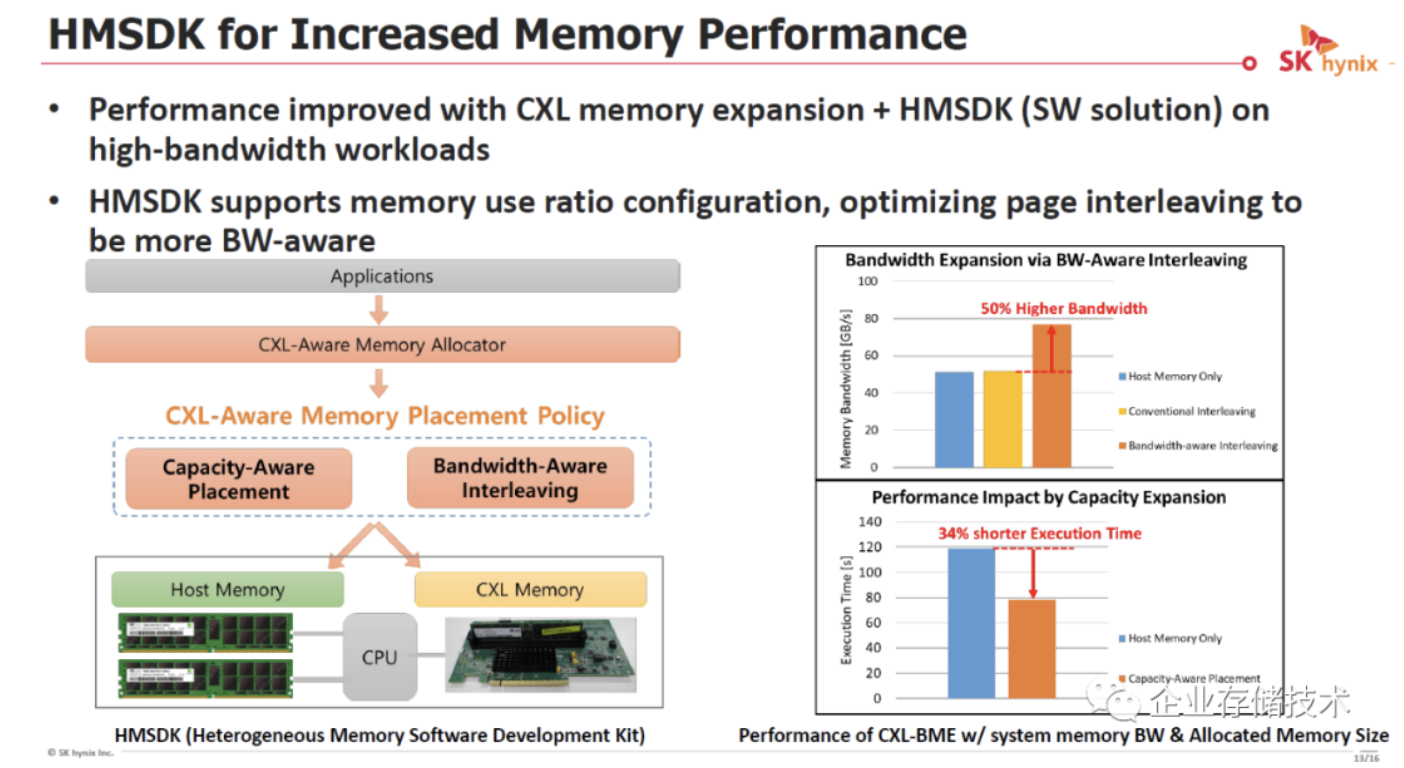

以前我提到过三星为CXL内存准备的SMDK(Scalable Memory Development Kit),Hynix也搞了类似的HMSDK。对于硬件厂商来说,想附加软件提供更完整的解决方案,这个心情我特别理解。但对于开发者来说,如果不同品牌CXL内存还要学习各自的管理软件,会不会有点头疼呢,如果大家联合贡献一个开源项目是不是更好?

小结

总之,在今天CXL众人拾柴的局面下,我却有点谨慎的乐观。无论如何,CXL不会像Optane那样“失败”,因为它与PCIe控制器在硬件上融为一体,可以说只有研发成本而没有像存储器芯片那样的制造成本。受限于我的知识面和水平,不知DPU等能否让CXL有更大的用武之地?

就先写这么多吧,这两天我生了点病还在恢复中,文字质量如果欠佳请读者朋友见谅。

扩展阅读:《_企业存储技术》文章分类索引(微信公众号专辑)_》

注:本文只代表作者个人观点,与任何组织机构无关,如有错误和不足之处欢迎在留言中批评指正。如果您想在这个公众号上分享自己的技术干货,也欢迎联系我:)

作者: 唐僧 huangliang

原文:企业存储技术

推荐阅读

欢迎关注企业存储技术极术专栏, 欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。