在数字经济时代,数据成为新的生产要素,围绕数据处理分析的计算能力成为新的生产力,广泛应用于千行百业的智能转型升级中。我国的云数据中心作为数字化基础设施的核心节点,得到了飞速发展。

益企研究院自 2018 年发起“数字中国万里行”以来,见证了国内云数据中心在快速成长过程中的持续演进。在数据中心基础设施层面, 新基建、双碳、东数西算,每年都有新热点,背后的指导思想则是一以贯之,兼顾效率与均衡、可持续的发展。

数据中心内部同样在经历类似的进化,以GPU为代表的加速器应用 越来越广泛,作为通用算力输出单元的 CPU 也走向多元化: x86 阵营 AMD 东山再起,Arm 阵营百花齐放。对云服务商而言,一方面需要 CPU 有更强的核心和更多的核心数,另一方面需要不同的 CPU 满足客户多元化细分场景的需求,都与效率有着密不可分的关系。相应的,AMD、Arm 等芯片厂商的新技术新架构日益赢得云服务商的广泛认可,并根据自身业务发展针对性的定制和优化。与此同时,在自主可控的大潮推动下,中国“芯”力量正在崛起,产品的技术 成熟度和应用范围正在追赶主流。

国际数据公司(IDC) 的 2021 年第四季度中国服务器市场追踪报告也指出,中国市场对 AMD 和 Arm 服务器的需求正逐渐增加。其中,互联网行业拥抱 AMD 服务器最为积极,占总出货量的 80% 以上;Arm 服务器的主要行业是政府和电信,预计到 2022 年,互联网和其他行业将更多地采用 Arm 服务器。

概述:花开两朵

用先后在 AMD、苹果、英特尔(Intel)参与或领导过多个大型芯片 项目的Jim Keller 的话说, x86、Arm 和 RISC-V,在诞生之初,都是“简单而干净”的。只是随着时间的推移,这些指令集架构(Instruction Set Architecture,ISA)会不可避免地走向复杂。

复杂,通常意味着更强大,和相对不那么高效。

以 64 位为例,x86 比 Arm 要早上十年左右,而超线程技术(Hyper- Threading Technology,简写为 HT 或 HTT) 的产品化甚至还先于 64 位(x86)。多年累积下来,以单个 CPU 核心计,x86 比 Arm 更复杂,是正常现象。

x86 的超线程是 1 核心 2 线程,简单地说,1 个物理核心可以当作 2 个逻辑核心使用。所以 64 核的 AMD EPYC(霄龙)系列 CPU,有 128 个线程,从云主机的角度,和 128(物理) 核的 Ampere Altra Max 一样能提供 128 个(逻辑)核。孤立的来看,1 个物理核出来的 2 个逻辑核,算力应当不如 2 个独立的物理核,而且二者间的共 享资源还会带来安全隐患;但放到全局视角,“真 ·核多”要把多一倍的核心有效的连为一体,对片上互连架构和资源的要求也更高。

制程之争

2016 年英特尔推出最后一代至强 E5/E7(v4) ,是其首批采用 14nm 制程的服务器 CPU。2017 年,AMD 以代号 Naples 的第一代 EPYC 处理器重返服务器 CPU 市场,制程也是14nm。随着核数的增加, 同期问世的第一代至强可扩展处理器(代号 Skylake-SP) ,最大热设计功耗(Thermal Design Power,TDP)率先突破 200W(瓦)。

随后,英特尔转产 10nm 不利,采用代工生产的 AMD 则在台积 电(TSMC) 的帮助下, 成功过渡到 7nm 制程。Arm CPU 也受惠于代工模 式,Ampere(安晟培 ) 的 Altra 和 Altra Max,AWS 的 Graviton2,都采用台积电的 7nm 制程生产。

现在,更新一代的 Arm CPU,如 AWS 的 Graviton3 和阿里云的倚天710,已经用上了 5nm 制程。随着代工厂的持续迭代,采用 3nm 制程的 CPU 也为期不远了。

不过,基于纳米(nm)的传统制程节点命名方法,已不再与晶体 管实际的栅极长度相对应。在这种情况下,在不同供应商的制程 之间单纯对比纳米数,并不能准确地反映实际情况。为了扭转在宣 传上不利的局面,英特尔在 2021 年 7 月下旬公布了“公司有史以来最详细的制程工艺和封装技术路线图”,改用“等效”的制程命名法,将此前的 10nm Enhance SuperFin 制程更 名为 Intel 7,用于 2022 年上半年量产的第四代至强可扩展处理器(代号 Sapphire Rapids);原先的 7nm 制程更名为 Intel 4, 此后还有 Intel 3、Intel 20A、Intel 18A 等。

架构与封装

半导体的制程工艺仍在进步,但已跟不上芯片规格提升的速度,所以各种不同层面的“堆料”手段越来越常见。

云计算供应商追求数据中心级别的规模和机柜级别的密度,四路和 八路等单机层面以较高难度“堆 CPU”的做法并不合潮流,双路服务器更受欢迎。

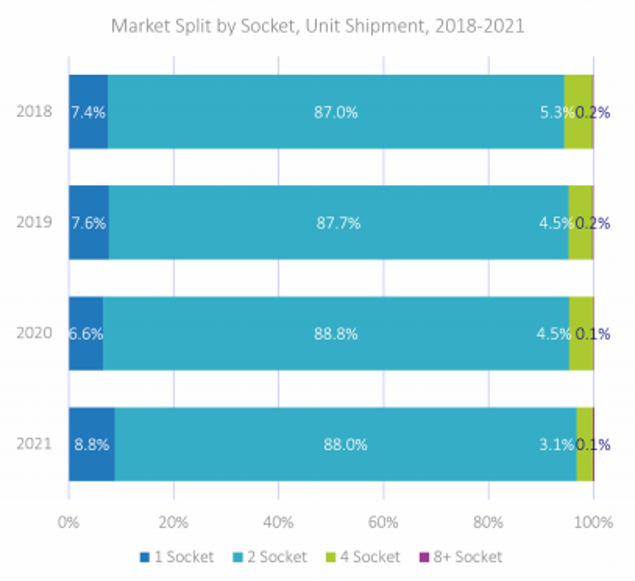

IDC 的数据显示:双路(2S) 的市场份额一直稳定在 88% 上下, 八路(8S) 和四路(4S)的市场一路降至不足 4%,空出的份额被单路(1S)占据,这要得益于AMD 和 Arm 处理器核数的增加(单路可替代低端双路)

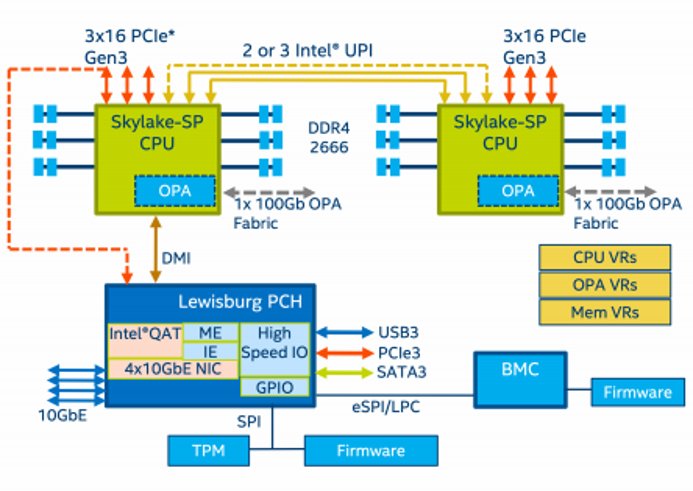

英特尔至强家族服务器 CPU 之间的互连采用专用通道,从至强 E5/ E7 时代的 QPI(Quick Path Interconnect) 到至强可扩展处理器的 UPI(Ultra Path Interconnect),数据带宽和效率更高、空闲功耗降低。以 2021 年推出的第三代至强可扩展处理器(代号 Ice Lake-SP) 为例, 两个 CPU 之间可以有多达 3 条 11.2GT/s 的 UPI 链路通信。

第一代至强可扩展(XeonScalable)平台就可以提供(可选的)第三条UPI

AMD 的 EPYC 家族服务器 CPU, 用 于 CPU 之间互连的 Infinity Fabric,与 PCIe 通道是复用的。也就是说,EPYC 7002/7003 系列虽然每 CPU 有 128 个 PCIe 4.0 通道,但在双 CPU 配置下,会各牺牲一定数量的 PCIe 通道用于连接彼此,所以能提供的 PCIe 通道总数可 达 162 个,仅比单路系统多四分之一强。

64 位 Arm CPU 的 CCIX 也有类似的现象,而 AWS 的三代 Graviton 处理器都采用单路方案。7nm 制程的 Graviton2 和 5nm 制程的 Graviton3 都是 64 核心(64 线程) ,但是后者的每个核更强,并升级到 DDR5 和 PCIe 5.0, 晶体管总数达 550 亿,几乎是前者的两倍。

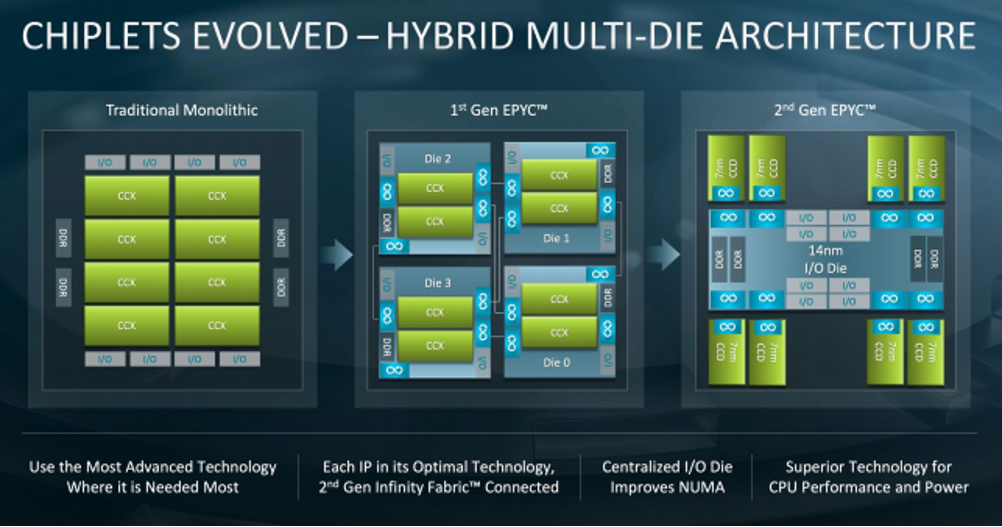

CPU 越来越复杂,为了保证制造的良率,将一个 CPU 拆分为多个较小的晶片(die)分别生产、最后互连、封装在一起的做法,逐渐普及开来。

第一二代 AMD EPYC处理器架构对比图

一种是对等均分,各晶片的成分一致,没有角色之分。第一代 EPYC 处理器由 4 个包含核心及其 Cache、片间互连的 CCD(Core Complex Die) 组成, 这种架构被称为多芯片模 块(multi-chip module,MCM)。

从四等分的角度来看,Sapphire Rapids 也可以归入此类。

另一种是按功能划分,生产、搭配更为灵活。AMD 代号 Rome 的第 二代 EPYC 处理器,采用被称为 Chiplet(小芯片)的架构,由 1 个 专用于互连的 IOD 和多达 8 个 CCD 组成,共 9 个晶片(1+8) 。通过调整 CCD 的数量,第二、三代 EPYC 处理器可以提供 8 ~ 64 个核心。

在代号 Milan 的第三代 EPYC 处理器上,AMD 和台积电还把 Chiplet 封装技术与芯片堆叠技术相结合,实现 3D V-Cache(3D 垂直缓存) , 推出 L3 Cache 容量高达 768MiB 的 Milan-X。

AWS 的 Graviton3 也采用了 I/O 与计算相分离的 Chiplet 设计,而在具体实现上几乎是 AMD 的“反面”:64 个核心组成的较大晶片居中,4 个 DDR(控制器)晶片和 2 个 PCIe(控制器)晶片三面环绕,共 7 个晶片(1+6)。Graviton3 是 AWS 自用的 CPU,不追求核心数量上的灵活性。

无论如何实现,Chiplet 已经是业界大势所趋。2022 年 3 月 2 日,日月光(ASE)、AMD、Arm、谷歌云、英特尔、Meta(Facebook) 、 微软、高通、三星和台积电,从领先的 CPU 供应商、代工厂到超大规模用户,共同发起小芯片互连标准UCIe(Universal Chiplet Interconnect Express),并公布了 1.0 规范。