【嘉勤点评】中芯北方发明的掺杂多晶硅栅极的半导体结构方案,将NFET区域和PFET区域的多晶硅栅极进行掺杂,降低了阈值电压和单位面积电阻,从而提高电学性能。同时,由于掺杂多晶硅栅极的是在半导体衬底中形成源极和漏极的同时进行的,因此也节约了工艺步骤。

集微网消息,随着半导体技术的不断发展,半导体技术已经渗透至生活中的各个领域,例如航空航天、医疗器械、手机通讯、人工智能等方方面面都已离不开半导体芯片。

以前很多芯片都是采用二氧化硅作为栅极介电质,但是,在半导体集成电路演变的过程中,功能密度急速增加。同时,几何尺寸不断缩小,让栅极介电质层继续缩短变薄的工艺复杂性、难度和制造成本剧增。另一方面,随着晶体管尺寸的不断缩小,源极和漏极之间的距离也越来越小,进而容易造成短沟道效应。

因此,HKMG(高介电金属栅)工艺被开发出来。其采用一种具有高介电常数(或称高K)的栅极介电层,并采用金属材料来作为栅极。采用HKMG工艺制备的器件相比较传统器件而言,极大地减小了漏电流,同时有效提升了驱动电流,因此HKMG成了目前高性能晶体管所采用的主流技术。

但是在采用后栅工艺的HKMG技术中,低压器件采用金属栅极,而加入的高压和中压器件仍然使用多晶硅栅极,由于高压和中压器件的栅极没有离子注入,NFET(N型场效应晶体管)和PFET(P型场效应晶体管)的阈值电压和单位面积电阻过高,会降低栅极的性能。

为解决上述问题,中芯北方在2020年4月10日申请了一项名为“半导体结构及其形成方法”的发明专利(申请号:202010277861.X),申请人为中芯北方集成电路制造(北京)有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项技术方案吧。

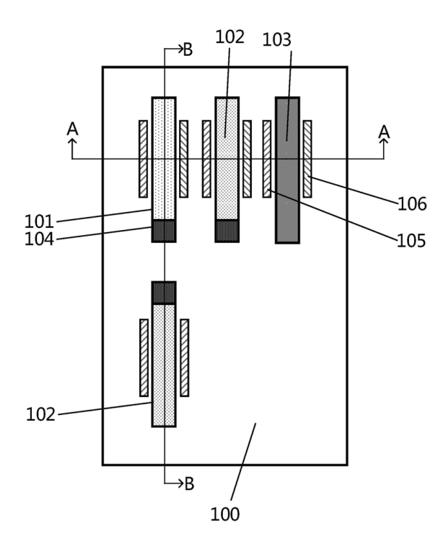

如上图,为该专利中发明的掺杂多晶硅栅极的半导体结构平面分布示意图,该半导体结构由半导体衬底100作为主要骨干,在半导体衬底上形成有NFET区域栅极101、PFET区域栅极102以及核心器件区域栅极103,此外还包括位于各栅极两侧的源极105、漏极106以及用于电连接上述栅极的金属互连结构104。

另外,上图中还指出了半导体结构在沟道长度方向和沟道宽度方向的截面图,其中,沟道长度方向的截面图指的是沿图中A-A方向的截面图,沟道宽度方向的截面图指的是沿图中B-B方向的截面图。

在HKMG的高压和中压器件中,由于NFET区域栅极和PFET区域栅极为未被掺杂的多晶硅栅极,并且多晶硅栅极下的TiN层厚度一般比较薄,因此NFET区域和PFET区域的阈值电压和单位面积电阻会过高,进而降低栅极性能。针对该问题,上述结构将NFET区域和PFET区域的多晶硅栅极进行掺杂,降低阈值电压和单位面积电阻,从而提高栅极的电学性能。

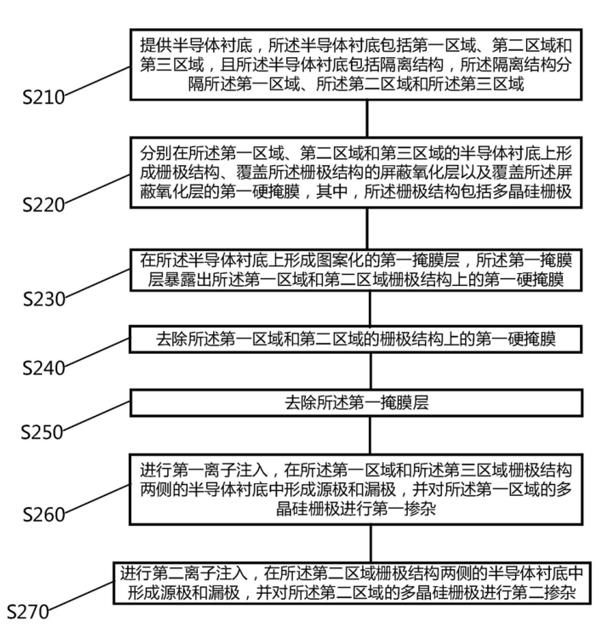

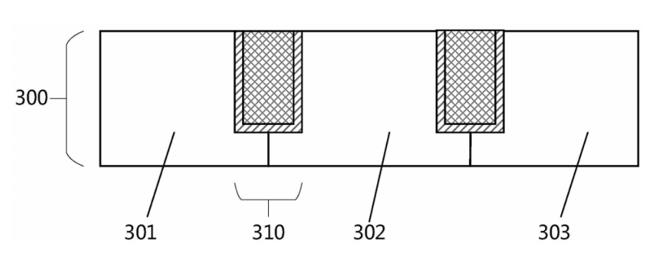

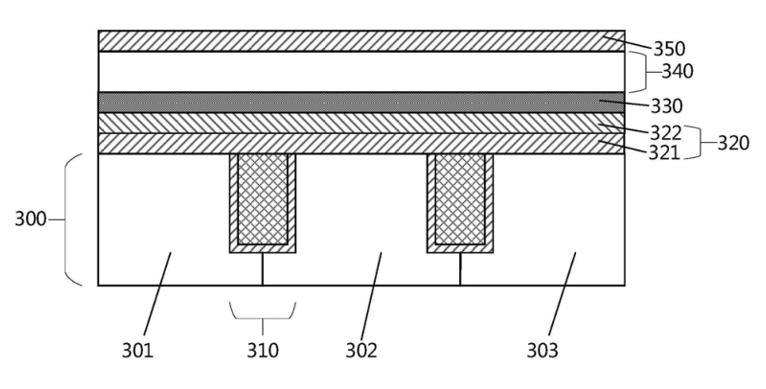

如上图,为该专利中发明的半导体结构形成方法的截面流程图,首先,在半导体衬底上形成第一区域(301)、第二区域(302)和第三区域(303),在半导体衬底上还设置有隔离结构(310),该结构将三个区域之间相互进行分割,如下图所示。

这三个区域分别承担着不同的任务,第一区域为高压或中压NFET器件区域,第二区域为高压或中压PFET器件区域,第三区域为核心器件区域。而栅极结构、覆盖栅极结构的屏蔽氧化层以及覆盖屏蔽氧化层的第一硬掩膜就分别设置在这三个区域上面,其中,栅极结构包括多晶硅栅极。

如上图,在半导体衬底和隔离结构上依次形成有栅介电层320、阻挡层330、多晶硅栅极340和屏蔽氧化层350。其次,在半导体衬底上形成图案化的第一掩膜层,第一掩膜层暴露出第一区域和第二区域栅极结构上的第一硬掩膜。接着,需要去除第一区域和第二区域的栅极结构上的第一硬掩膜。

最后,进行第一、第二离子的注入。该步骤会在第一区域和第三区域栅极结构两侧的半导体衬底中形成源极和漏极,并对第一区域的多晶硅栅极进行掺杂。同时,会在第二区域栅极结构两侧的半导体衬底中形成源极和漏极,并对第二区域的多晶硅栅极进行第二次掺杂。

以上就是中芯北方发明的掺杂多晶硅栅极的半导体结构方案,该方案将NFET区域和PFET区域的多晶硅栅极进行掺杂,降低了阈值电压和单位面积电阻,从而提高电学性能。同时,由于掺杂多晶硅栅极的是在半导体衬底中形成源极和漏极的同时进行的,因此也节约了工艺步骤。