本文以 KiCad v6.0 设计一个简单的 MM32F5277E9PV 的开发板为例,通过原理图讲述 MM32F5 硬件系统设计,中间会提到一些电路设计中遇到的问题,供大家参考。

最小系统设计

最小系统是 MM32F5 能够工作的电路设计,包括 MM32F5 系列的芯片,去耦电容,复位电路,外部时钟电路(可选)以及电源。

元件绘制

首先,我们需要绘制一个名为 MM32F5277E9PV 的元件,绘制元件的信息来自于该芯片的产品手册,可在灵动官网中查看。

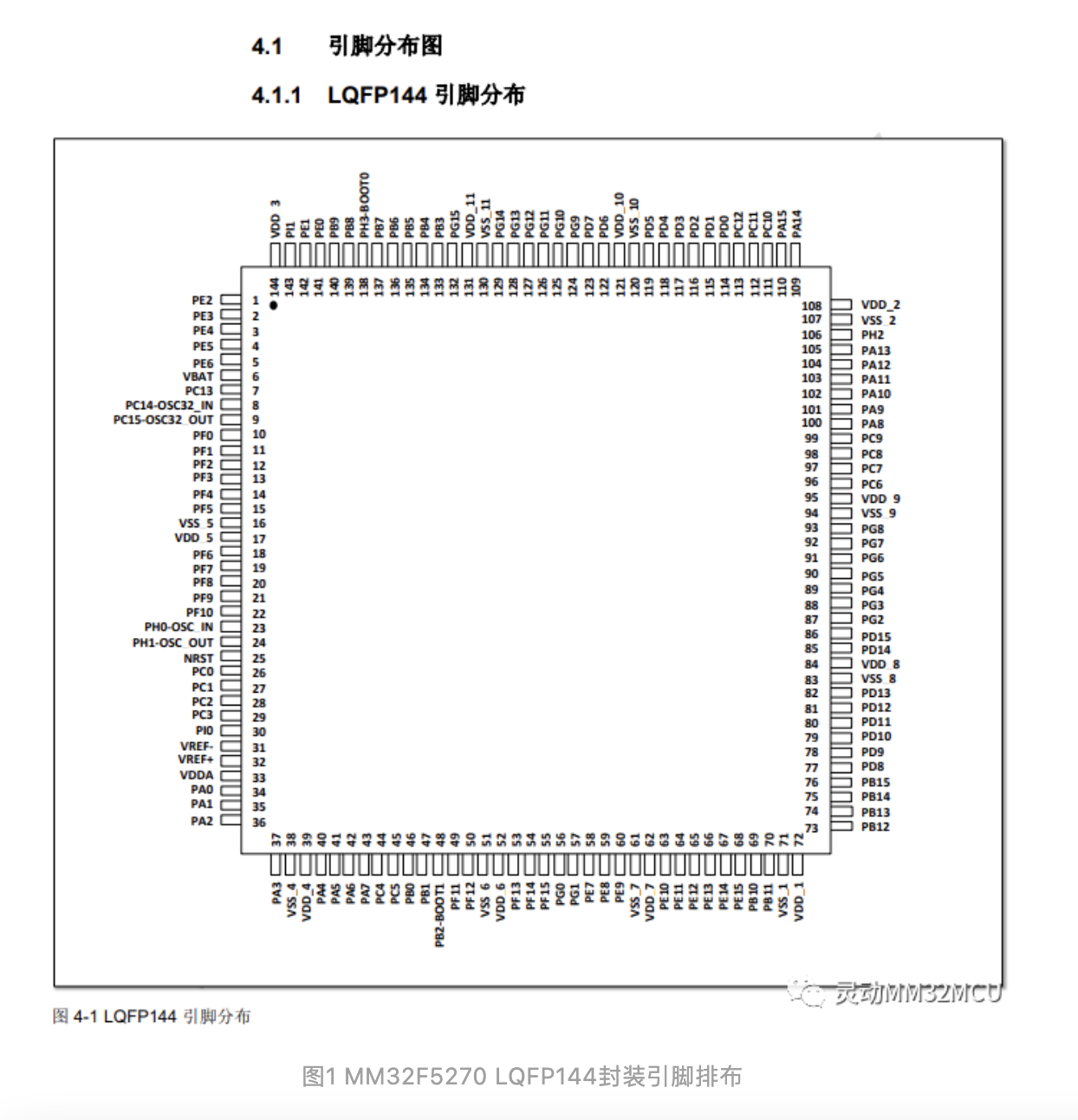

在 “引脚定义及复用功能” 章节中,通过引脚分布图可以直观看到不同封装芯片的引脚分布情况(图1),或者是通过引脚定义表,查看引脚功能和序号。

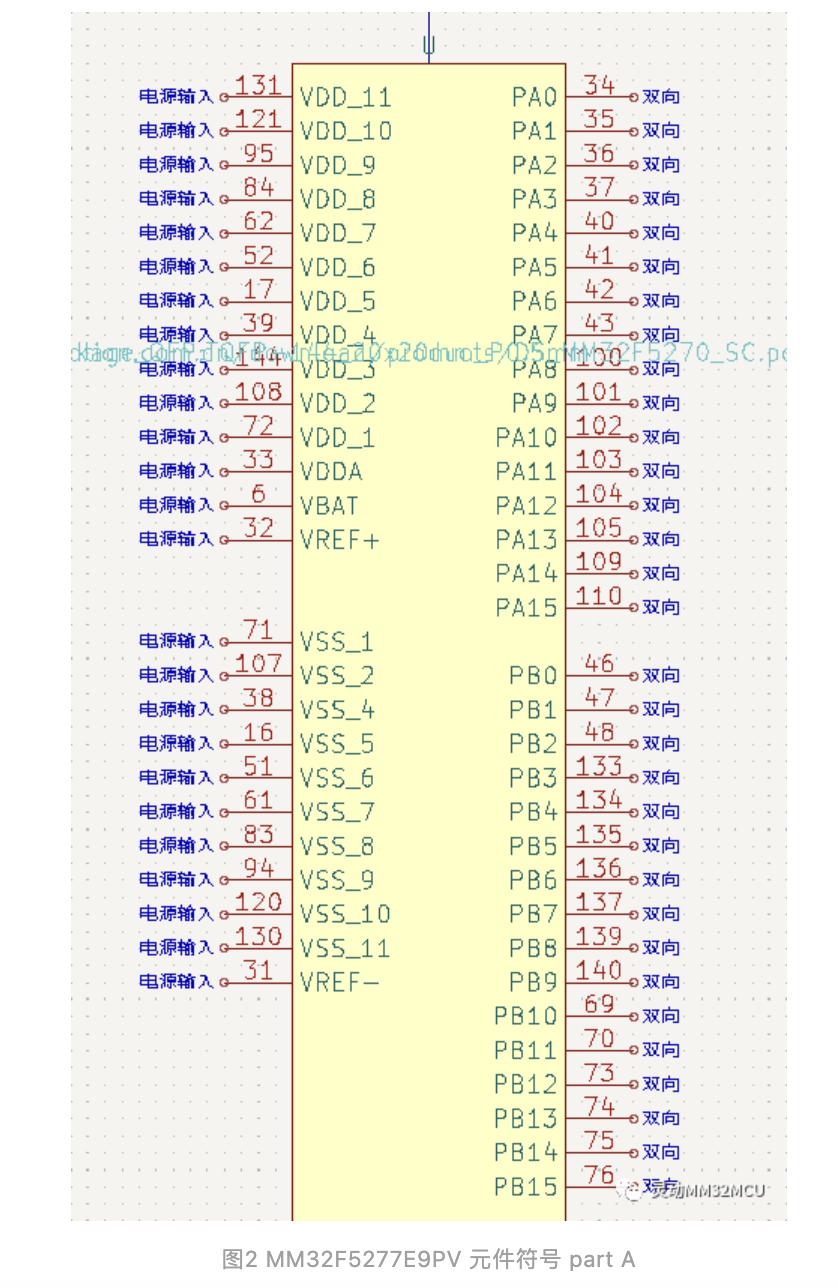

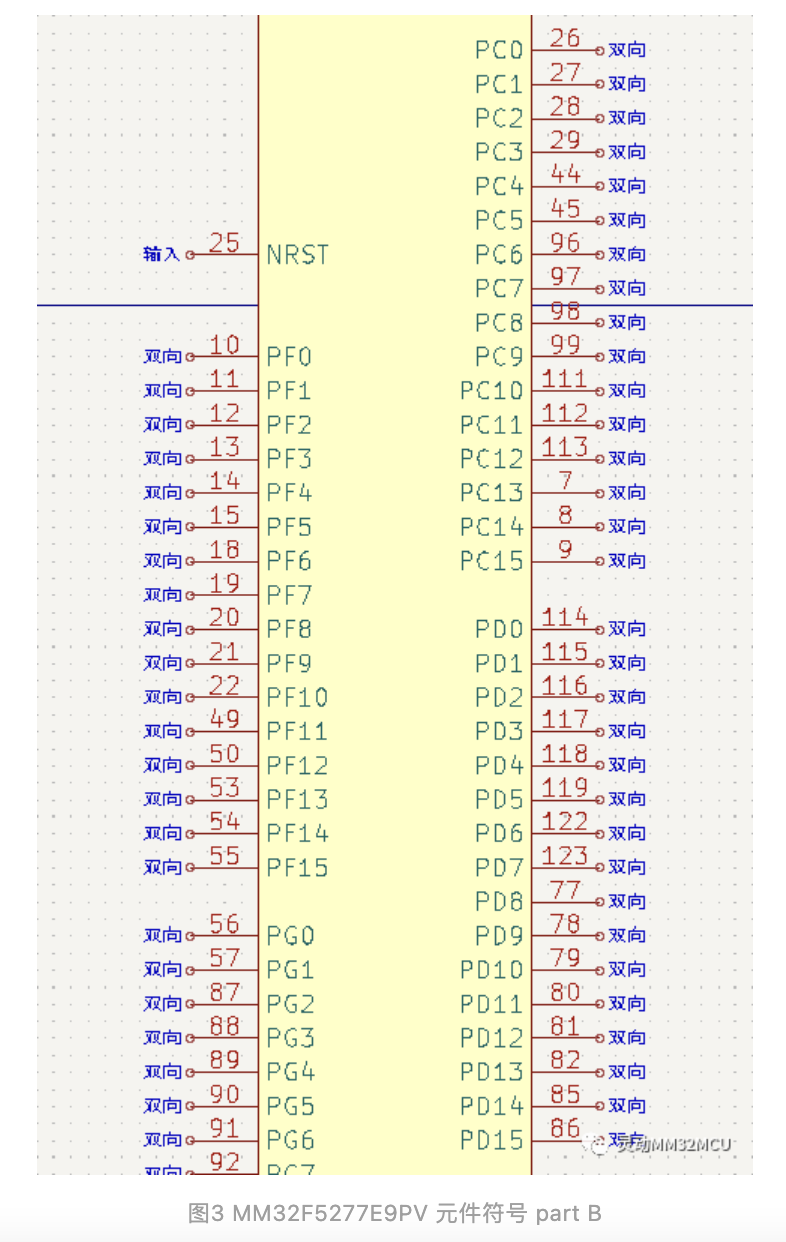

不同用户对 MCU 元件的绘制方法有所不同,较大的器件甚至可以绘制成多个单元,从而能在一张原理图中放下整个器件。

本文介绍一种绘制方法,规则如下:

1. 元件以单个矩形表示,引脚分布在矩形的左右两边。

2. 电源引脚集中放置在左上角,VDD 在上,VSS 在下。

3. GPIO 引脚在右侧放置,且按照 PORT 顺序排列,不同 PORT 中间间隔一个引脚位置,若右侧放置数量过多,可适当将部分 GPIO 放置在左侧。

4. 复位引脚在矩形左侧绘制,其位置在电源引脚的下面,GPIO引脚的上面。

元件绘制如图所示,由于绘制的元件较长,分成三张图片表示(图2,图3,图4):

当然,这种画法也存在一定的问题,A4 大小的原理图需要纸张竖向才能放得下,一般使用的话都调整成 A3 大小绘制。

元件绘制有一些建议:

1. 不建议按照芯片形状绘制,否则一个大矩形,中间空着,浪费原理图空间不说,看着也并不舒服。

2. 引脚按照功能分类,方便索引,如上面提到 GPIO 引脚在右侧放置,且按照 PORT 顺序排列,并没有按照引脚顺序排列,这样方便查找指定功能的引脚。

总之,原理图的第一需求是让用户看得懂,看着舒服,其次才是让机器明白电路之间的关系,因此绘制元件时,也需考虑怎么才能让用户看着舒服,再将元件绘制完整。

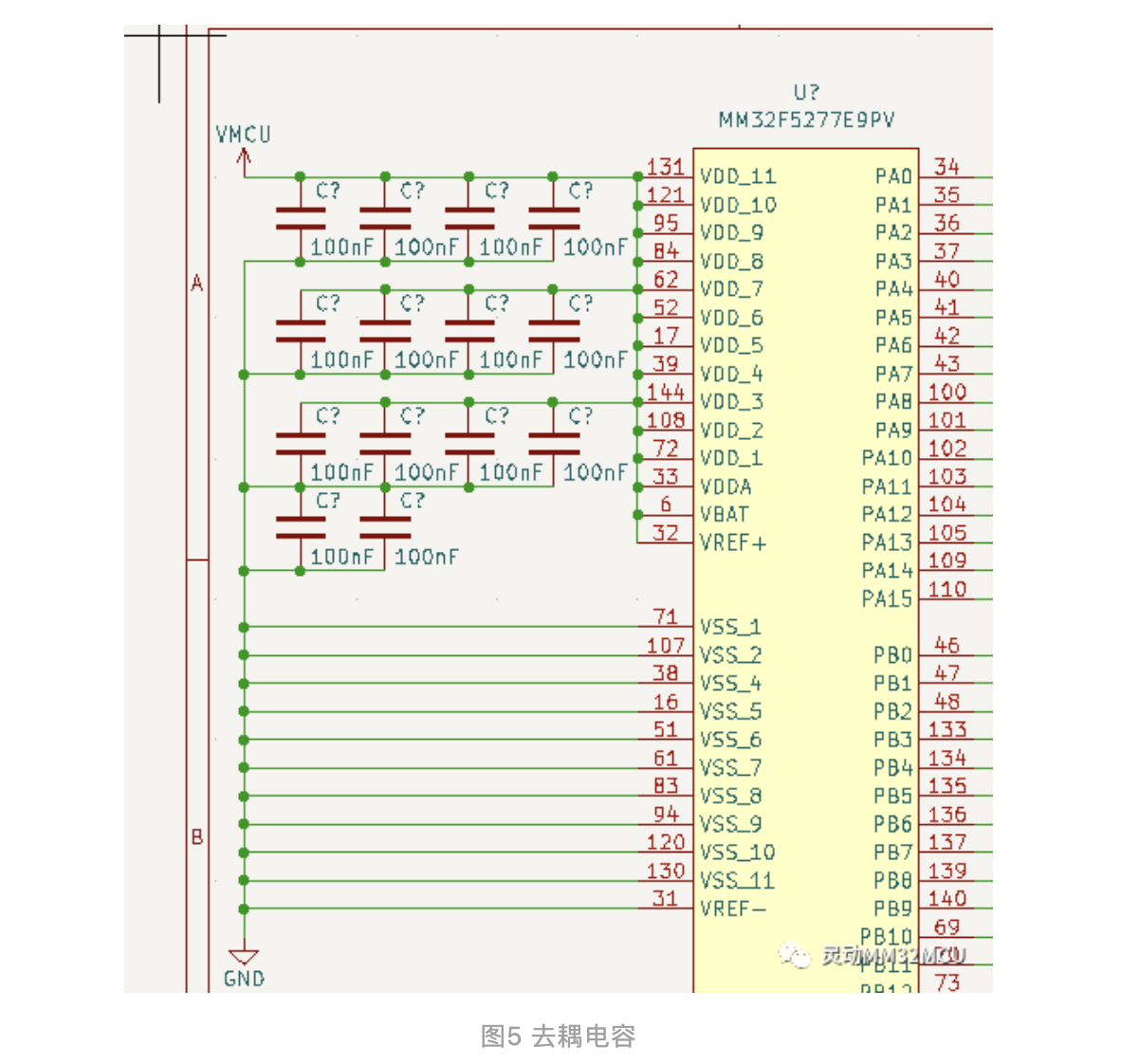

去耦电容

几乎每个器件的电源附近都要放置一个容值为 100nF 左右的去耦电容,来提高系统的稳定性。在此推荐,每个VDD 附近都要就近放置一个 100nF 的去耦电容。MM32F5277E9PV 有11个 VDD 引脚,1个 VDDA 引脚,一个 VBAT 引脚,一个 VREF+ 引脚,因此需要放置14个去耦电容(图5)。

当然,本文的目标是设计一款简单的开发板,对 ADC 的需求没有那么严格,因此 VDDA 以及 VREF+ 与 VDD 使用同样的电源,若有对 ADC 严格要求的场景,需额外使用更加稳定的基准电源,来保证 ADC 的正常工作。同样的,如果有 RTC 需求,VBAT 也需额外处理。

复位电路

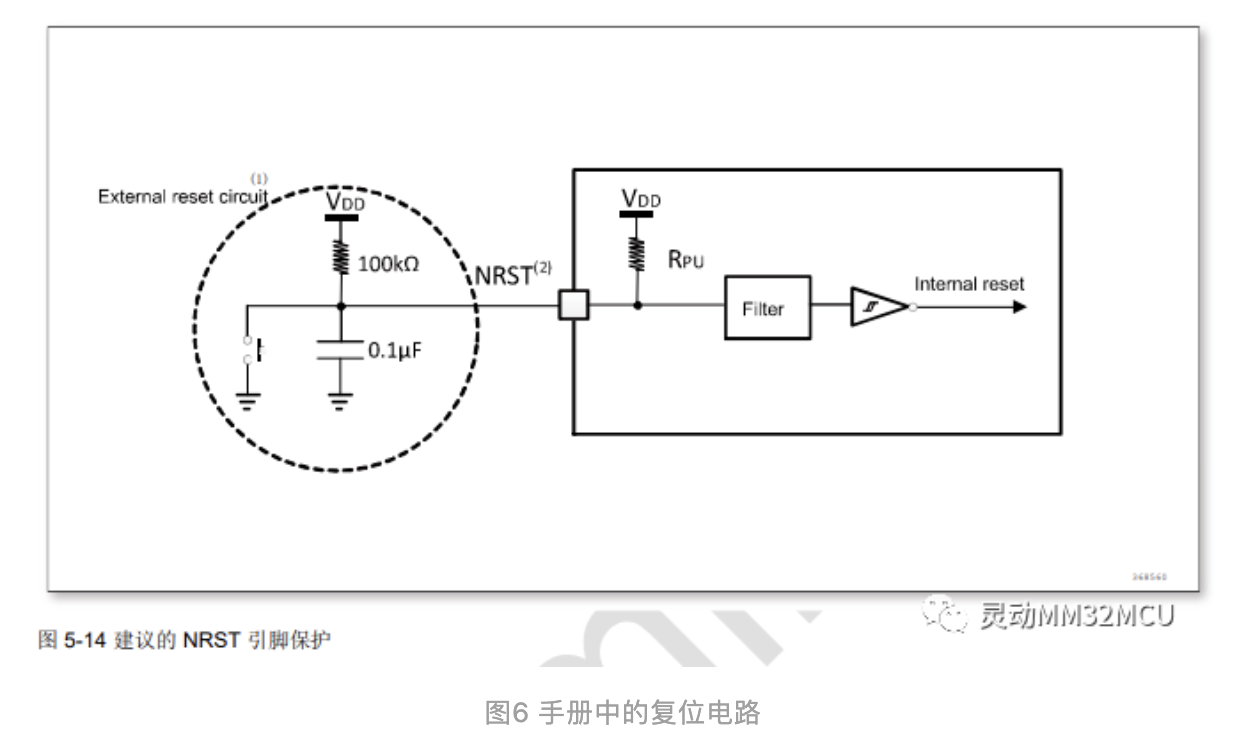

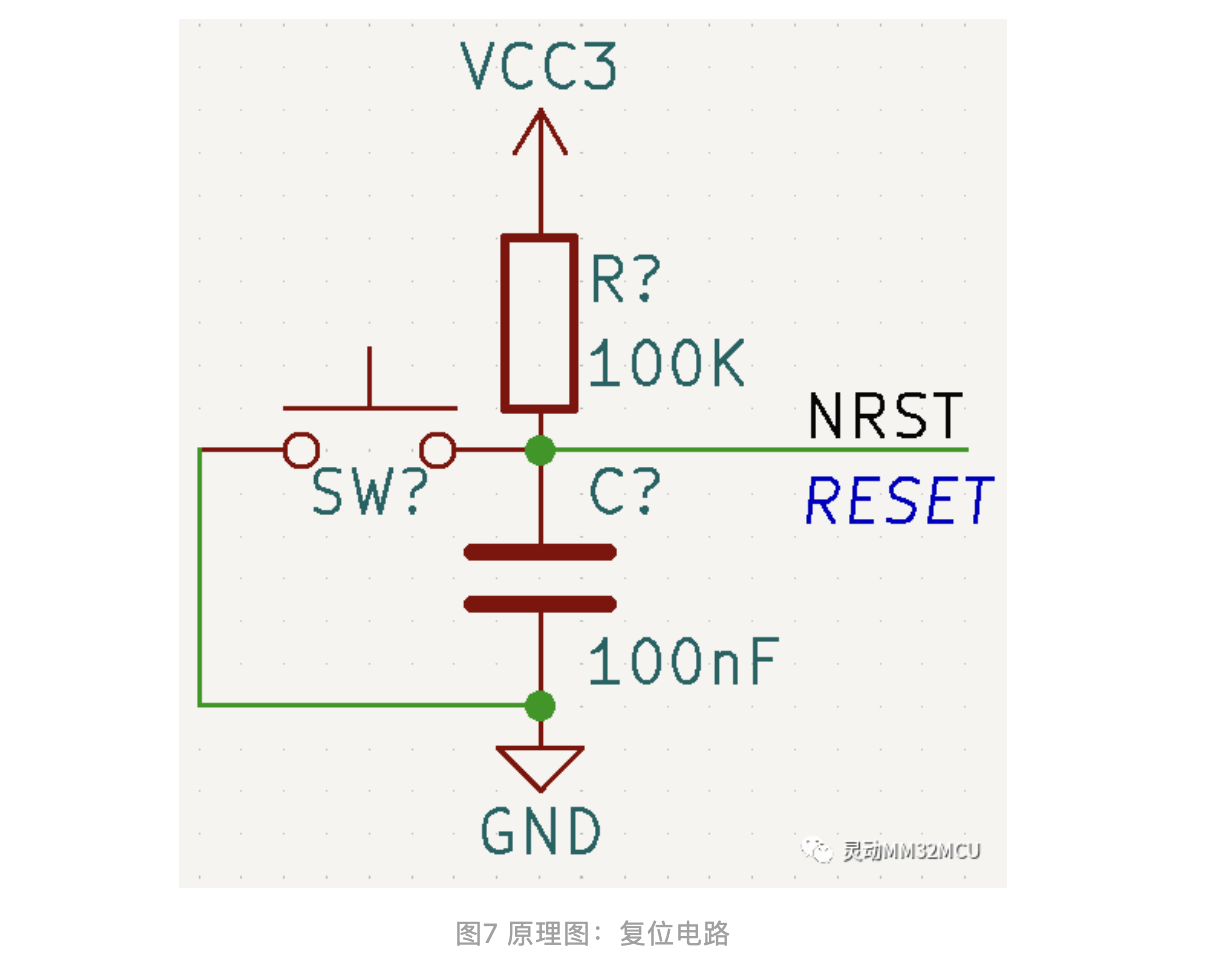

产品手册中有对复位 电路的描述(图6):

通过产品手册可知,为保证系统稳定工作,建议在复位引脚添加一个上拉电阻,和一个接地的电容。作为一个开发板,方便调试,再加上一个按键,方便复位(图7)。

外部时钟

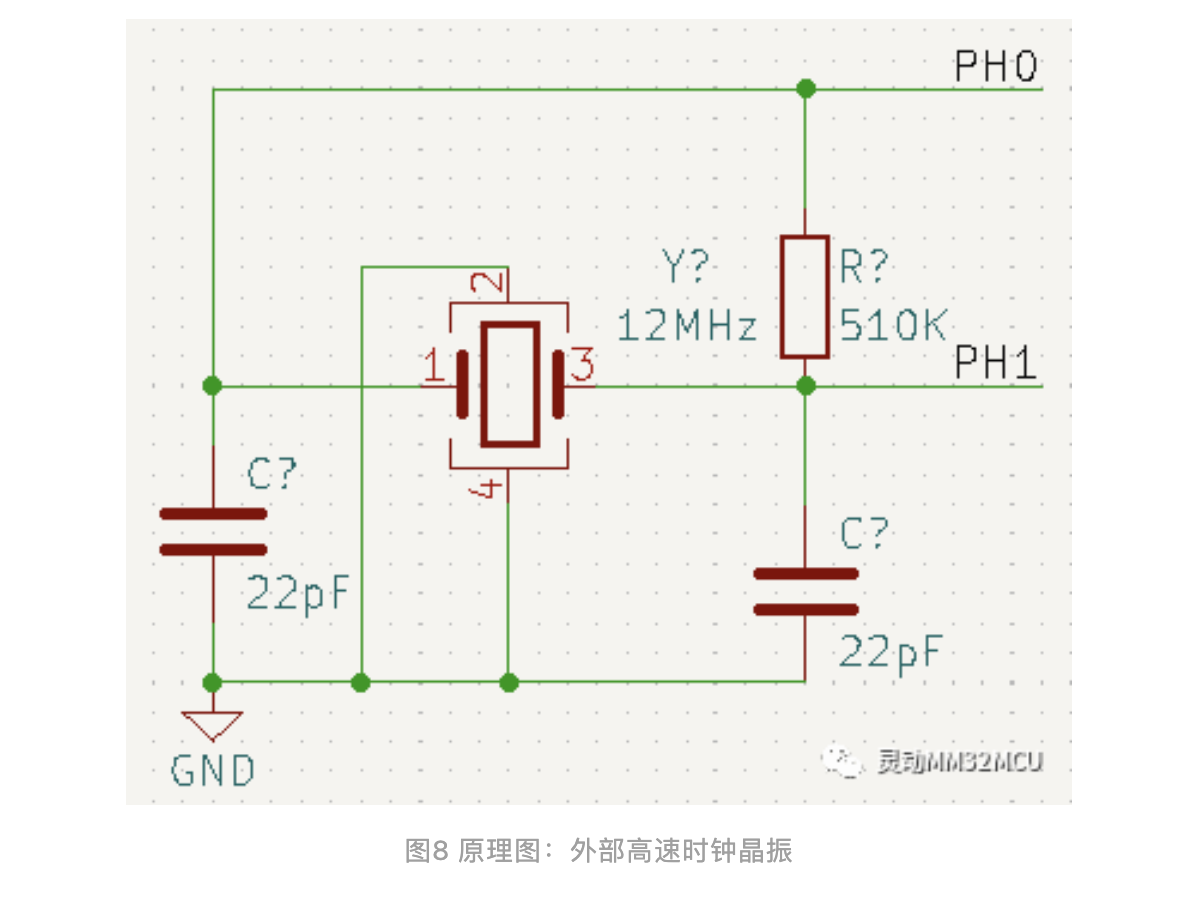

MM32F5277E9PV 内置经出厂调校的 8MHz 高速 RC 振荡器,在一些简单的场合,无需再添加外部晶振,但即使是经出厂调教过,RC 振荡器提供的时钟依然存在误差,对于高精度要求的场合,比如说 USB,尤其是产品在进行 USB 认证时,对时钟精准度要求极高,此时就需要使用外部晶振提供更加精确的时钟来源了。

常见的外部晶振频率一般有 8MHz 和 12MHz,还有32.768KHz 的晶振作为外部低速时钟来源,用于 RTC。如果有 USB 需求的用户,外部高速时钟建议使用 12.000MHz 的晶振,注意12后面有小数点带三个零,比单纯的 12MHz 晶振更精确,这样才能给 USB 提供更精确的时钟。

如图所示(图8),本文采用 12MHz 晶振作为外部高速时钟来源,22pF的负载电容,510K 的反馈电阻。

本文要设计的开发板无 RTC 需求,因此不再放置 32.768KHz 晶振。若有 RTC 需求的用户,可参照 12MHz 晶振的规则,注意选择好负载电容的容值即可。

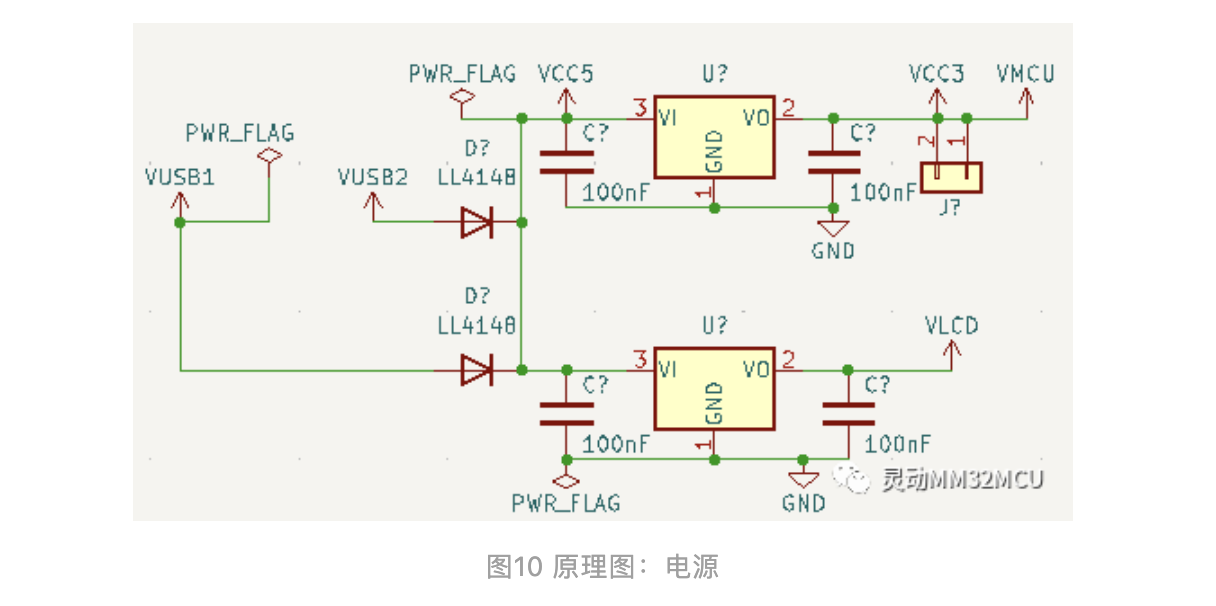

电源

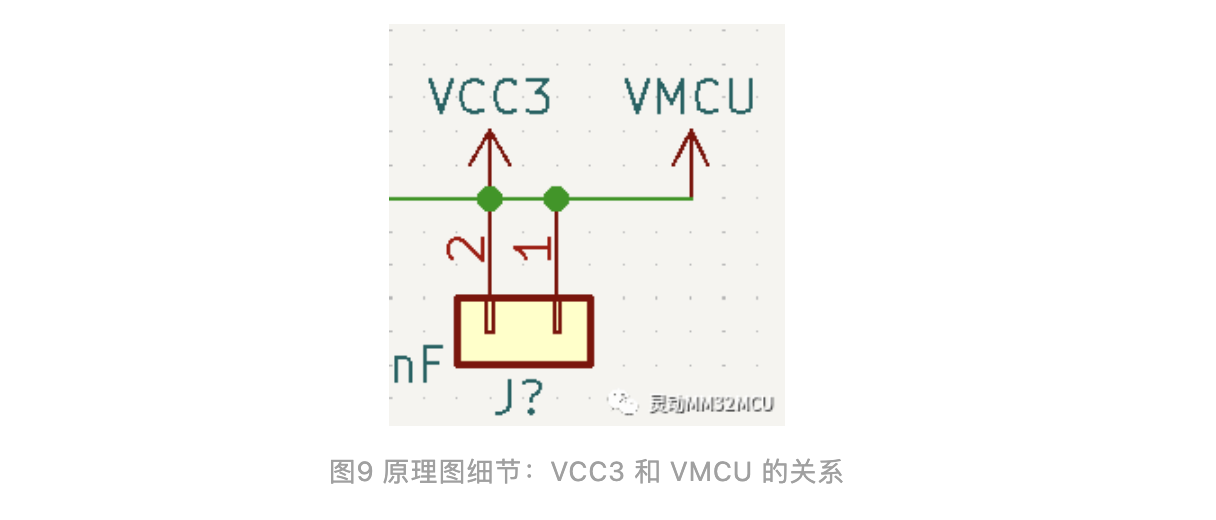

前文的图片中已经可以看到,存在两种不同的电源:VMCU 和 VCC3,VMCU 是用于测量 MCU 功耗而单独设计的电源,实际与 VCC3 导通(图9)。

MM32F5277E9PV 具有较宽的电压范围,支持2.0V ~ 5.5V 供电,但实际电路中,需要考虑外围器件的工作电压,比如稍后介绍的 QSPI Flash,就只能在 2.7V~ 3.6V 左右的电压下工作,综合考虑,在实际电路中,VCC3 的电压选择为3.3V。

本文设计的开发板供电来源为 USB 供电,开发板带有两个 TYPE-C 接口,存在两路 USB 电源,为防止电流倒灌,需使用过二极管隔离。

完整的电源原理图如图所示(图10):

还有个VLCD?这一路是单独给 LCD 屏这个吃电大户提供的,开发板选择使用 XC6206 LDO 作为电源芯片,考虑到可提供的电流较小,因此放置两路 LDO,且 LCD 单独供电,避免电流较大,LDO 吃不消。

为什么两个 LDO 不并联放置?考虑到的一个问题是两个 LDO 总会存在少许差异,如输出电压不一致,若并联放置,则可能其中一个 LDO 在拼命干活, 另个 LDO 在那闲着,那放置两个 LDO 就没有什么意义了。

外设器件设计

最小系统有了,MCU 就能够正常工作了,但没有外围器件,MCU 就是一个光杆司令,你甚至感受不到 MCU 已经运行起来了,除非让它以最大功耗工作,过好一会后,能感受到 MCU 有一丢丢的温热。

那么,就加一丢丢细节,丰富下这个最小系统吧,下面将讲述几个外设的电路设计:

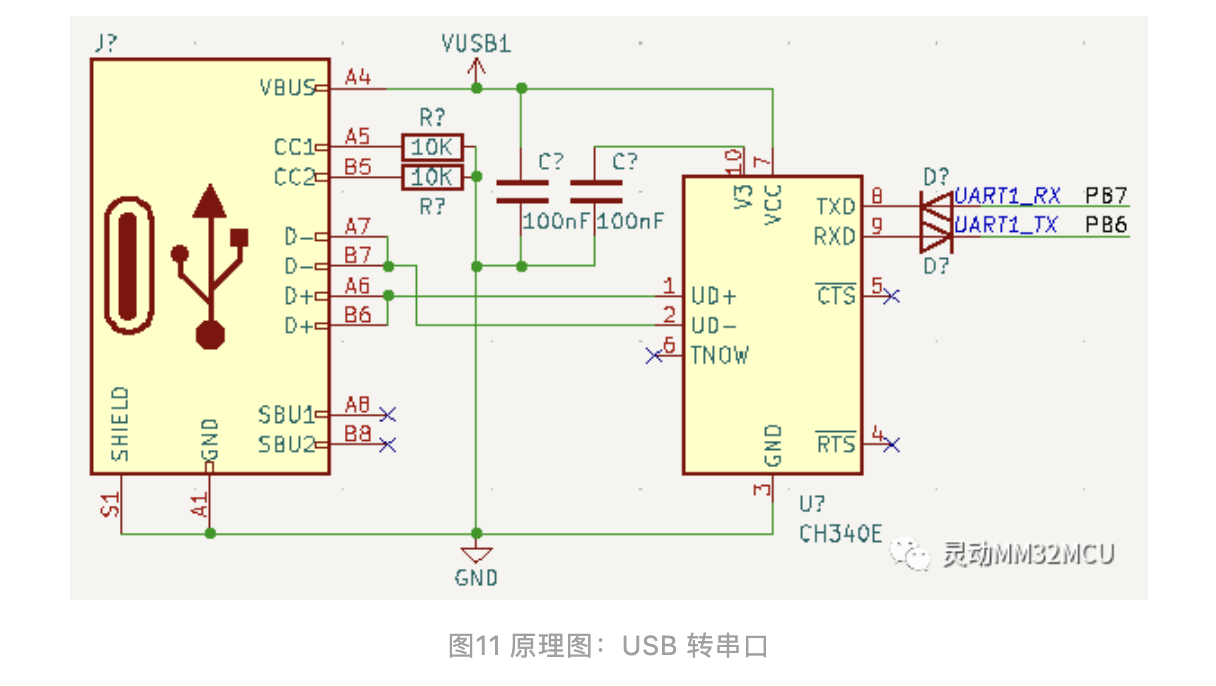

USB 转串口

串口是一个常用的好东西,简单实用,加一个 USB 转串口的器件,方便用户在电脑上查看 MCU 的工作日志呗。

原理图放上(图11):

大多数用户使用串口时,习惯使用 PA9 & PA10 作为调试用的串口引脚,同时具有 ISP 下载程序的功能,但当使用 USB 功能时,PA9 & PA10 会被占用,因此建议使用 PB6 & PB7 引脚作为调试用串口引脚,也具有 ISP 下载功能,且不会被 USB 占用,岂不美哉?

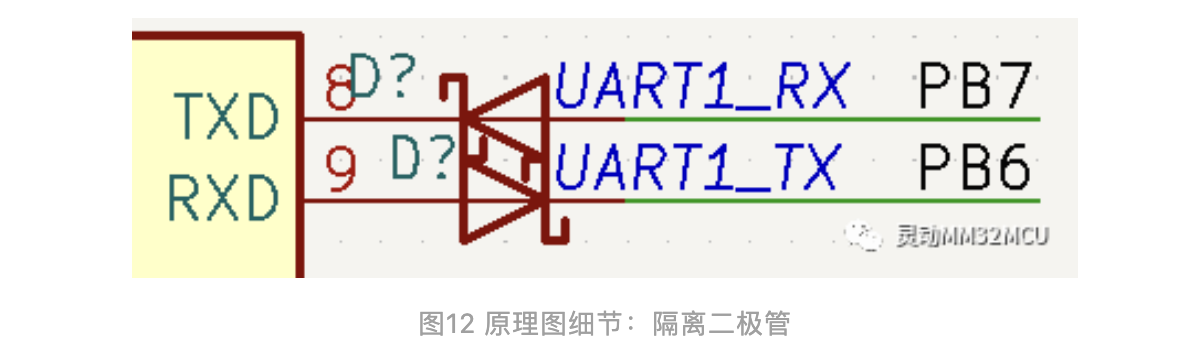

有一个细节(图12),我见过一些板载 USB 转串口的方案,都没有考虑一个问题:串口芯片一般工作在 USB 提供的 5V 电压下,TXD 输出的高电平也是 5V 电压,而 MCU 以及其它外设,是工作在 3.3V 电压下的,如果没有隔离,会影响其他器件的正常工作,因此需要在串口引脚之间,加入肖特基二极管,起到隔离的作用。当然,MCU 的 RX 引脚,也要配置成上拉输入才行。

分析下电路,USB 转串口的 TXD 如果输出高电平,二极管左侧电压高于右侧,二极管截止,MCU 的 RXD 配置为上拉输入,默认为高电平,因此可以接收到 USB 转串口发出的高电平信号;USB 转串口的 TXD 如果输出低电平,二极管左侧电压低于于右侧,二极管导通,MCU 的 RXD 也因此被拉低,接收到了 USB 转串口发出的低电平信号,数据就这样传输起来了,当然,二极管需要选择肖特基二极管这种快恢复的二极管,避免丢数据。

需要注意的是,USB 转串口芯片要根据手册描述来决定是否串联阻抗匹配电阻,否则会造成芯片无法正常工作。

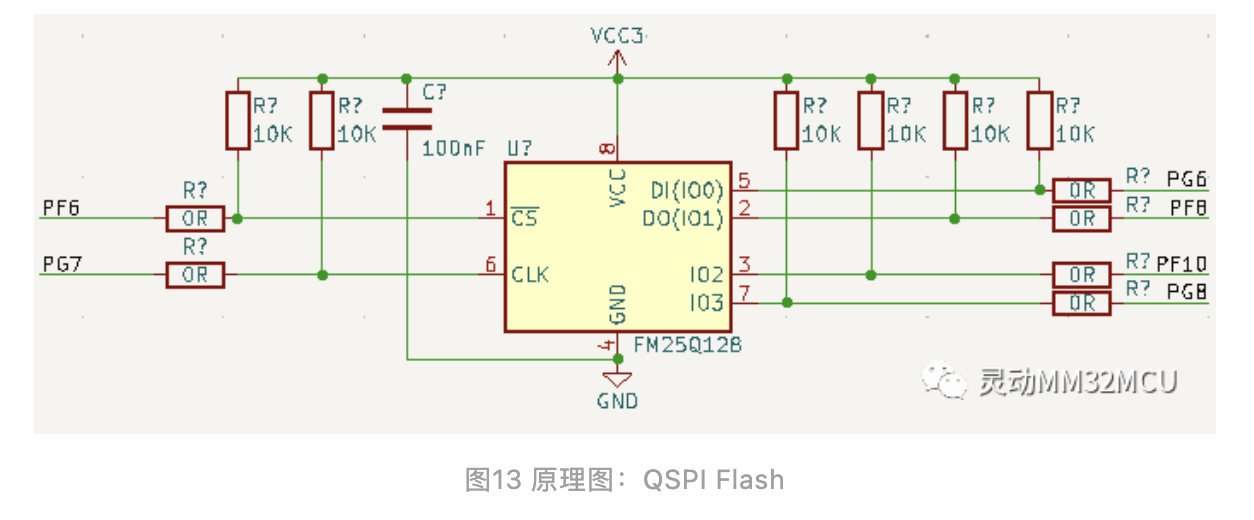

QSPI Flash

MM32F5 系列的一大优势就是具有 QSPI 接口,可以连接 QSPI Flash,并且 XIP 执行 QSPI Flash 中存储程序。

原理图放上(图13):

一个芯片加了好多电阻,其实很多是冗余的,为了适配更多的 SPI Flash 芯片,我们来一一分析下:

以 IO2 和 IO3 引脚的上拉电阻为例,这两个引脚可能会被复用为 HOLD 引脚和 WP 引脚,当这两个引脚处于低电平时,QSPI Flash 芯片就不能随心所欲的使用了,因此,建议手动拉高这两个引脚,防止 QSPI Flash 不能正常使用。当然,在做产品时,可以省略这些上拉电阻,先将IO2 和 IO3 连接的 GPIO 配置为推挽输出模式,输出高电平,待将 QSPI Flash 配置为四线模式时,再将这两个 GPIO 恢复为 QSPI 模式,操作 QSPI Flash。

原理图中的 0R 电阻,其实阻值并不是 0R,而是需要根据 QSPI Flash 的阻抗特性,匹配相应的匹配电阻,以 W25Q 系列芯片为例,建议将 0R 电阻替换为 22R 或 33R 的电阻(仅供参考),否则在四线模式下,读写的数据可能会出错,其它 QSPI Flash 如 FM25Q系列芯片实测 0R 电阻也可用,但实际应用过程中,需根据芯片手册和实际场景,来更换匹配电阻的阻值。

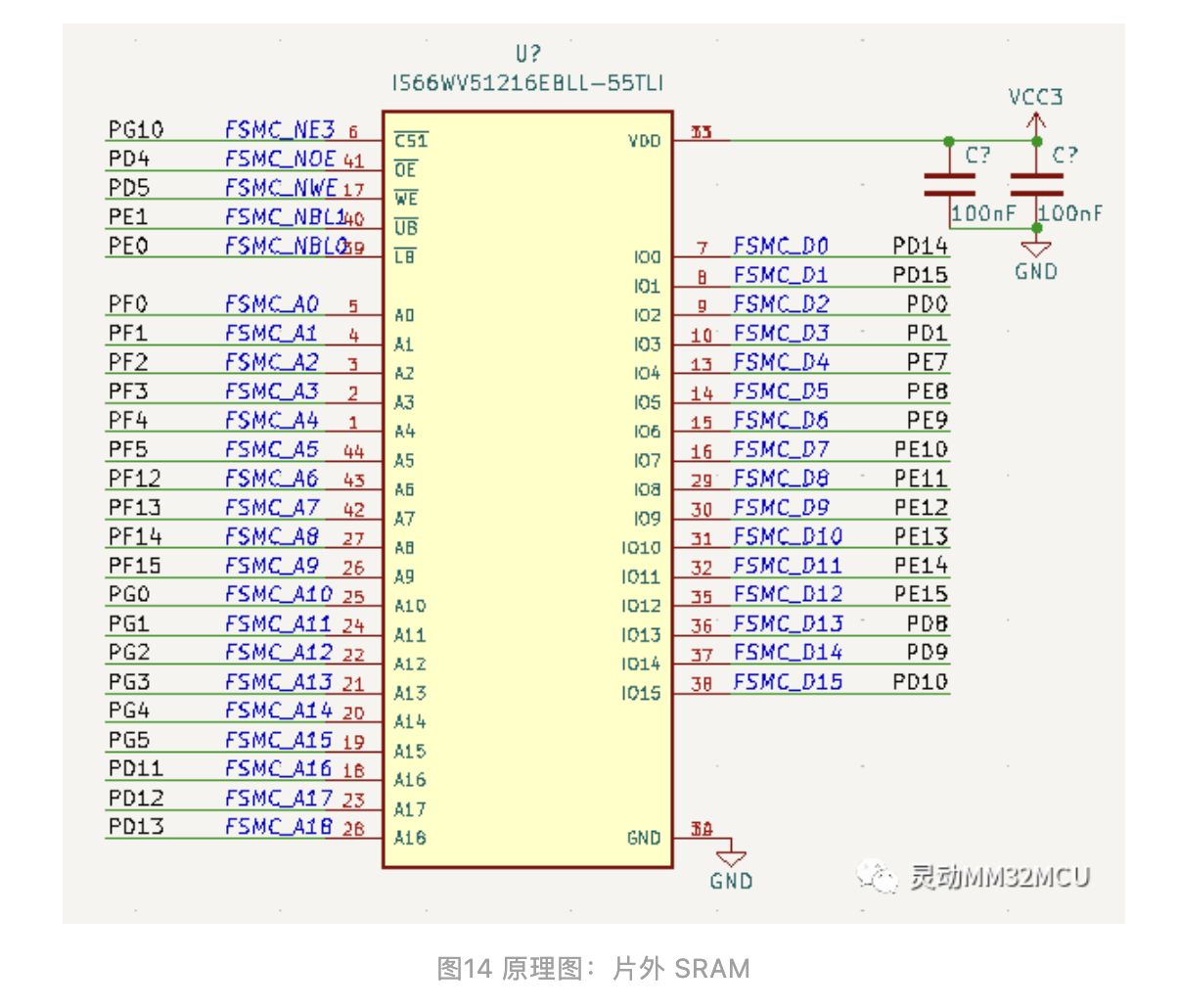

SRAM

使用 QSPI Flash 扩展了 MM32F5277E9PV 的 Flash 大小,何不再扩展下它的 SRAM 呢?

常见的 SRAM 芯片有 SRAM 和 PSRAM 两种,PSRAM 其实是 DRAM 加控制器实现的,对外的接口和 SRAM 无差,但成本会比 SRAM 低不少,感兴趣的用户可以了解下。

原理图没什么好讲的,把线连起来就行,重点是 PCB 布线,SRAM 走的是并行信号,并且信号频率也挺高的,需要考虑下线路的问题了:

1. PCB 布线是否等长?

2. 信号线过孔数量是否过多?

布线要等长,这一条其实挺难实现的,如果没特别要求,在实际布线中,只要别差个十万八千里,也没啥大问题,调整 FSMC 的工作参数,别让它工作的太快也能用起来,当然,这样的话性能肯定会受影响,就需要综合考虑情况了。

过孔其实挺烦人的,每增加一个过孔,就相当于在信号线上加了个数皮法的电容,信号质量肯定会受影响,因此,要减少过孔数量,实测两三个没啥问题,但过孔多了,还是得担心信号质量问题了。

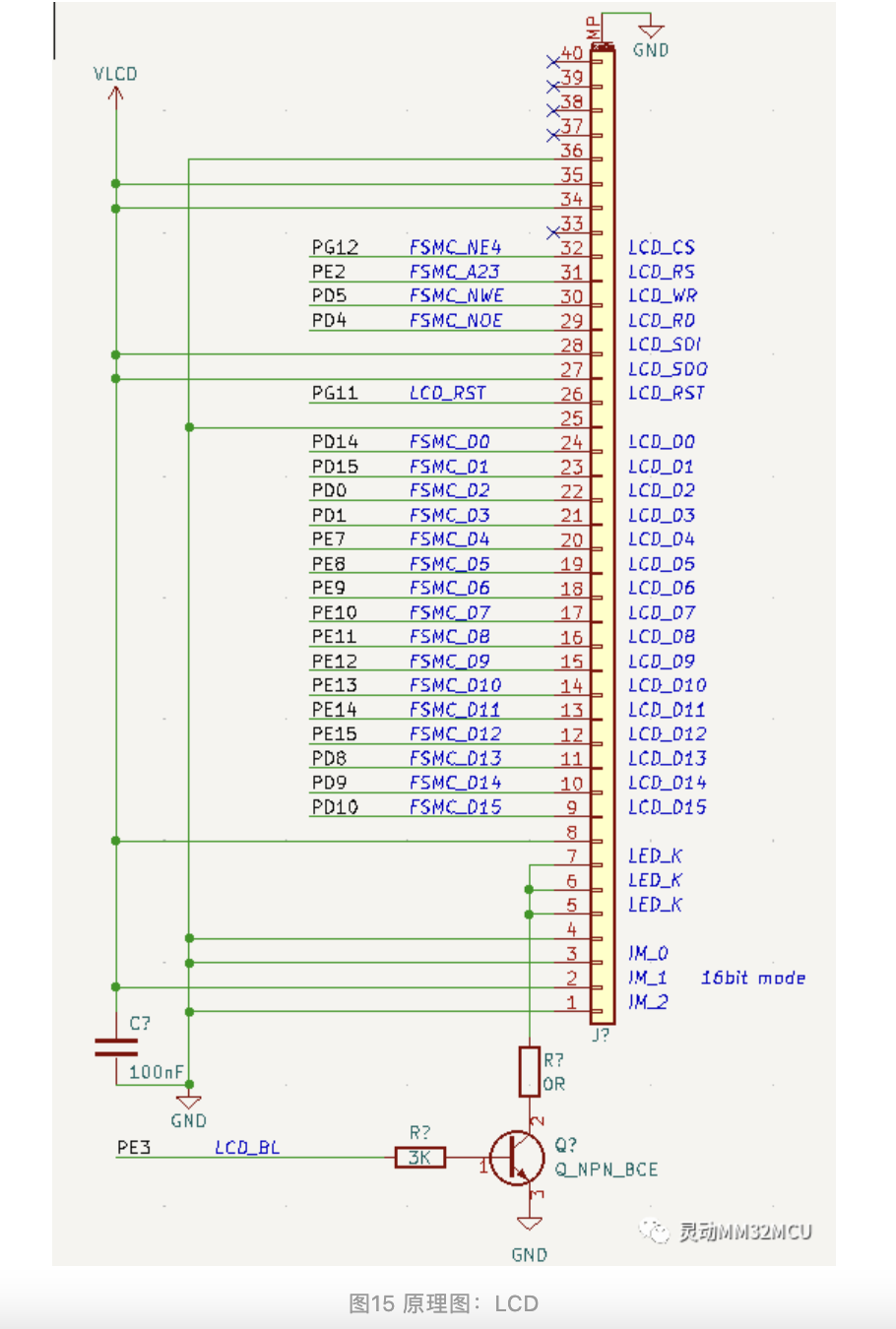

LCD

同 SRAM 一样,LCD 也是使用 FSMC 驱动,当然,SPI 也可以,但有 FSMC,为什么还要用 SPI 慢悠悠刷屏呢?

放原理图(图15):

信号线也没什么多讲的,接上就行,需要注意几点:

1. 同 SRAM 一样,注意信号线要尽可能等长,过孔数量尽可能少。

2. LCD_RS 可接 FSMC 任意一根地址线,但软件要根据所接的地址线,来决定向哪个地址读写数据。

3. LCD_RST 接任意 GPIO,该 GPIO 配置为普通的推挽输出即可,与 FSMC 无关。

需要看的就是这个 LCD 的背光控制了,LCD 背光来自于 LED,由于工作电流较大,不能单纯使用限流电阻草草了事,而应该使用三极管进行电流控制,LCD\_BL 同 LCD\_RST 一样,接任意 GPIO,该 GPIO 配置为普通的推挽输出即可,与 FSMC 无关,当然,如果想实现屏幕亮度控制的话,可用带定时器 PWM 输出的引脚作为背光控制,使用 PWM 波控制屏幕亮度。

结语

本文通过设计一个 MM32F5277E9PV 开发板的原理图讲解下 MM32F5 的硬件系统设计,以及分享下设计电路中遇到过的坑,比如说 USB 转串口的问题,一个是 USB D+ & D- 不加串联电阻,一个是串口电流倒灌,都是本文作者切身实际踩过的坑,希望大家设计电路时,能够注意到这些问题,减少 PCB 打样的次数,也希望能有更多的人,选择使用 MM32F5 系列的芯片,做出更多更有趣的产品。

作者:灵动MM32

文章来源:灵动MM32MCU

推荐阅读

- 灵动微课堂 | 灵动微控制器软件开发平台MindSDK简介

- 灵动微课堂 | MM32F0140学习笔记——独立看门狗(IWDG)

- 灵动微课堂 | MM32F0140学习笔记——FlexCAN 控制器局域网

更多MM32F5系列资料请关注灵动MM32 MCU专栏。如想进行MM32相关芯片技术交流,请添加极术小姐姐微信(id:aijishu20)加入微信群。