【爱集微点评】钜泉科技发明的一种亚稳态修正电路、逐次逼近型模数转换电路方案,借助于亚稳态检测模块,来对输出比较完成的最长时间信号进行检测,从而可以检测到SAR ADC中比较器可能出现的亚稳态,并进行修正。

集微网消息,模数转换器(ADC)是一种将模拟信号转换成数字信号的电路。ADC的应用范围非常广泛,包括通信设备、测试仪器、音频设备等都有ADC的应用。随着集成电路工艺的发展,逐次逼近模数转换器(SAR ADC)因其低功耗和受工艺影响较小的优势获得了越来越多的关注。

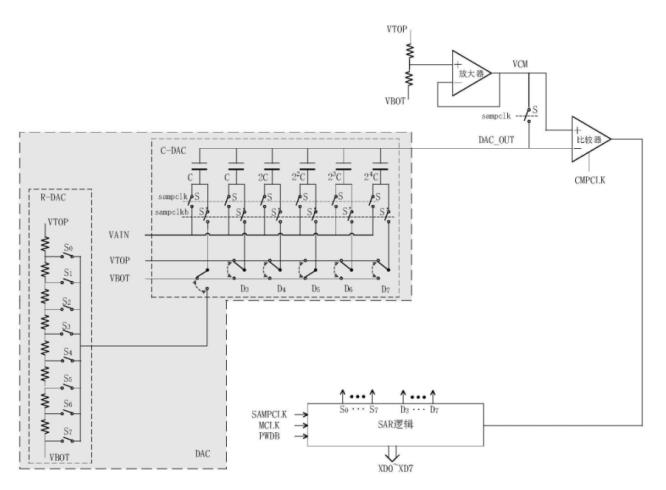

如上图,为常见的SAR ADC的系统示意图,虚线框内的部分为数模转换器(DAC),其作用为产生用于采样的信号,以及转换时产生用于比较的逐次逼近的信号DAC_OUT。其电路中具体的波形如下图所示,电路中的DAC部分产生的DAC_OUT信号作为比较器的一个输入信号,与另一个输入信号VCM进行比较,并且根据比较结果改变DAC的开关切换,以产生下次的待比较信号。

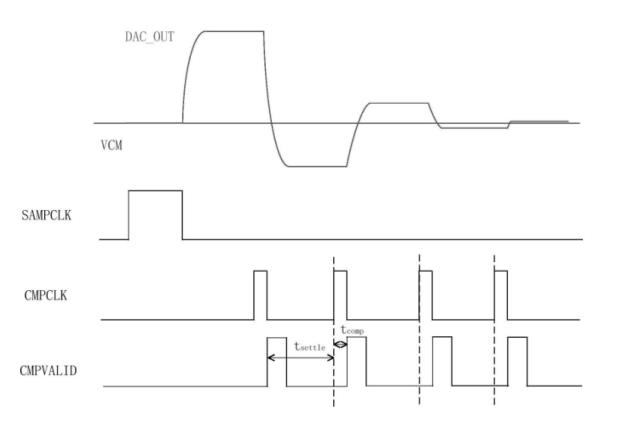

随着SAR ADC往高速发展,异步时钟得到了更多的应用。例如上图中,DAC的输出经过一定的建立时间tsettle后,产生一个CMPCLK上升沿通知比较器开始比较。经过一段比较时间tcomp后,产生比较结果,并且CMPVALID产生一个上升沿表示该次比较完成,同时开始下次的DAC建立过程。

从上面的异步时钟原理来看,这种ADC不需要外部的主时钟来同步各操作。而且当比较器的比较速度快时,可以有比同步主时钟更快的工作速度。但是比较器的比较时间与输入端的信号差值相关,当输入信号差值较大时,比较时间较短,但是输入信号差值比较小时,比较时间会很长。所以当DAC_OUT和VCM的差值非常小时,会出现很长时间都不能产生出正确比较结果的情况,这个现象称为SAR ADC中比较器的亚稳态。亚稳态对SAR ADC正常工作的影响很大,使ADC有可能无法完成正常的比较,尤其在低电压的SAR ADC中,亚稳态的影响更大。

为缓解亚稳态的影响,钜泉科技在2021年3月31日申请了一项名为“一种亚稳态修正电路、逐次逼近型模数转换电路”的发明专利(申请号:202110349289.8),申请人为钜泉光电科技(上海)股份有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项技术方案吧。

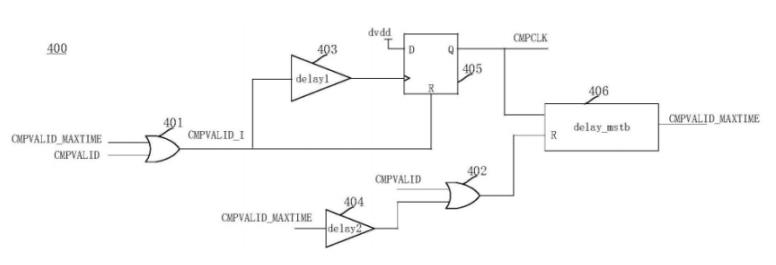

如上图,为该专利中公开的亚稳态检测电路的示意图,上图中是一种逐次逼近型模数转换电路的亚稳态修正电路400,该电路包括:第一与门401、第二与门402、第一延迟线403、第二延迟线404、触发器405和亚稳态检测模块406。亚稳态修正电路可以检测到逐次逼近型模数转换电路(SAR ADC)中比较器可能出现的亚稳态,并进行修正。

第一与门的两个输入端分别与比较完成的最长时间信号和比较完成信号耦合,输出端分别耦合到第一延迟线的输入端和触发器的第一输入端,输出CMPVALID_I到第一延迟线和触发器。第二延迟线的输入端与比较完成的最长时间信号耦合,第二延迟线的输出端耦合到第二与门的第一输入端,第二与门的第二输入端与比较完成信号耦合,第二与门的输出端耦合到亚稳态检测模块的第一输入端。

触发器的输出端耦合到亚稳态检测模块的第二输入端,亚稳态检测模块输出比较完成的最长时间信号CMPVALID_MAXTIME。例如,触发器输出比较开始信号CMPCLK到比较器。当比较器存在亚稳态时,亚稳态检测模块输出的比较完成的最长时间信号CMPVALID_MAXTIME复位比较开始信号CMPCLK,并且,比较器输出指定电平。

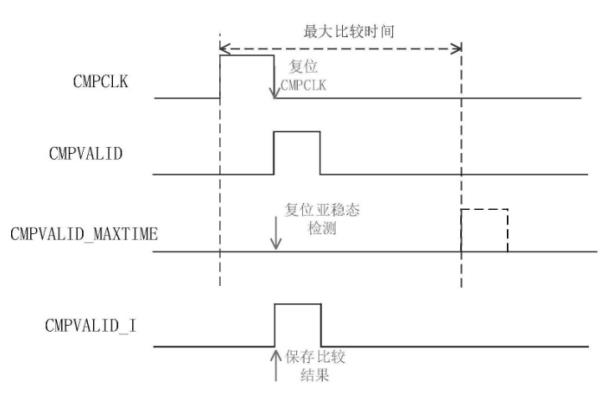

如上图,为该专利中展示的比较器不存在亚稳态时的时序图,当比较器可以正常比较出结果时,比较完成信号CMPVALID变为高,将比较开始信号CMPCLK复位,并且将亚稳态检测模块也复位,同时保存比较器的比较结果。

以上就是钜泉科技公开的一种亚稳态修正电路、逐次逼近型模数转换电路方案,该方案借助于亚稳态检测模块,来对输出比较完成的最长时间信号进行检测,从而可以检测到SAR ADC中比较器可能出现的亚稳态,并进行修正。