编者按

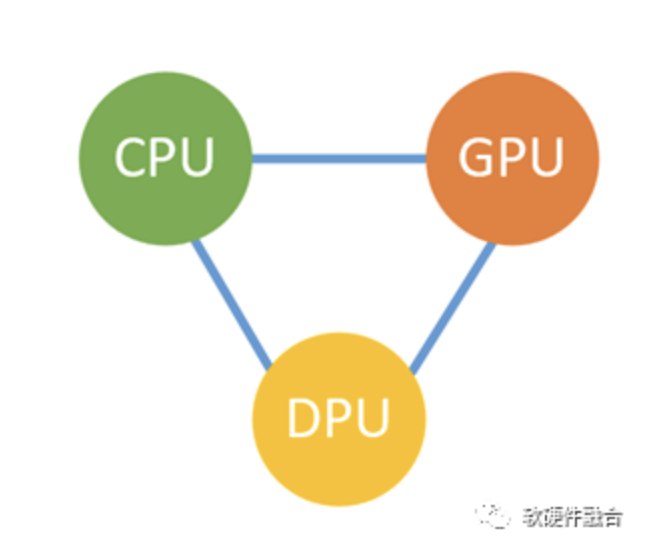

CPU、GPU和DPU是数据中心的三大芯片,通常情况下:CPU主要用于业务应用的处理,GPU用于性能敏感业务的弹性加速,而DPU则是基础设施加速。站在CPU的视角:一开始所有事情都是我的,然后GPU从我这“抢”过去了一部分工作,现在又出现个DPU来跟我“抢食”。是可忍孰不可忍,必须坚决反击!

1 CPU视角看硬件加速

站在CPU视角,最开始,一切处理都通过处理器CPU的常规指令集完成。随着CPU性能瓶颈,需要硬件加速的方式来提升性能。硬件加速大致有如下几种方式:

- 方式1:实现支持扩展指令集的协处理器,实现一定程度的加速能力。比如Intel集成的AVX和AMX指令集,ARM的NEON指令集等。

- 方式2:独立的单一架构的加速器。比如GPU、AI芯片。

- 方式3:独立的多架构集成加速器。比如DPU。

- 方式4:即将开始的一种方式,集成单个或多个加速器。

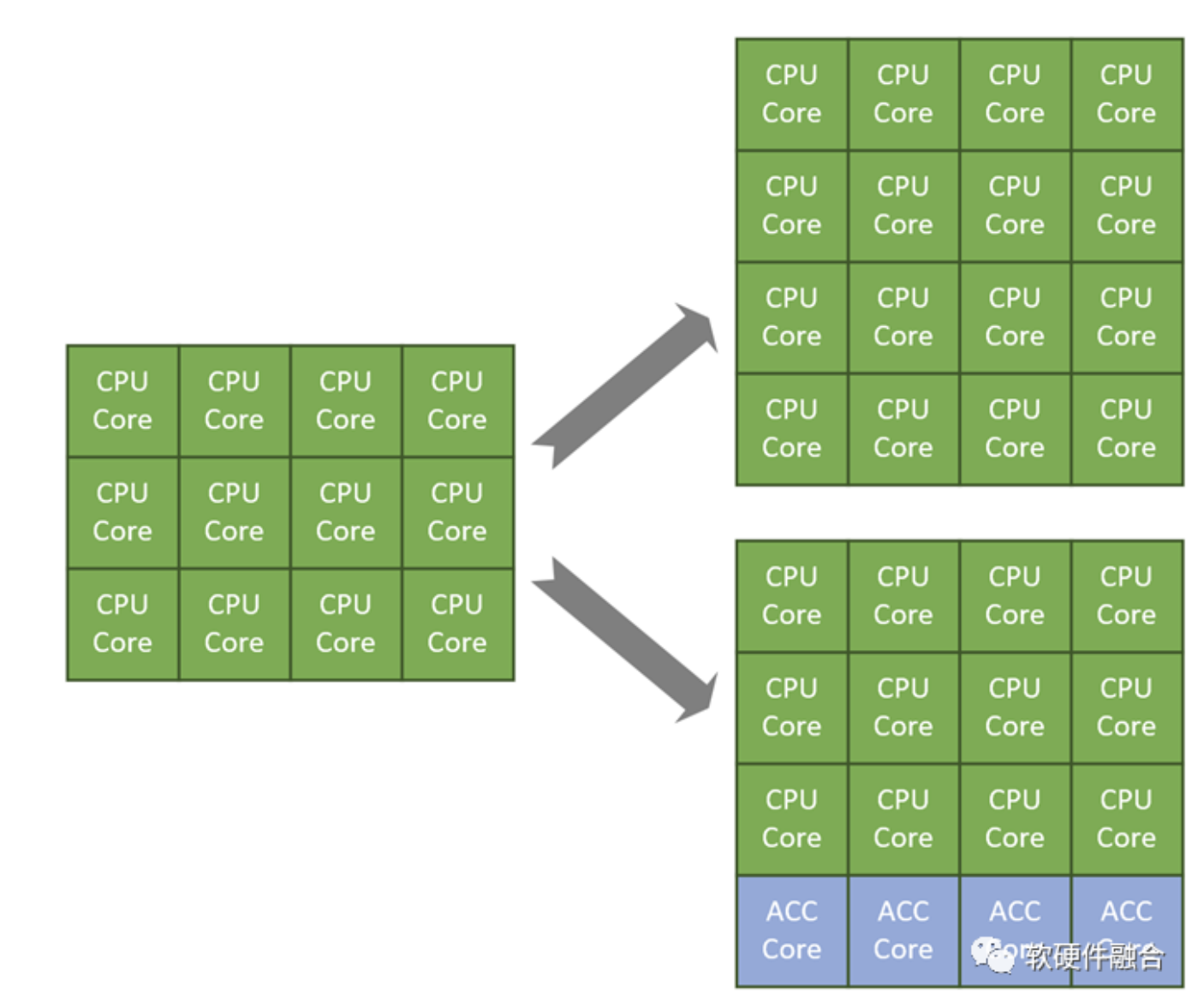

这里需要大家区分两个概念:处理器核和处理器芯片。处理器芯片是由同构或异构的处理器核组成的。

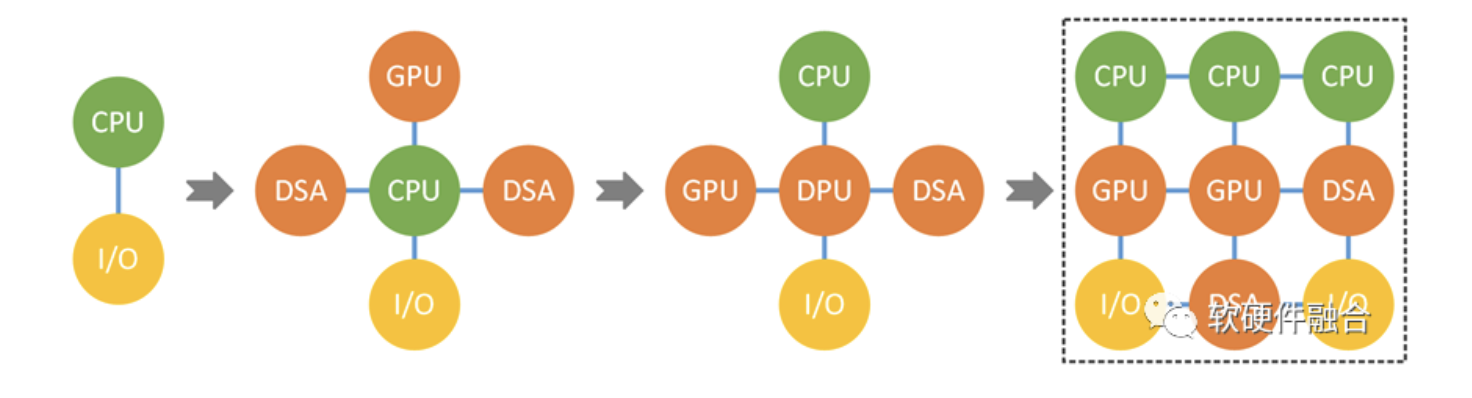

CPU已经到了性能瓶颈,这是大家的共识;当CPU遇到性能瓶颈的时候,通过加速的方式进一步提升性能,也是大家的共识。但是,加速的实现形态,是分立的多个芯片,还是集成的单个芯片,就是“仁者见仁智者见智”的事情了。独立的DPU公司会认为,独立的DPU有很多的优势;但是在CPU厂家而言,通过CPU集成加速器核,使得CPU成为某种程度上的类SOC芯片,也是完全可行的。

2 独立DPU的价值基础并不牢靠

DPU作为独立的集成加速平台,其价值可以从四个方面进行阐述:

- 价值一:为了进一步提升性能,DPU实现CPU工作任务的卸载和加速;

- 价值二:从I/O的硬件虚拟化(也可以看做是I/O模拟的硬件卸载)开始,DPU实现I/O模拟、I/O Workload以及整个虚拟化和基础设施层的全量卸载和加速;

- 价值三:从运维和管理视角,DPU重要的价值在于实现了业务和基础设施分离,实现了业务主机的安全访问;

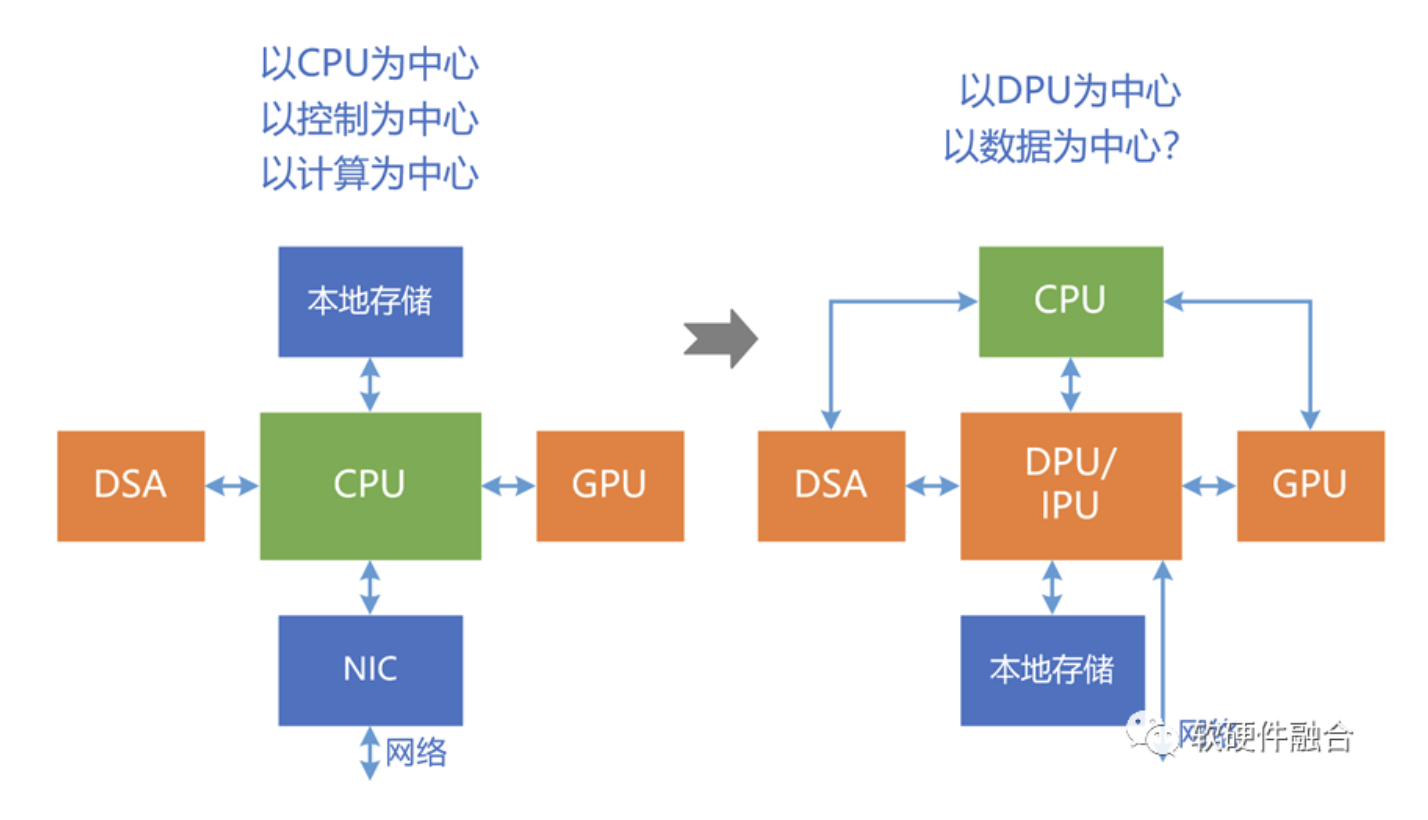

- 价值四:面向更大计算量和数据吞吐量,DPU实现从“以计算为中心”到“以数据为中心”。

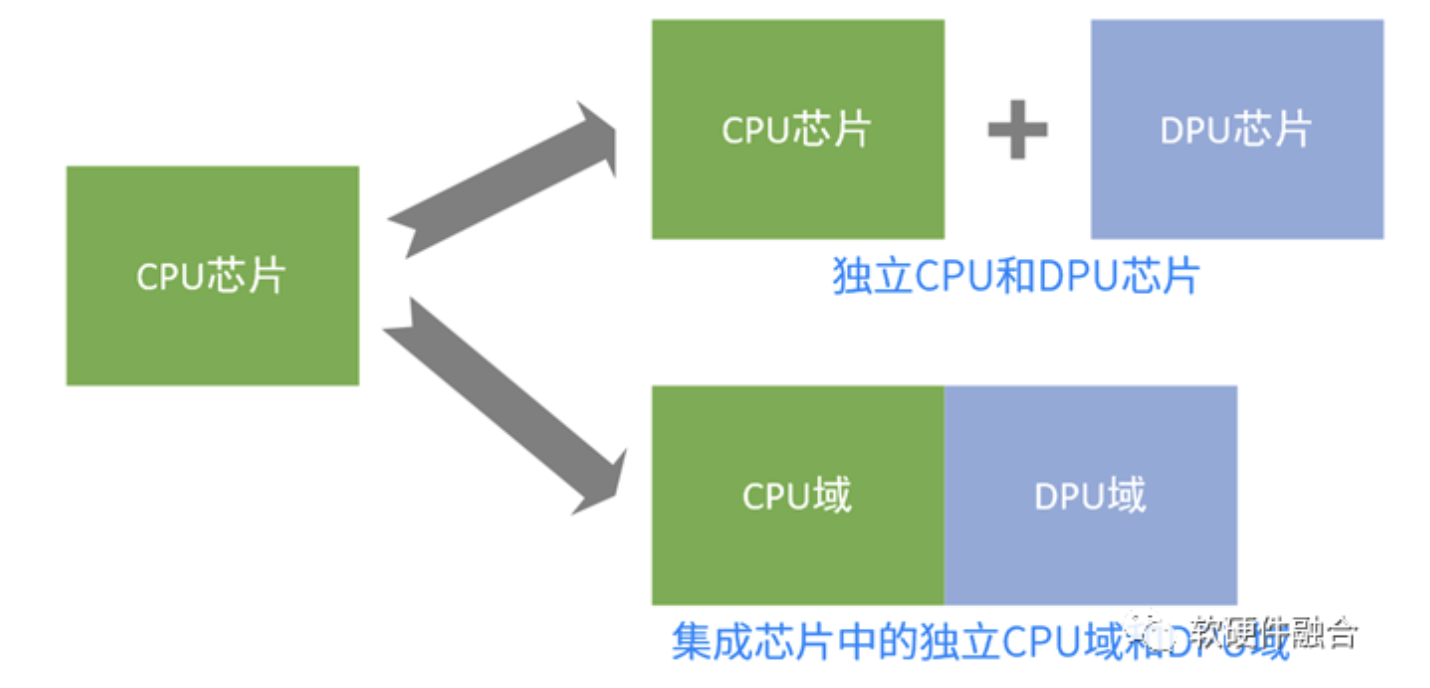

DPU的前三个价值,其实现:可以是独立的DPU芯片实现,也可以是集成的DPU域实现。这对功能和特征没有任何影响,甚至集成的方式,还有一些优势:优化访问效率,提升性能;集成芯片进一步降低成本和功耗。

DPU的第四个价值,一方面,和独立或集成无关,也就是说独立或集成都可以;另一方面,DPU并不一定能够实现以数据为中心的价值。

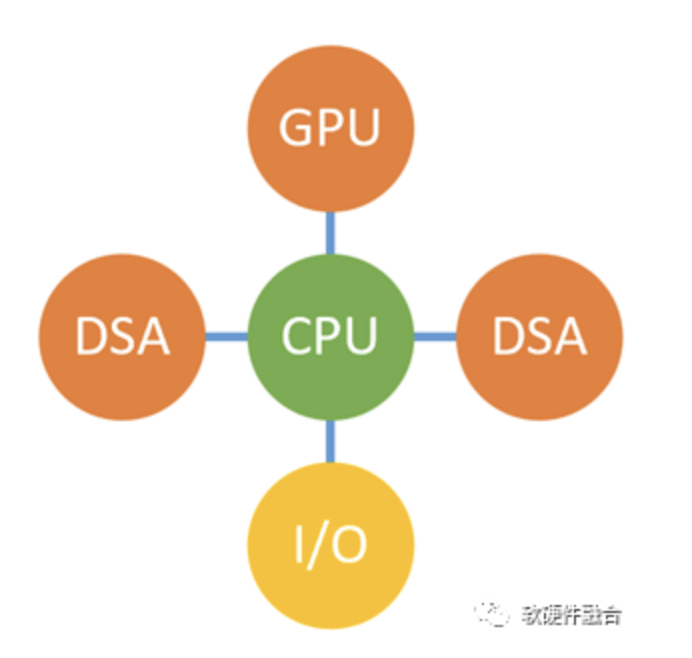

上面这张图,通常把左边的称为“以计算为中心”,右边的称为“以数据为中心”。然而,这种表述是有问题的。严格来说,左边称为“以CPU为中心”、“以控制为中心”或者“以计算为中心”是可以的,右边这张图称为“以DPU为中心”是合适的,但如果称为“以数据为中心”则是不准确的。“以DPU为中心”并不一定等于“以数据为中心”,“以DPU为中心”,完全可能是“以‘CPU’为中心”,或者说是“以计算为中心”。

最终的结论是:很多DPU其实并非严格意义上的数据驱动处理器,并且即使DPU是数据驱动的,依然无法保证整个计算机系统是完全数据驱动的。

3 Intel Sapphire Rapids CPU介绍

Sapphire Rapids是Intel新一代的数据中心CPU,用于接替Ice Lake。Sapphire Rapids相比Ice lake,从单个TILE变成了4个TILE的Chiplet集成。

Sapphire Rapids可以提供更高的单节点性能:

- 处理器方面,如更高性能的微架构实现、更多的内核数量、AMX扩展、多个集成的加速引擎等;

- 存储方面,如更大的私有/共享缓存、DDR5/HBM等;

- I/O方面,如采用PCIe 5.0、UPI2.0、支持新一代Optane等;

- Chiplet封装:EMIB总线实现多TILE集成。

除了单芯片的性能提升之外,Sapphire Rapids还提供更高的数据中心整体性能,例如快速VM迁移、更强的遥测能力、更强的I/O虚拟化、缓存和内存性能一致性、新一代QoS、CXL1.1、更加的弹性,以及提升资源利用率等等。

而Sapphire Rapids的最大创新则是:AIA。通过AIA集成多种加速引擎,包括数据流加速器DSA(Data Stream Accelerator,不是Domain Specific Architecture)、QAT等。我们将在接下来的一节对AIA详细介绍。

4 Intel里程碑:AIA

4.1 背景知识:加速器接口/架构

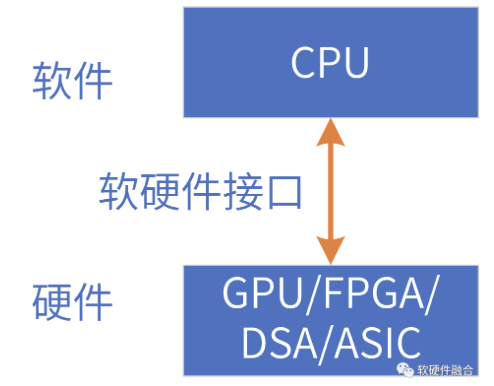

相对于CPU,其他类型的处理器,都可以称为加速处理器,如:GPU、DSA和ASIC等(FPGA需要具体的处理器实现)。这些加速器都是非图灵完备的,因此都需要和CPU组合成Host CPU+xPU的异构计算方式工作。

加速器接口,也即加速器呈现给Host CPU的软件访问接口,也可以称为加速器架构。在这里,架构和接口的概念是等同的。

4.2 AIA技术介绍

AIA(Accelerator interfacing Architecture,加速器接口架构)不是一个简单的功能或特征实现,而是一组相关技术能力的组合(类比Intel的VT-x和VT-d技术)。从Intel新一代Xeon处理器Sapphire Rapids开始,提供加速接口技术AIA,其技术点包括如下:

- 任务分配指令(MOVDIRI、MOVDIR64B、ENQCMD/S)用于优化任务卸载,ENQCMD/S支持共享任务队列;

- 用户态等待指令(UMONITOR、UMWAIT、TPAUSE),用于高效同步;

- 低延迟用户态中断;

- 共享虚拟内存;

- 轻量的可扩展I/O虚拟化S-IOV。

AIA目前支持的加速类型有:数据流处理DSA、加解密和数据压缩QAT等。

4.3 Intel AIA的战略意图分析

作为全能型的处理器,通吃整个计算市场几十年的CPU,面临性能瓶颈的巨大挑战。于是,各种加速处理器,如GPU、DPU等,都在拼命地“挖CPU的墙角”。

作为CPU的霸主,Intel肯定不会“坐以待毙”,一定会“奋起反击”。AIA就是Intel准备的“核弹”级的武器,AIA是Intel CPU的重要里程碑,其战略意图(可能)是:

- 捍卫CPU的核心地位,所有的一切加速器都需要围绕着CPU技术生态展开;

- Intel试图通过AIA统一加速器接口、架构和生态。以GPU作为案例:一方面GPU是独立的架构和生态,与CPU架构是解耦的,可以基于x86架构,也可以迁移到ARM或RISCv架构;另一方面,GPU架构是各自封闭的,NVIDIA有自己的架构和生态,AMD有自己的架构和生态。AIA也许无法把所有的不同加速器类型都统一到一个标准的AIA,但是把GPU统一一个,各种领域加速器DSA各统一一个,是完全可能并且技术上可行的。

- 一些常见的、关键的加速器,就自己搞定,集成到CPU中,比如Sapphire Rapids集成了数据流处理DSA(DSA可以把很多数据处理类的加速统一进来,如网络和存储等)和QAT,未来再集成AI、网络、存储、虚拟化卸载、安全等基础设施层处理(也即DPU覆盖的范畴)功能或加速器,其可能性也是非常的高。

5 Intel CPU的未来发展分析

CPU发展的几个重要里程碑:

- 里程碑0:CPU的出现。基于简单运算指令的通用处理器,实现软件和硬件的完全解耦。从此后,软件作为独立的工作领域而存在,软件开发人员不用关心硬件细节。

- 里程碑1:多核CPU,从串行计算走向并行计算。

- 里程碑2:VT-x和VT-d等CPU硬件虚拟化技术,实现无性能损耗的多租户多系统的独立运行;

- 里程碑3:AIA技术的出现,通过AIA,支持独立或集成加速器,并且规范加速器的接口/架构和生态。

Sapphire Rapids的出现,第一次从CPU的视角,试图统一各种加速器和CPU的控制和数据交互方式,也即加速器呈现给Host CPU的架构。未来,AIA的方式能否成功,大家拭目以待。

硬件加速,不管是独立或集成的加速引擎/芯片,都是可行的路径。但抛开具体的芯片实现,在架构上,硬件加速的形态会再往何处发展?这里我们抛砖引玉:

- 标准的交互(Host CPU和加速器的接口或称为架构),统一加速器架构。可能无法把不同类型的加速器统一,但同类型的架构走向统一。

- 标准交互的同时,需要开放,需要跟CPU架构解耦,可以跨不同的CPU架构实现同样的交互协议;

- 基于标准的交互,基于一定的机制,要实现业务应用的跨处理器类型运行。

Intel Sapphire Rapids,代表着CPU的一个重要的发展趋势是:CPU芯片不断融合各类加速器核,使得自己成为更加综合和均衡的新型处理器。

6 CPU、GPU、DPU,从竞争/协同到混战/融合

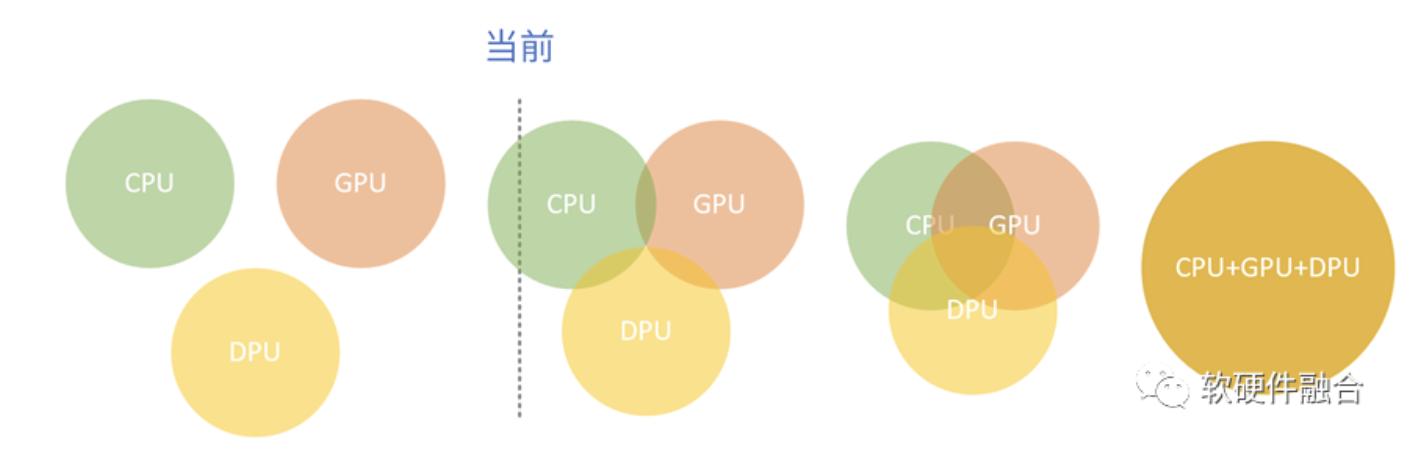

目前,CPU、GPU和DPU,数据中心的三大芯片,从“井水不犯河水”,走向“跨越边界,侵入对方领地”的混战阶段。

CPU、GPU和DPU,既是协同的关系,又是竞争的关系。三者处于一个动态平衡的状态,在协同中竞争,在竞争中协同。这个趋势不断发展,走向更加深度地协同甚至融合。

从CPU单个处理器的“合”,走向众多加速器的“分”,再“从分到合”,逐步融合成一个新型的超级处理器。

(全文完)

来源:软硬件融合

微信公众号:

相关文章推荐

更多软硬件技术干货请关注软硬件融合专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。