【爱集微点评】赛昉科技的RISC-V专利,在重命名阶段增加余数指令加速单元,通过余数指令的目的寄存器映射到除法指令写余数的物理寄存器,取到除法指令产生的余数,以此提升余数指令执行的效率。

集微网消息,近日国内首款基于RISC-V芯片的工业防火墙取得阶段性成果,而产品主要基于赛昉科技自研的RISC-V芯片。

微处理器的架构伴随着半导体工艺经历了蓬勃的发展。从单核到物理多核及逻辑多核、从顺序执行到乱序执行、从单发射到多发射等等,尤其在服务器领域,不断的追求处理器的性能。随着数据中心和科学计算的要求越来越高,对除法及余数指令的性能要求也越高,同时指令中的除法和余数指令比重逐渐升高。除法和余数指令执行周期比较长,同时执行周期与数据相关,执行周期可变,这些因素对CPU的性能影响很大。

为此,赛昉科技于2021年1月18日申请了一项名为“一种RISC-V指令集余数指令的实现方法及系统”的发明专利(申请号:202110062056.X),申请人为广东赛昉科技有限公司。

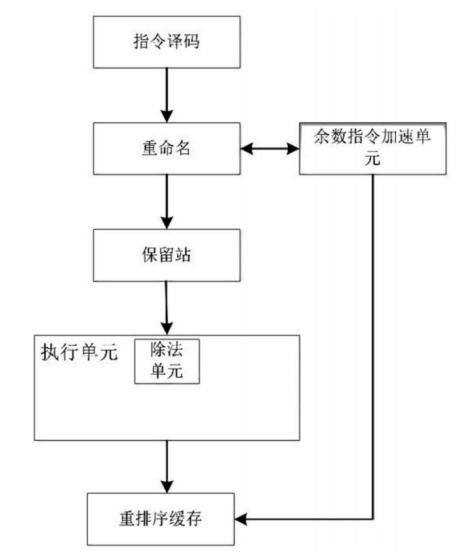

图1 余数指令实现架构图

图1是本发明提出的余数指令实现架构图,该方法在重命名阶段通过增加一个余数指令加速单元实现余数指令的功能。当除法和余数指令配对出现时,余数指令不需要发射到后续除法执行单元,而是通过余数指令的目的寄存器映射到除法指令写余数的物理寄存器,取到除法指令产生的余数。

在乱序执行的CPU中,指令从取指单元进入指令译码单元,进行指令译码。译码完成后的指令在重命名单元进行目的寄存器的重命名,并且在重命名阶段对余数指令进行优化。如果余数指令不满足优化条件时,重命名之后的指令进入保留站后,进入执行单元执行。执行完成后的指令通过重排序缓存提交,并且释放在重命名阶段分配的除法指令编码缓存等资源。

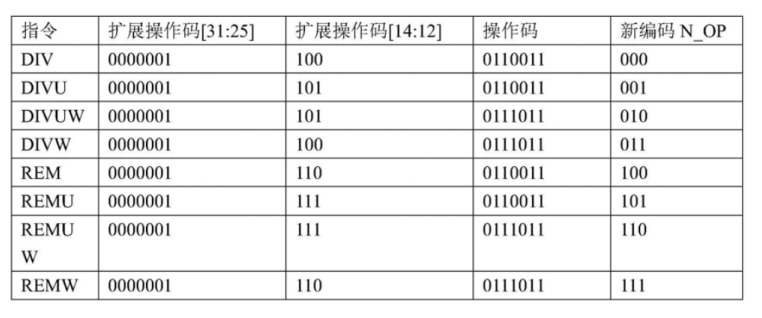

表1 除法与余数指令编码

表1为除法与余数指令编码表,在指令译码阶段产生除法指令和余数指令的一个新操作码N_OP。对除法和余数指令的N_OP编码,除法指令和余数指令可以配对的组合为:000与100,001与101,010与110和011与111。N_OP中除法指令的编码称为DIV_N_OP;N_OP中余数指令的编码称为REM_N_OP。

余数指令加速单元中的除法指令编码缓存保存了需要配对的除法指令及相关信息。当除法指令写入到除法指令编码缓存的时候,需要判断是否有空闲的entry,将除法指令的信息写到对应的entry。当余数指令的标识rem_val有效时,即表示当前指令为余数指令。余数指令的编码REM_N_OP匹配除法指令编码缓存中的除法指令编码DIV_N_OP。同时如果有效位valid有效,那么该条余数指令匹配成功,即div_rem_hit为1。余数指令目的寄存器rem_rd映射到除法物理寄存器rem_phy_reg。

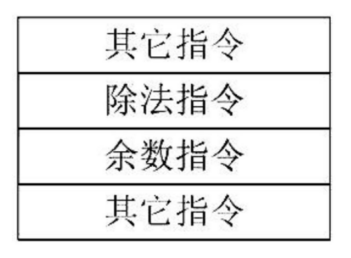

图2是除法与余数指令配对相邻图

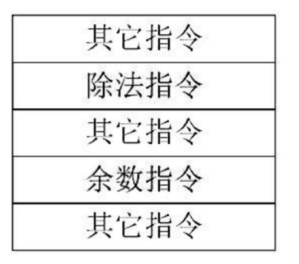

图3是除法与余数指令配对不相邻图

图2、3为除法与余数指令配对相邻图和不相邻图。在重命名阶段的时候,如果流水线中的除法和余数指令存在配对,并且除法和余数指令之间不存在/存在其它指令,那么配对指令中的余数指令都不需要执行,即该余数指令不需要发到后续的流水线,余数指令的功能完全被配对的除法指令实现。

简而言之,赛昉科技的RISC-V专利,在重命名阶段增加余数指令加速单元,通过余数指令的目的寄存器映射到除法指令写余数的物理寄存器,取到除法指令产生的余数,以此提升余数指令执行的效率。

赛昉科技成立于2018年,提供全球领先的基于RISC-V指令集的CPU IP、SoC、开发板等系列产品和解决方案,是中国RISC-V软硬件生态的领导者。成立至今,赛昉科技已相继推出了多款基于RISC-V的产品,而这次国内首款基于RISC-V芯片的工业防火墙的成果,也再次印证了赛昉科技在RISC-V领域的强大实力。