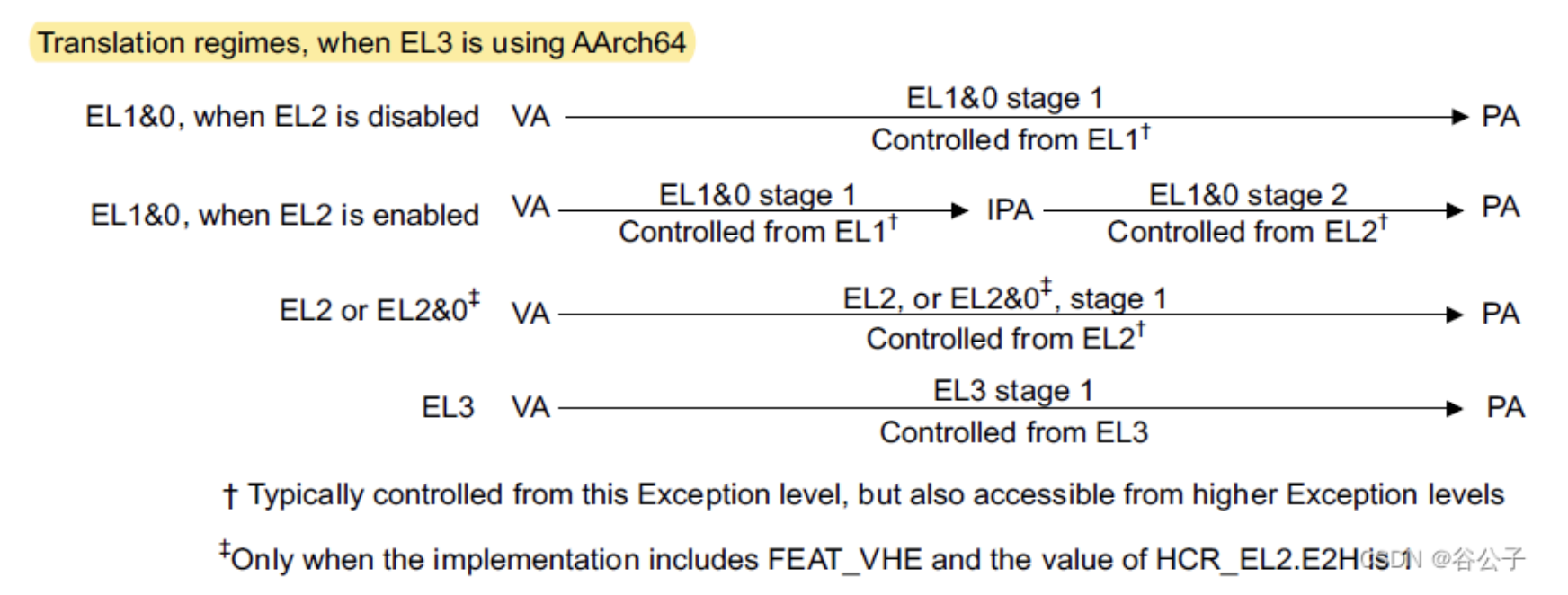

当EL3使用AArch64时,ARMv8 architecture定义了如下translation stages和translation regimes:

上图是在implementation包含了所有exception levels情况下的translation regimes和translation stage。

如果某一implementation不包含所有的exception levels,那么具体的address translation scheme也会跟着变化的。ARM architecture里规定:

—— 如果implementation不包含EL3,那么它将只有一个security state,其中MMU控制等价于secure state下的MMU控制。

—— 如果实现不包含EL2,那么分两种情况分析:1.如果也不包含EL3,MMU只简单提供一个EL1&0 stage 1 translation regimes。2.如果包含EL3,那么MMU会在每个security state下提供一个EL1&0 stage 1 translation regimes。

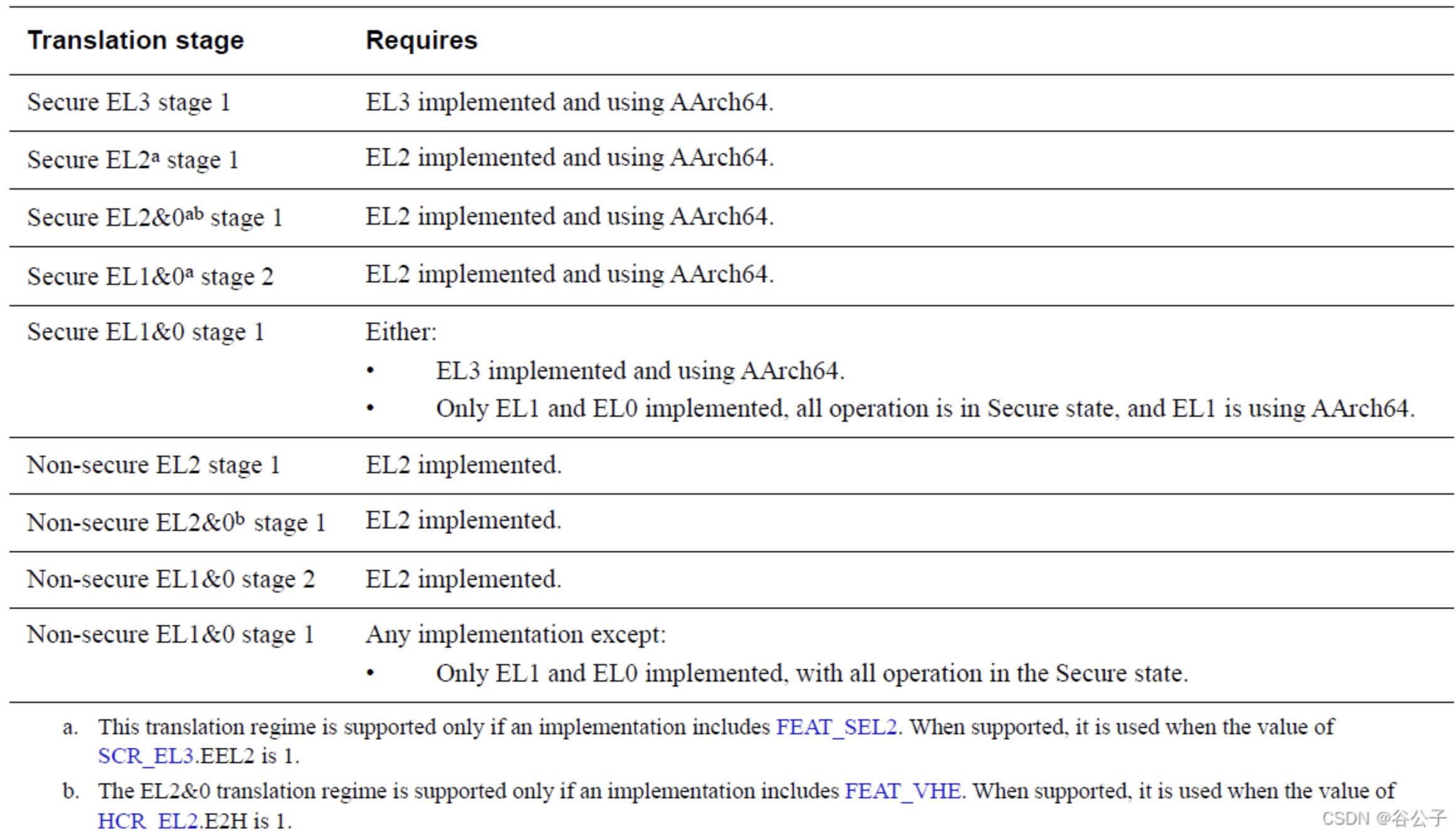

下表列出了支持的translation stages如何依赖于implementation实现的Exception levels,并且在某些情况下,依赖于最高实现的Exception level的execution state是AArch64还是AArch32.

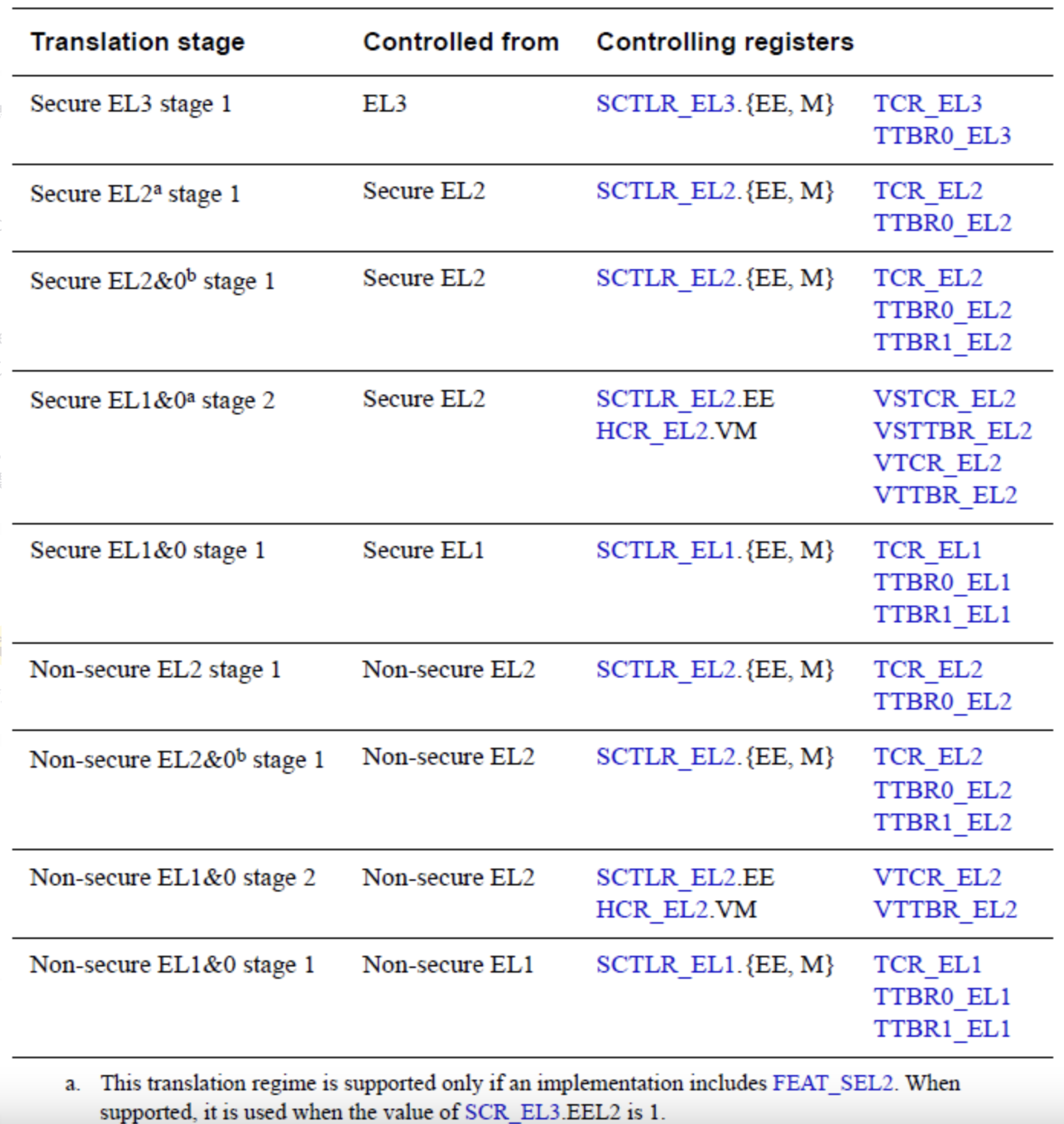

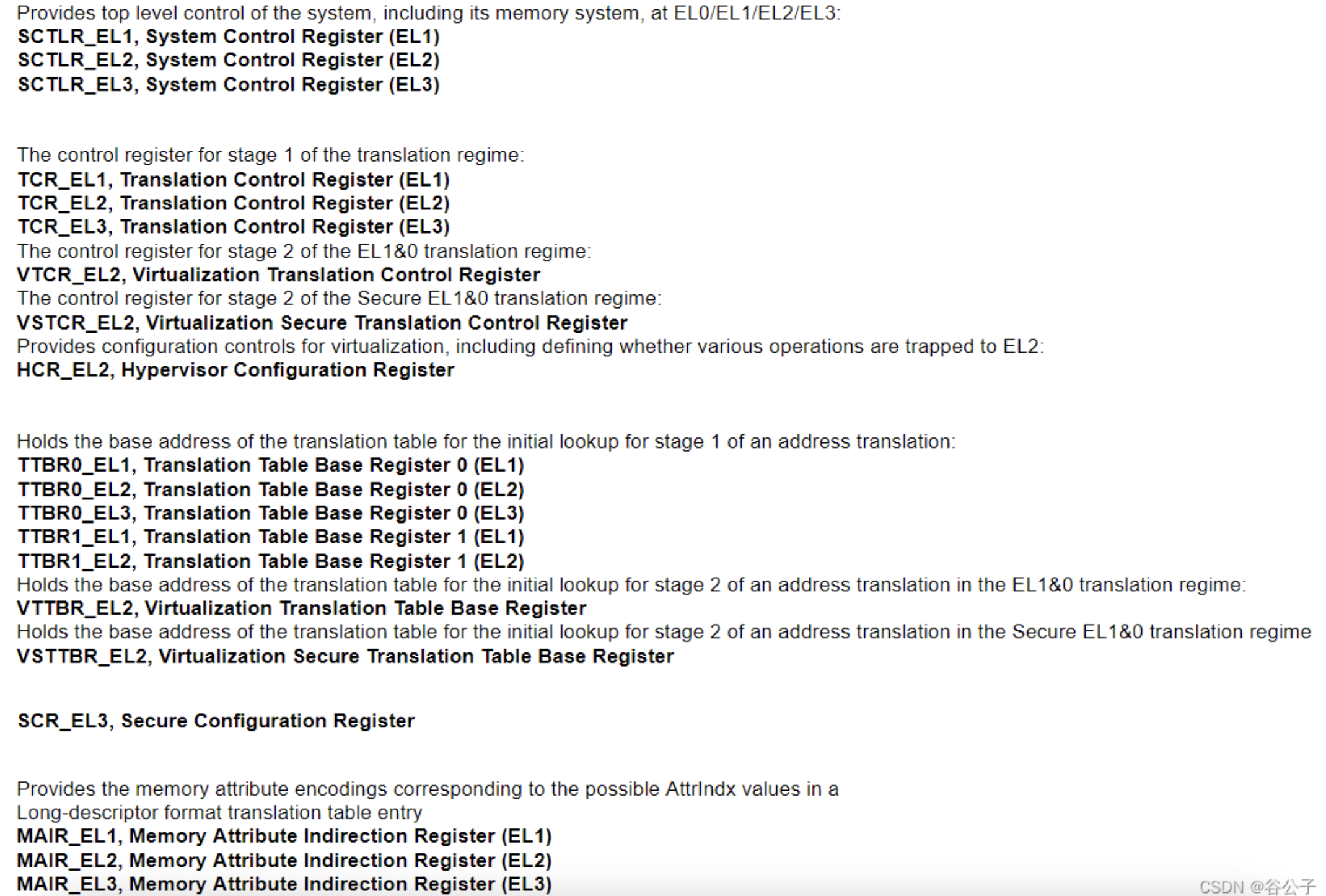

对于每个支持的address translation stages,在AArch64 state下的相关控制有:

—— System register控制是否使能对应的address translation stage: SCTLR_ELx.M or HCR_EL2.VM。

—— System register控制translation table lookup的endianness:SCTLR_ELx.EE。

—— Translation Control Register(TCR_ELx)控制对应的translation address stage。对于stage 1来说,TC_ELx控制。对于stage 2来说,VTCR_EL2、VSTCR_LE2和HCR_EL2控制。VTCR_EL2和HCR_EL2作用于secure或non-secure stage 2,VSTCR_LE2作用于secure stage 2。

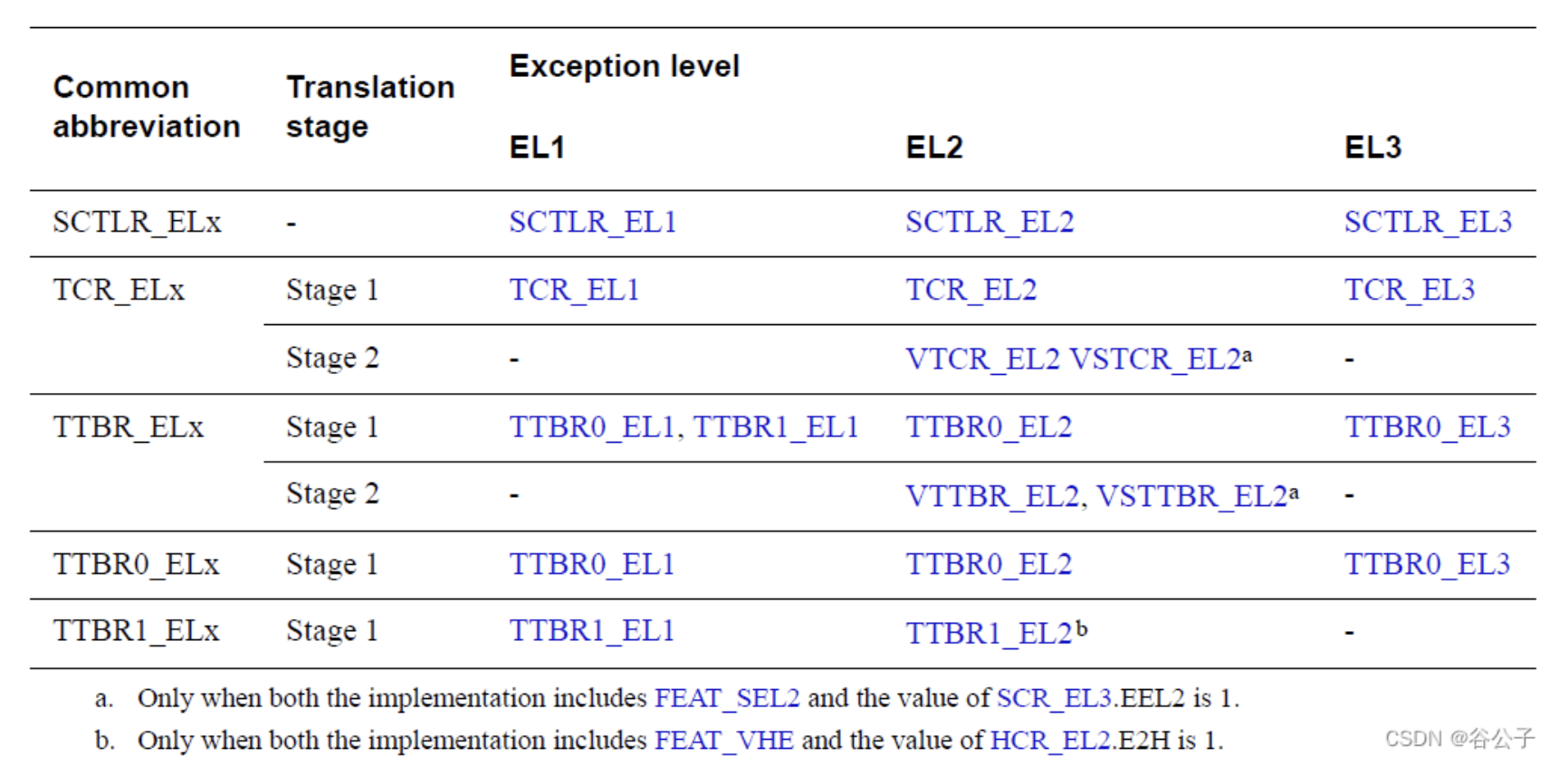

—— 如果一个address translation stage支持两个VA ranges的话,那么对于这个stage会有两个TTBR_ELx,各自分别对应一个VA range。TTBR0_ELx指向以0x0000000000000000为起始地址的address range。TTBR1_ELx指向以0xFFFFFFFFFFFFFFFF为终点的address range。支持两个VA ranges的translation stage只有EL1&0 stage 1和EL2&0 stage 1,其它的stage1或stage2都是只支持1个VA ranges。对于支持1个VA range的stage 1,只有TTBR0_ELx指向以0x0000000000000000为起始地址的address range。对于stage 2只支持1个VA range,因此只有VTTBR_EL2, VSTTBR_EL2指向以0x0000000000000000为起始地址的address range。VTTBR_EL2用于secure或non-secure stage 2,VSTTBR_EL2只用于secure stage 2。

对于这些registers和translation stage,以及Exception level的关系如下表:

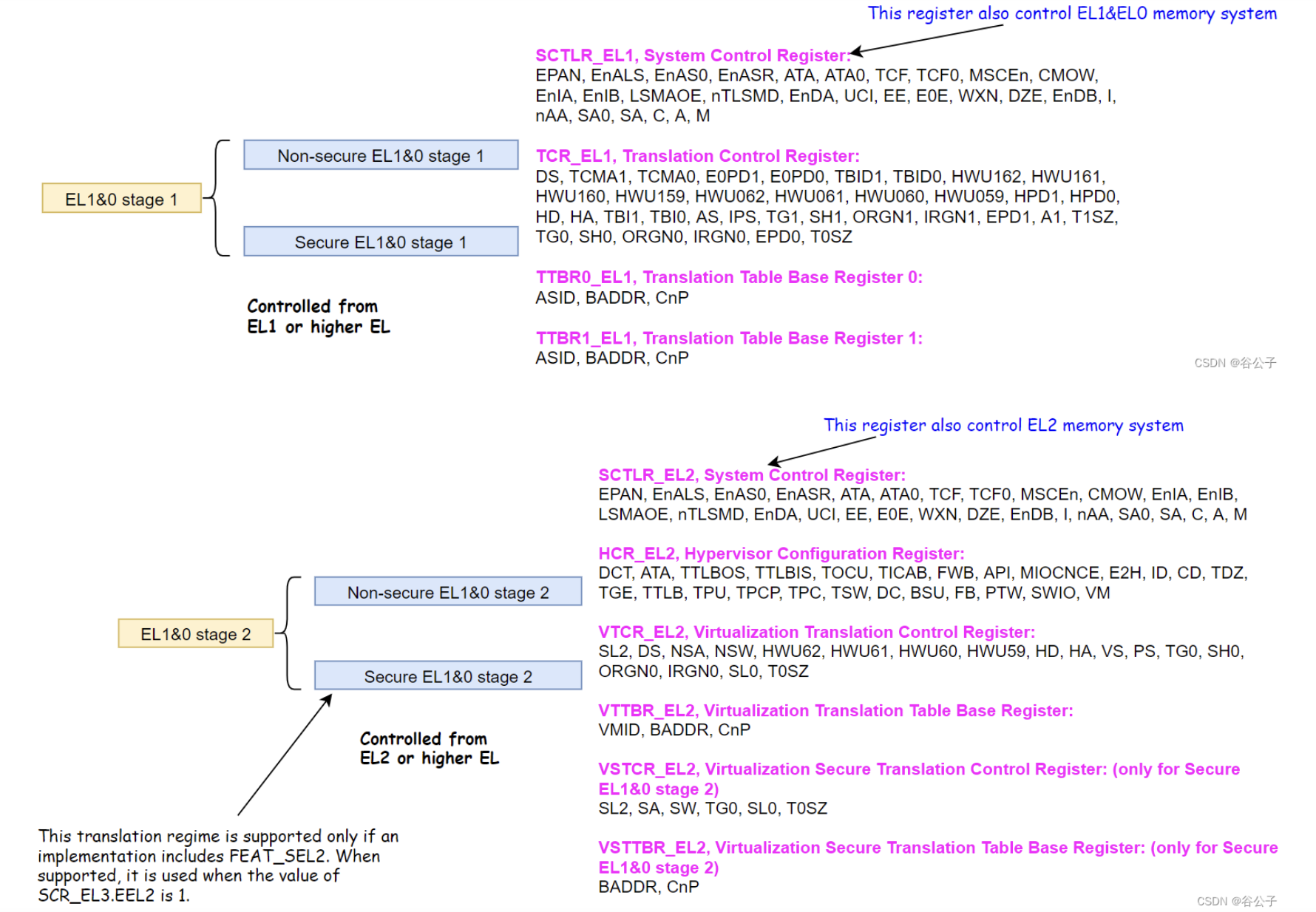

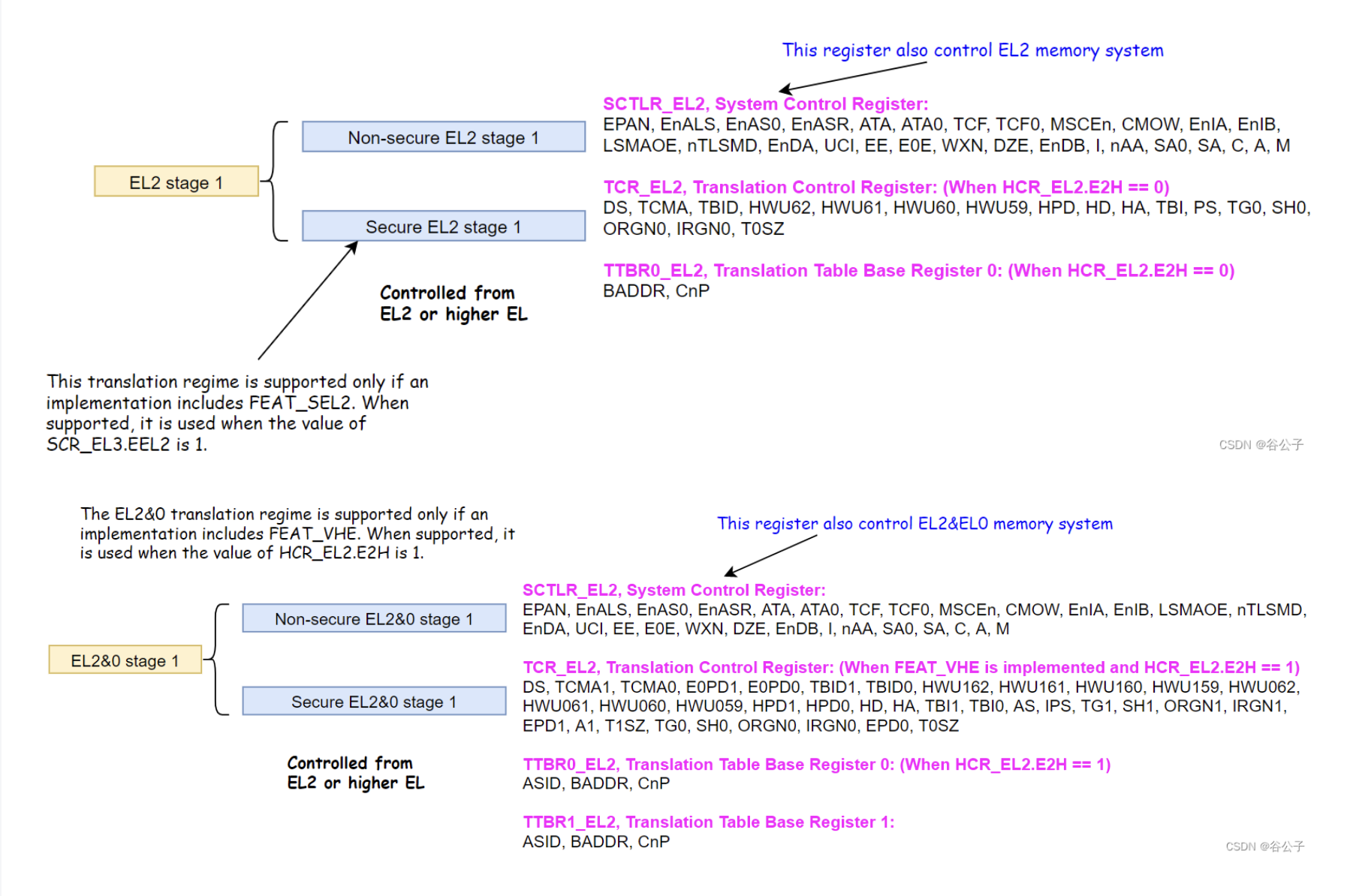

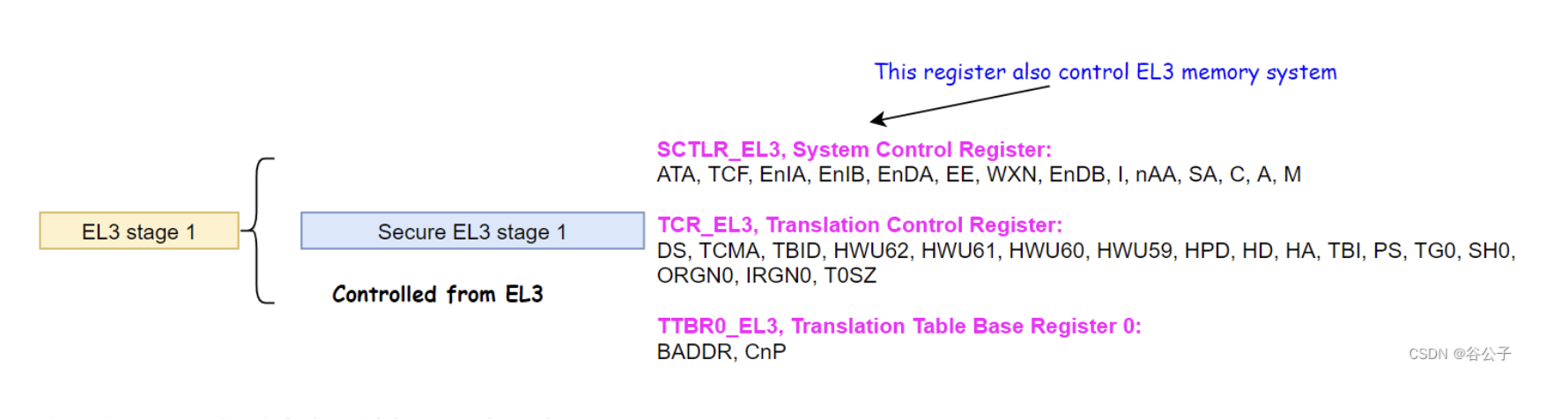

下面用图画的形式列出这些translation regime和registers/register fields的关系,并且按功能给它们归类。一共有9个translation stage:Non-secure EL1&0 stage 1,Secure EL1&0 stage 1,Non-secure EL1&0 stage 2,Secure EL1&0 stage 2,Non-secure EL2&0 stage 1,Secure EL2&0 stage 1,Non-secure EL2 stage 1,Secure EL2 stage 1,Secure EL3 stage 1。具体如下:

关于这些MMU相关寄存器按如下分类列出:

作者:谷公子

文章来源:CSDN

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。