【爱集微点评】中科海芯公开的芯片测试方案,该方案通过先测试待测芯片的待测存储器是否合格,仅在合格时对待测芯片的待测逻辑电路进行测试,从而节省测试时间。此外,测试模块集成在待测芯片内部,不需要额外的测试机台和测试软件,也可以节省生产成本。

集微网消息,目前,为了检测芯片是否合格,芯片厂商们一般在芯片生产后对晶圆进行cp测试以挑选出合格芯片进行封装,在封装完成后采用ATE机台进行FT测试或抽测以筛除封装失败的芯片,然后再供货给产品设计厂商。

产品设计厂商在芯片焊装完一般还需要再进行系统测试,以筛除焊接过程中失效的产品,然后将最终通过测试的产品交付用户。

为了应对不同行业的测试标准,芯片厂商通常会额外加入测试固件。例如,采用开发测试软件的方式,对芯片内部各项硬件功能进行遍历以检验已经焊装的芯片各项功能是否合格。这不仅会增加开发成本,且测试软件无法对芯片内已经固化的电路逻辑进行所有测试,即测试软件无法保证测试的覆盖率。

为此,中科海芯在2021年11月17日申请了一项名为“芯片测试方法和装置”的发明专利(申请号:202111358332.3),申请人为北京中科海芯科技有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项技术方案吧。

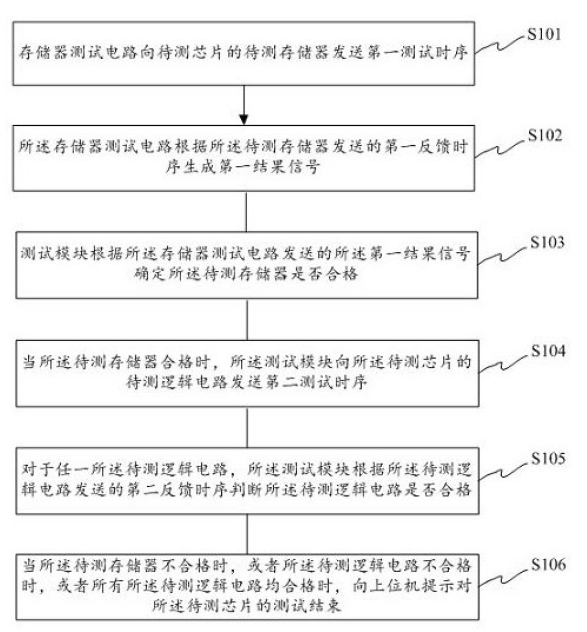

如上图,为该专利中公开的芯片测试方法的流程图。首先,存储器测试电路向待测芯片的待测存储器发送第一测试时序,存储器测试电路根据待测存储器发送的第一反馈时序生成第一结果信号,第一反馈时序由待测存储器根据第一测试时序生成。第一结果信号包括第一成功结果信号和第一失败结果信号,如果匹配度不小于第一预设阈值时,设置为成功结果信号,否则为失败结果信号。

其次,测试模块根据存储器测试电路发送的第一结果信号确定待测存储器是否合格。当待测存储器合格时,测试模块向待测芯片的待测逻辑电路,发送第二测试时序。接着,对于任一待测逻辑电路,测试模块根据待测逻辑电路发送的第二反馈时序判断待测逻辑电路是否合格,第二反馈时序由待测逻辑电路根据第二测试时序生成。

最后,当待测存储器不合格或者待测逻辑电路不合格时,或者所有待测逻辑电路均合格时,向上位机提示对待测芯片的测试结束。该匹配过程中,需要对第二反馈时许进行CRC校验计算,根据校验结果与对应的第二标准时序的匹配度判断待测试逻辑电路是否合格。

因此,该方案通过先测试待测芯片的待测存储器是否合格,当待测存储器合格时对待测芯片的待测逻辑电路进行测试,不合格时则终结测试,从而可以不必对待测芯片的其余待测逻辑电路进行测试,可以节省测试时间。

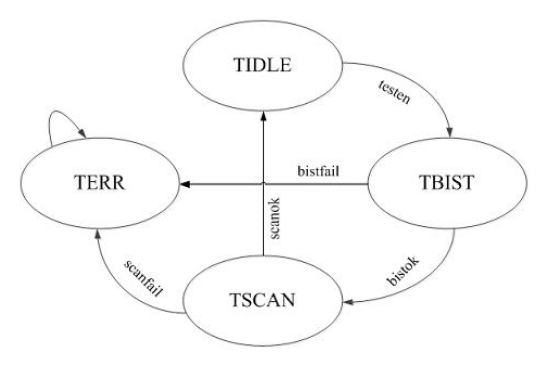

如上图,为该专利中展示的状态控制子模块的模式转换示意图,测试状态包括空闲状态TIDLE、存储器测试状态TBIST、逻辑电路测试状态TSCAN和测试错误状态TERR。例如,在初始阶段,即在未启用第一芯片测试模式或者未对待测芯片进行测试时,状态控制子模块处于空闲状态,此时不向待测芯片发送任何信号。

当启用第一芯片测试模式时,状态控制子模块可以由空闲状态TIDLE先转换为存储器测试状态TBIST,当待测芯片的待测存储器测试合格时,状态控制子模块可以转换为逻辑电路测试状态TSCAN,此时可以通过上述实施例提供的芯片测试方法对待测芯片的待测逻辑电路进行测试。

当待测芯片的待测存储器测试不合格时,或者当待测芯片的任一待测逻辑电路测试不合格时,状态控制子模块则转换为测试错误状态TERR。当待测芯片的所有待测逻辑电路均合格时,状态控制子模块即转换为空闲状态TIDLE,此时对待测芯片的测试结束。当状态控制子模块转换为测试错误状态TERR时,表明待测芯片不合格,此时对待测芯片的所有测试工作均停止。

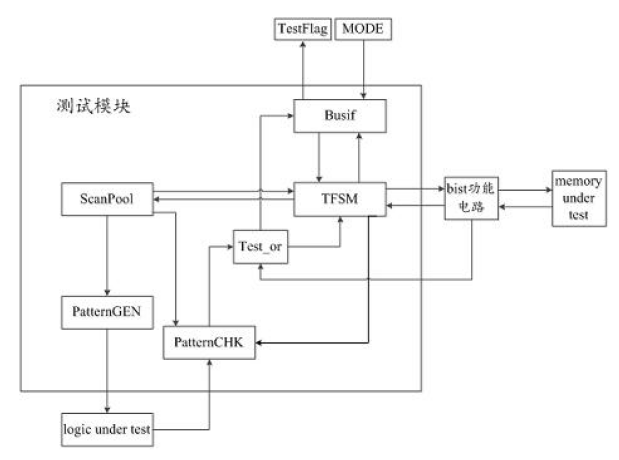

最后,如上图,为该芯片测试装置的结构细节图。当测试使能寄存器转换为第一模式,或者当总线控制子模块Busif监测到测试模式选择管脚MODE转换为第二模式时,总线控制子模块即向状态控制子模块TFSM发送测试触发信号testen和测试模式信号testmode,以触发状态控制子模块进入测试模式,并根据测试模式信号转换测试状态。

以上就是中科海芯公开的芯片测试方案,该方案通过先测试待测芯片的待测存储器是否合格,仅在合格时对待测芯片的待测逻辑电路进行测试,从而节省测试时间。此外,测试模块集成在待测芯片内部,不需要额外的测试机台和测试软件,也可以节省生产成本。