【爱集微点评】普莱信智能的芯片封装专利,通过对点位轨迹速度曲线进行优化调节,降低总运动时间。同时限制允许激起能量强度值,能够提高芯片封装效率、防止速度规划超调、提高芯片封装控制的精度。

集微网消息,普莱信智能深耕半导体封装领域多年,近日,普莱信智能从15737家广东省创新型中小企业中脱颖而出,荣获广东省“专精特新”中小企业。

随着集成电路产业的快速发展和芯片制造工艺的不断提高,小型化、多引脚、细间距的芯片对其封装设备高加速运动系统的响应能力、定位精度、定位时间等伺服性能提出了更高的要求。芯片封装的快速高精度定位要求主要通过加速度、定位精度和运行时间三个方面的参数进行体现。但是,由于芯片封装控制系统具有短行程高加速高速高精度定位的特点,且位移相对固定,现有技术方案难以发挥作用。因此,亟需一种用于芯片封装控制的速度规划方法,以提高芯片封装精度、降低所需时间。

为此,普莱信智能于2021年4月7日申请了一项名为“芯片封装控制的速度规划方法及芯片封装控制装置”的发明专利(申请号:202110373352.1),申请人为东莞普莱信智能技术有限公司。

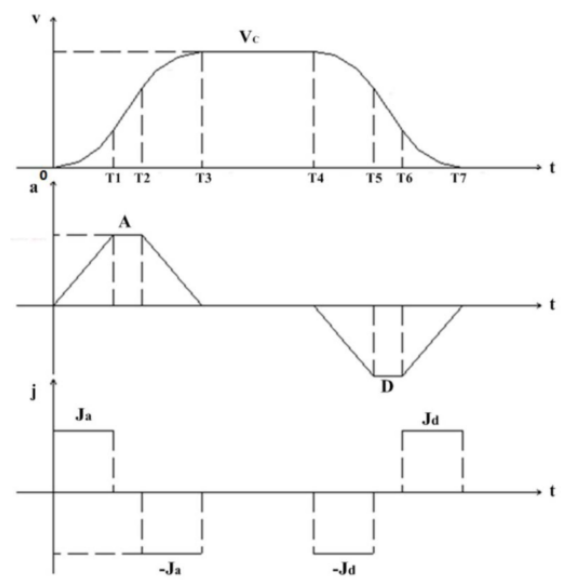

图1 芯片封装控制的速度规划方法示意图

图1为本专利提出的一种芯片封装控制的速度规划方法示意图,封装控制的点位轨迹速度曲线为非对称S曲线,点位的运动通过轴电机驱动。其中非对称S曲线按加减速特征划分为七个运行阶段:加加速段0T1、匀加速段T1T2、减加速段T2T3、匀速段T3T4、加减速段T4T5、匀减速段T5T6和减减速段T6T7。

实现的具体规划方法如下,首先设定插补周期、启动端插补周期数量、停止端插补周期数量、允许激起能量强度值、调节变化率上限、速度修改分辨率、加速度修改分辨率。根据如图1所示的各个参数间关系,设定初始速度Vs、结束速度Ve、最大速度Vmax、最大加速度A、最大减速度D、加加速度Ja、减加速度Jd、位移值S。

之后通过Vs、Vmax、A、D、Ja、Jd、S,计算点位轨迹速度曲线,获取总运动时间Tb;若是首次计算Tb,使Ta=Tb。接着根据插补周期、启动端插补周期数量、点位轨迹速度曲线,计算启动端各单个插补周期设备运行速度频率所激起的能量强度。然后计算得到各个插补周期的能量强度之和,并判断是否大于允许激起能量强度值,最后根据两者大小以及Ta、Tb的值对相关参数进行调节。

比如当能量强度之和大于允许激起能量强度值时对A、D、Ja、Jd进行优化调节,直至能量强度之和小于允许激起能量强度值,从而抑制芯片封装系统中轴电机的震动造成的残余振动,提高芯片封装控制的精度。此外,还可以调节A、D、Ja、Jd使总运动时间Tb减小,从而提高芯片封装效率。同时通过速度修改分辨率、加速度修改分辨率约束A、D、Ja、Jd的调节幅度,以此控制参数调节结果的变化率,防止速度规划超调。

简而言之,普莱信智能的芯片封装专利,通过对点位轨迹速度曲线进行优化调节,降低总运动时间。同时限制允许激起能量强度值,能够提高芯片封装效率、防止速度规划超调、提高芯片封装控制的精度。

普莱信智能在创立之初,就汇聚了运动控制、算法、机器视觉、直线电机、半导体设备和自动化设备领域的资深人士,希望在未来,普莱信智能可以继续通过国际级的先进技术来提高国内制造业水平,最终助力实现中国制造的智能化升级。