欢迎关注软硬件融合公众号:

编者按

ChatGPT等AI大模型的发展,对算力的需求每两个月增加一倍。

OpenAI每年的支出费用高达10多亿美金。

如果将ChatGPT部署到谷歌搜索中,需要512,820 个 A100 HGX服务器和总共4,102,568 个 A100 GPU,服务器和网络的总硬件成本超过1,000亿美元。

算力,成为制约AI发展的最关键因素。

如果算力能够大踏步地发展,在成本不变的情况下,把算力提升千倍万倍,比ChatGPT更高级别的智能就一定会出现。

如何能够千倍万倍地提升算力?

首先可以肯定的是,现有的各类大算力芯片肯定不行:做一个“裱糊匠”,把算力百分比提升,甚至数倍提升,是有可能的;但要想多个数量级的提升算力,“裱糊”的方式肯定是不行的。

要想千倍万倍地提升算力,必然需要全新的算力平台!

1 业务应用和算力基础

1.1 算力:数字经济的核心生产力

一切系统的运行,可以归一到计算。微观的计算是性能,宏观的计算是算力。也因此,算力在数字经济、数字社会和数字政府等领域得到广泛应用,算力已经在赋能千行百业。

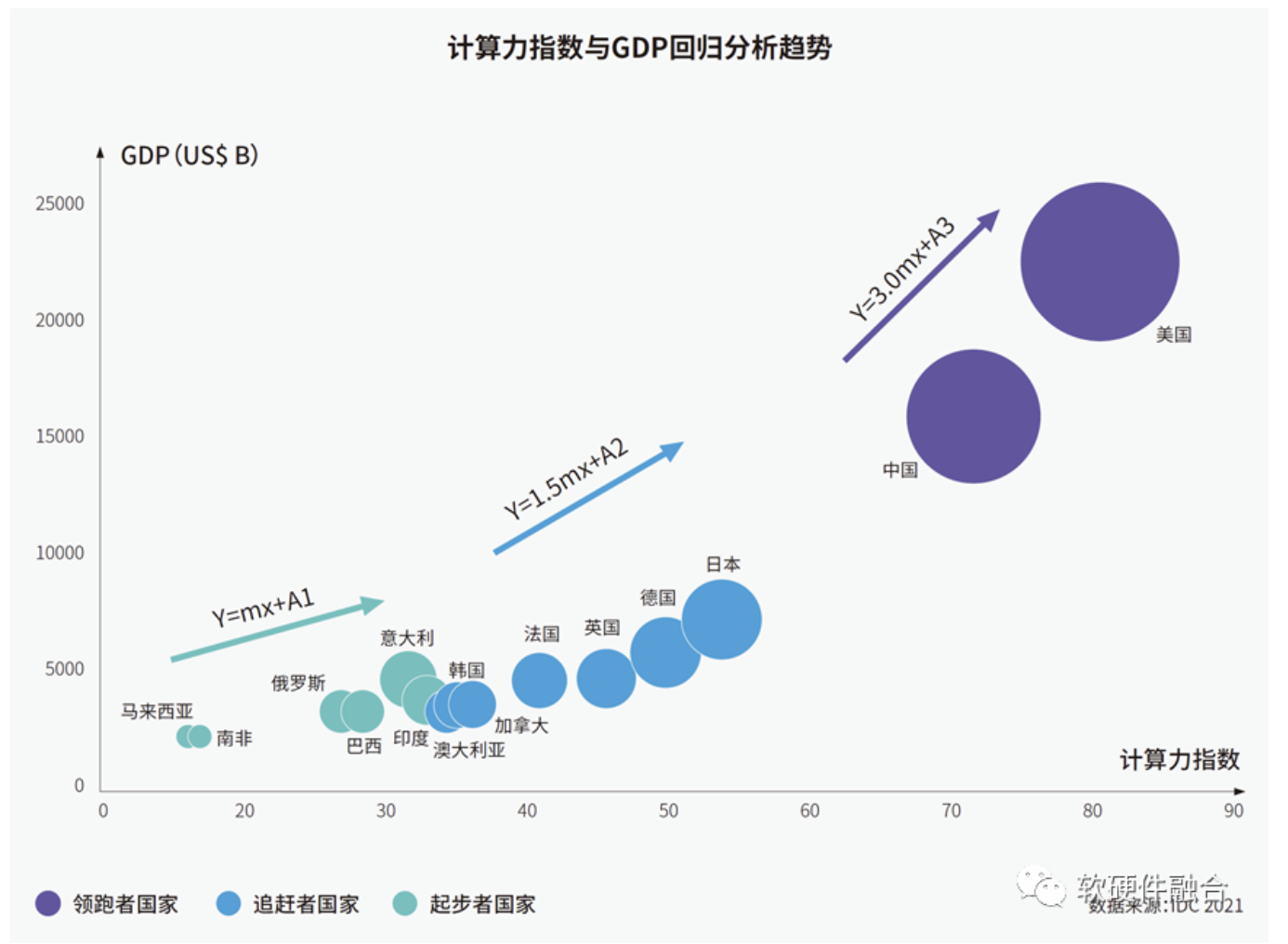

算力已成为继热力、电力之后新的关键生产力。计算力指数平均每提高1个百分点,数字经济和GDP将分别增长3.5‰和1.8‰。

如上图所示,算力规模与经济发展水平呈现出显著的正相关关系,算力规模越大,经济发展水平越高。

如果我们把这张图再扩展一下,随着计算力指数扩展到1000甚至10000,可以看到计算力指数其实和GDP是指数级关系的。随着数字经济的进一步发展,未来,算力会成为决定GDP发展的最核心因素。

文献1:IDC、浪潮、清华全球产业研究院联合发布的《2021—2022全球计算力指数评估报告》

文献2:《算力:数字经济的核心生产力》,方正梁,人民邮电报

1.2 ChatGPT等AI算力需求指数级增长

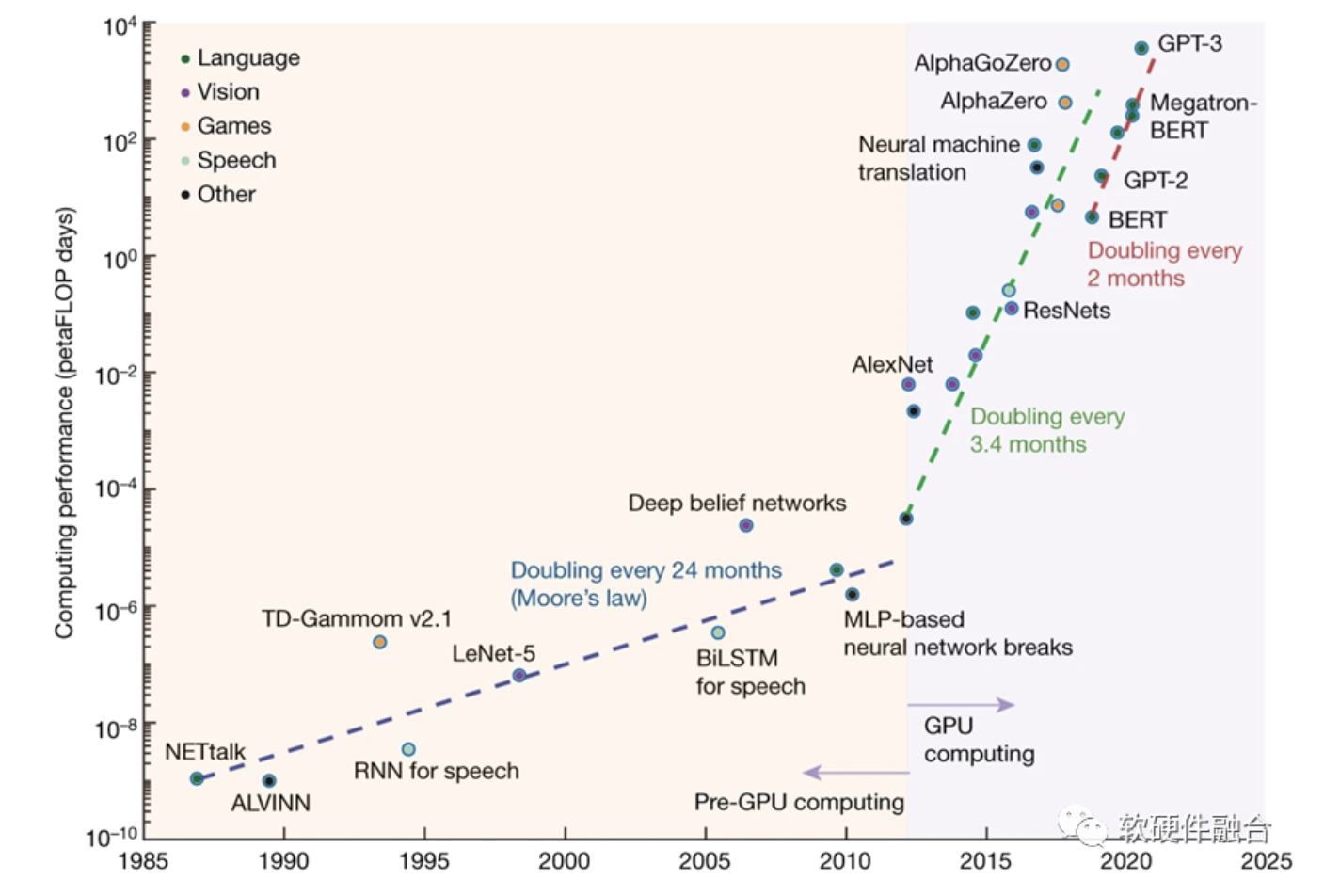

2012年之前,“深度学习”主要运行在CPU平台。2012年,随着AlexNet等深度学习模型的出现,对算力需求越来越多,也随着云计算的普及,基于GPU集群的超大规模深度学习人工智能技术进入高速发展阶段。

OpenAI在2018年发布的AI模型算力报告中指出:自2012 年以来,AI训练的算力呈指数级增长,每 3.4个月翻一倍。这意味着,从2012到2018年,AI算力增长了超过300,000倍。

与2012年的模型相比,2020年提出的模型需要600万倍的计算能力。据预测,从2023到2028年,AI所需算力将再增加100万倍。

ChatGPT的成功表明:大力真的可以出奇迹!

目前来看,是性能和成本,约束了ChatGPT的能力。

据测算,ChatGPT 的单次回复至少要花费 1 美分。在未爆发前100多万用户的时候,OpenAI 每天至少花费 10 万美元或每月 300 万美元用于运行成本。如今在数亿用户的情况下,其运行成本支出将超过50亿美金,这个成本对任何一家企业来说,基本上都无法接受。

如果将ChatGPT部署到谷歌搜索中,需要512,820 个 A100 HGX服务器和总共4,102,568 个 A100 GPU,服务器和网络的总硬件成本超过1,000亿美元。

算力成本高昂,限制了ChatGPT等AI模型的参数量,也限制了模型的智慧能力,还限制了模型的广泛使用。

如果有更低廉的成本,ChatGPT可以更加强大和智能,并且能得到更加广泛的普及。

文献1:Mehonic A, Kenyon AJ. Brain-inspired computing needs a master plan. Nature 2022;604(7905):255–260.

文献2:S. Zhu, T. Yu, T. Xu, H. Chen, S. Dustdar, S. Gigan, D. Gunduz, E. Hossain, Y. Jin, F. Lin et al., “Intelligent Computing: The Latest Advances, Challenges and Future”, INTELLIGENT COMPUTING, 3 Jan 2023, Vol 2

文献5:What is GPT-4?, https://blog.localseo.studio/...

1.3 自动驾驶汽车,又一个算力吞金兽

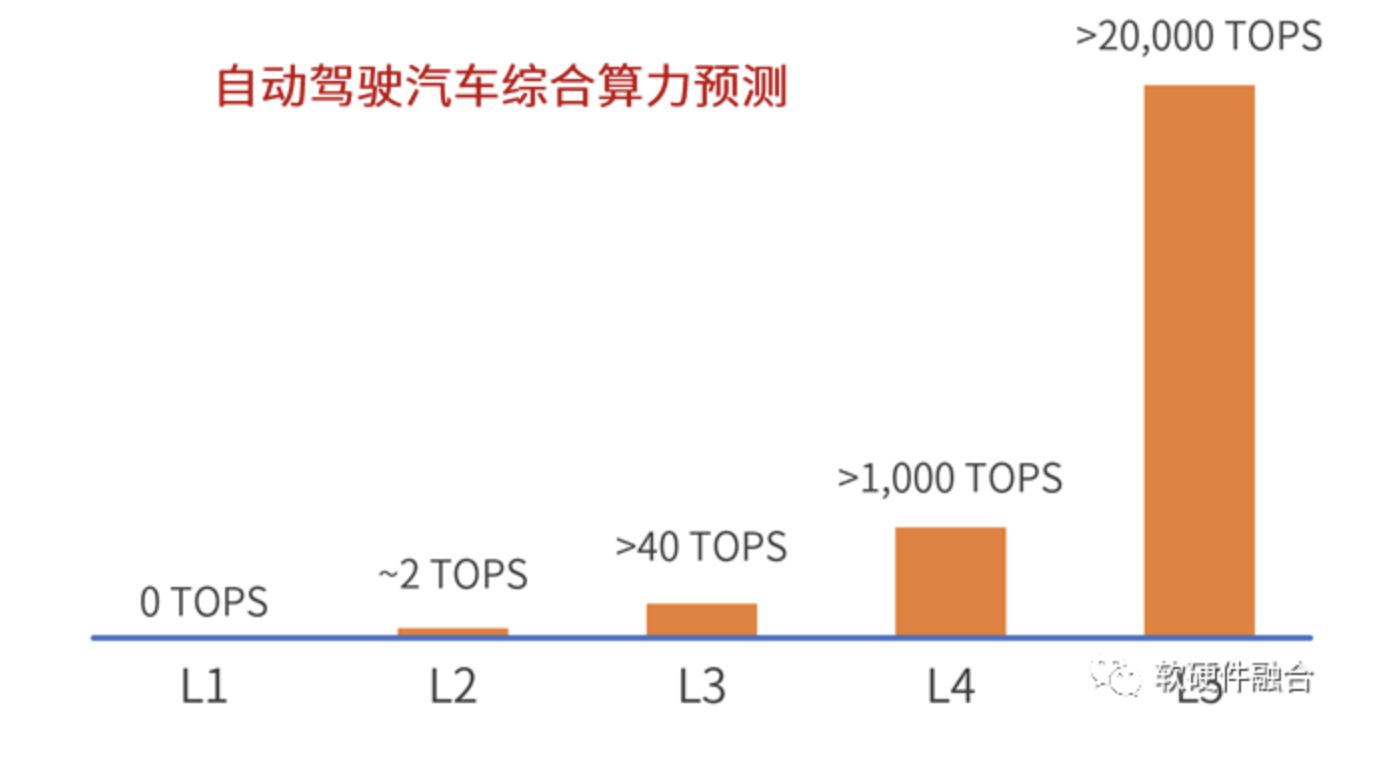

大部分观点认为:L5级别自动驾驶算力至少需要4,000 TOPS;也有部分观点认为:需要超过10,000 TOPS。

如果自动驾驶进入L5阶段,对娱乐的需求必然猛增。随着传感器数量越来越多、感知精度越来越高、AI模型越来越大,并且娱乐需求越来越丰富,各类需求蓬勃发展,必然需要算力爆发式增长。

多域融合的综合算力需求预计会超过20,000 TOPS。

算力需求是永无止境的,更多、更高的综合性需求,需要汽车平台算力快速并且持续不断地增长。

1.4 元宇宙,巨量算力支撑虚实融合

元宇宙需要源源不断的“算力能源”,算力支撑元宇宙虚拟世界的运行以及数字人等AI智能。要想实现元宇宙级别的体验,需将算力提升至少10,000倍。

这里举两个典型的案例。

案例一:沉浸感所需的16K效果,需要280.7Gbps带宽。目前的算力基础设施,还难以支撑如此高数据量的传输、处理和存储。

案例二:一方面,随着大模型持续发展,支撑单个数字人的AI算力需求急速增长;另一方面,随着元宇宙快速发展,数字人的数量也会猛增。也因此,元宇宙对AI算力的需求必然是多个数量级的提升。

文献1:https://www.zhihu.com/question/39630265/answer/134906922

文献2-3:电影《头号玩家》剧照、电影《失控玩家》剧照

1.5 问题的本质

整个问题的本质在于:落后的算力基础和先进的业务需求之间的矛盾!

硬件算力永远无法满足软件的需要。并且,随着AI、自动驾驶、元宇宙等场景和算法的逐渐成熟,业务算力需求和落后的算力基础之间的矛盾更加凸显,落后的算力基础限制了上层应用的进一步发展。

文献:电影《让子弹飞》剧照

2 计算架构的发展现状和面临的挑战

2.1 计算由单CPU串行走向多CPU并行

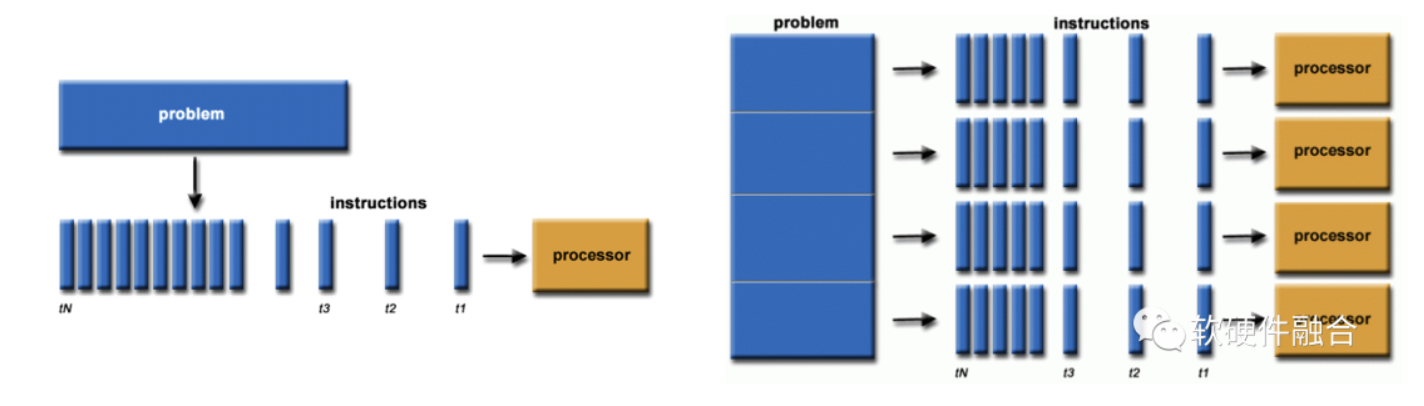

最开始是单核CPU流水线,在宏观视角下,单核CPU的指令流是串行执行的。

随着单核性能做到了极限,就不得不通过多核来提升性能,因此就从串行走向了并行,这里的并行是CPU同种架构的并行。

从单核到多核,不仅仅只涉及到硬件上的拼凑,也涉及到并行编程的软件开发难度,或者说并行计算的驾驭难度高于串行编程。

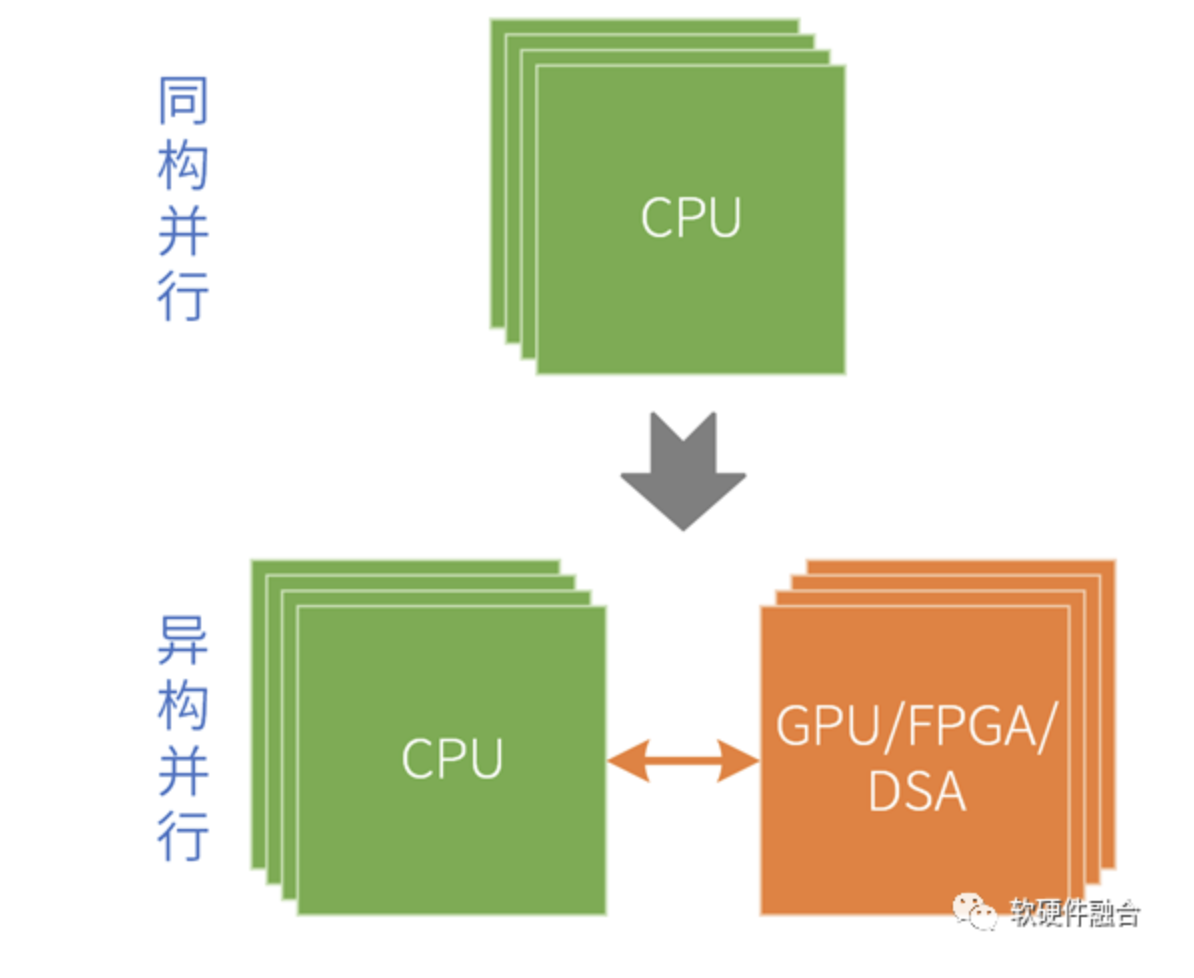

2.2 再从同构并行到异构并行

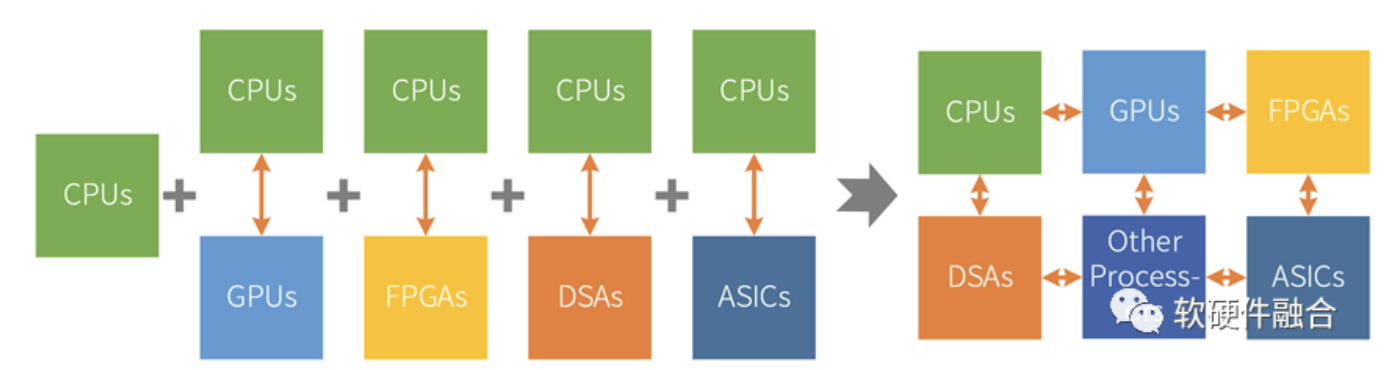

再后来,同构多核效率依然不够,所以就有了通过各种硬件加速器来进行性能加速。

但硬件加速器无法独立工作,需要有CPU的协助,所以就成了CPU+XPU的异构计算。

异构计算主要可以分为三类:基于GPU的异构计算,基于FPGA的异构计算,基于DSA的异构计算。

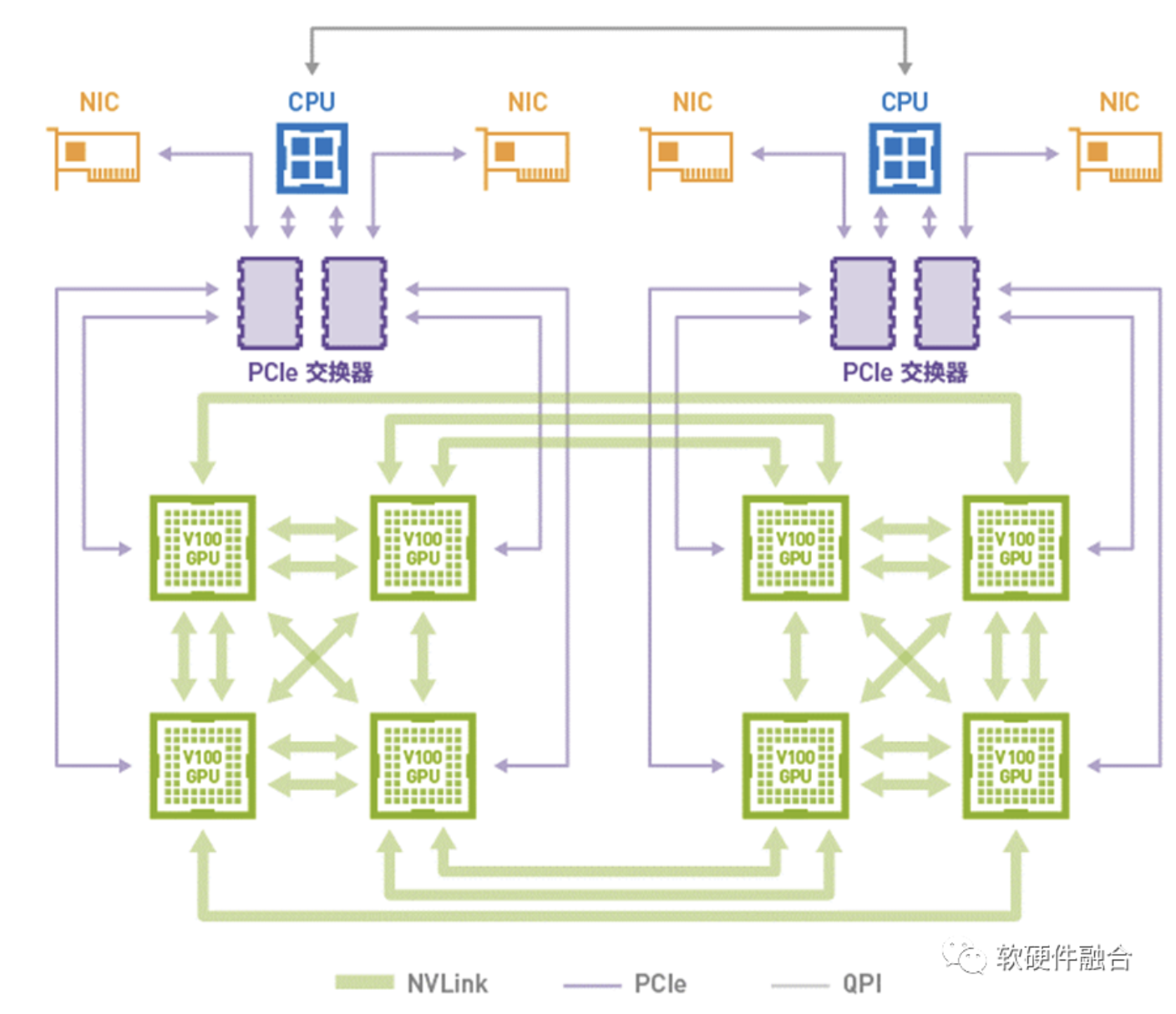

异构计算的最典型案例就是目前数据中心常见的GPU服务器,其他案例如:最开始做大规模HPC异构的天河超算系列,然后就是FPGA即服务的FaaS,以及谷歌TPU等AI加速。

GPU 并行计算性能效率比CPU高,并且场景覆盖较多,CUDA生态成熟。AI的兴起,让GPU成为最佳的平台。也推高NVIDIA股价,成为全球市值最高的IC公司。

GPU的劣势在于:性能效率比ASIC/DSA仍有很大差距;对一些轻量级异构加速场景,独立GPU显得太重。

2.3 异构计算存在的问题

异构计算面临的核心挑战,是一个悖论:系统越复杂,越需要灵活的处理器;但性能挑战大,越需要我们做定制加速,也就是越不灵活的处理器。这个矛盾的本质是,单一的处理器无法兼顾性能和灵活性。再怎么优化,仍是治标不治本。

异构计算中的Host CPU,已经性能瓶颈,摩尔定律失效。

异构计算中的加速处理器,决定了整个系统的性能/灵活性特征:

GPU灵活性较好,但性能效率不够极致;并且性能也逐渐瓶颈。DSA性能好;但灵活性差,难以适应算法的多变;架构碎片化;落地困难。

FPGA功耗和成本高,定制开发,落地案例少,通常用于原型验证。

ASIC功能完全固定,无法适应灵活多变的复杂计算场景。

FPGA和ASIC的异构加速落地较少,可以不用过分关注。

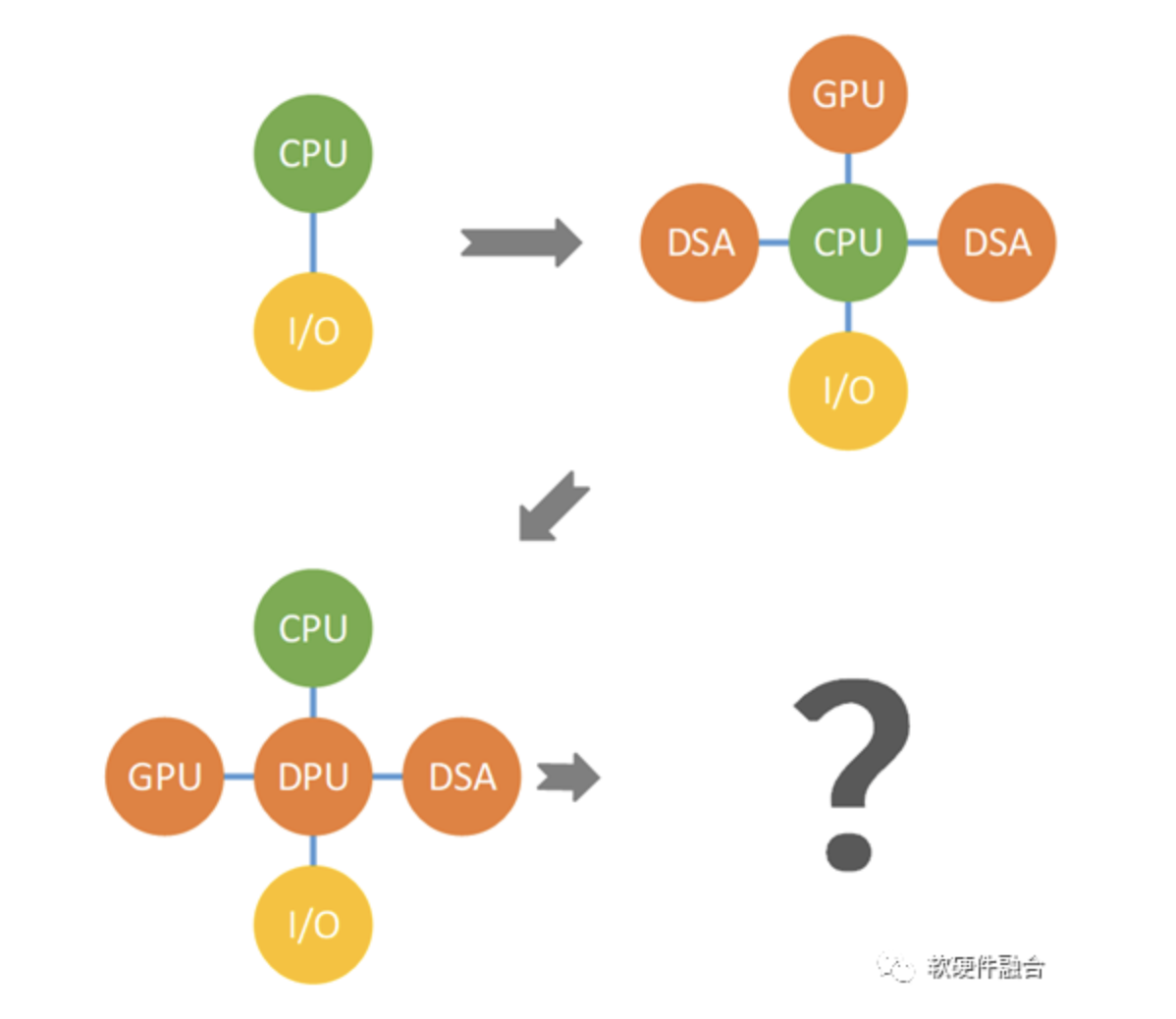

更多异构共存,还存在计算孤岛的问题:

- 每个领域加速处理器只考虑本领域问题,难以考虑全局协同。就如瞎子摸象,每个领域加速器只看到自己的“绳子”、“柱子”、“扇子”等,这些东西最终能否组织出用户所需要的“大象”?

- 各领域加速器之间的交互困难。如上图所示,每个加速器都通过CPU进行通信,CPU已经性能瓶颈,那么整个系统的性能上限也被锁死。

- 多芯片异构的中心节点问题。之前是CPU,性能不够,现在有了DPU这样的I/O加速器,但依然没有改变中心节点的架构问题。所有加速器交互通过中心节点,效率会降低,并且中心节点的处理能力就是整个系统的总处理能力,这约束了系统的处理性能。

- 单台(服务器)设备的物理空间有限,无法容纳多个物理的加速卡。需要整合。

2.4 小结:计算架构的发展阶段

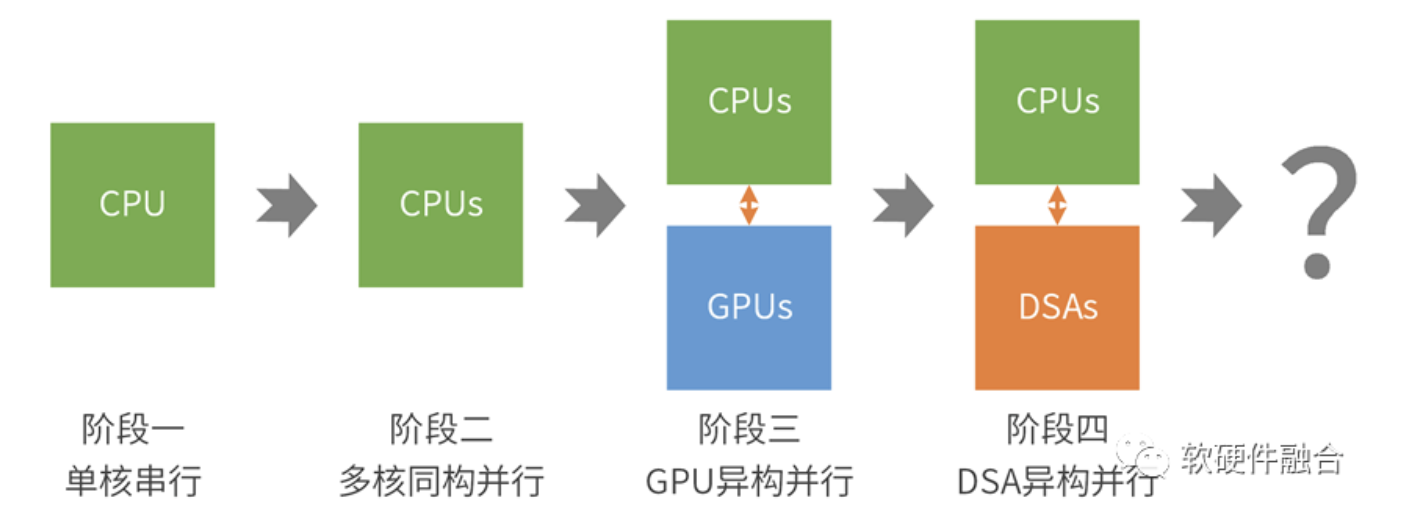

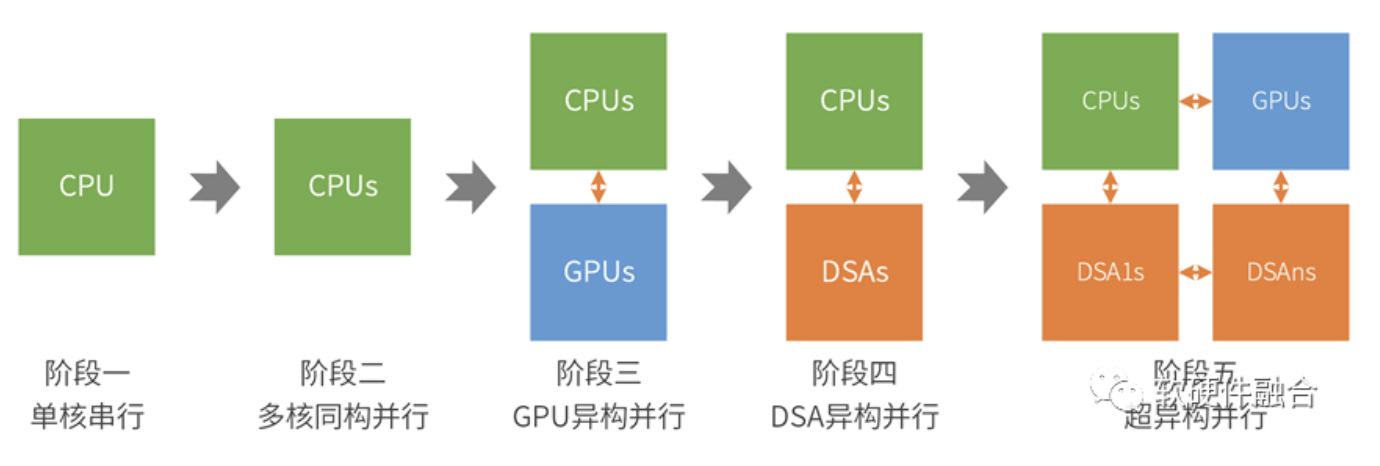

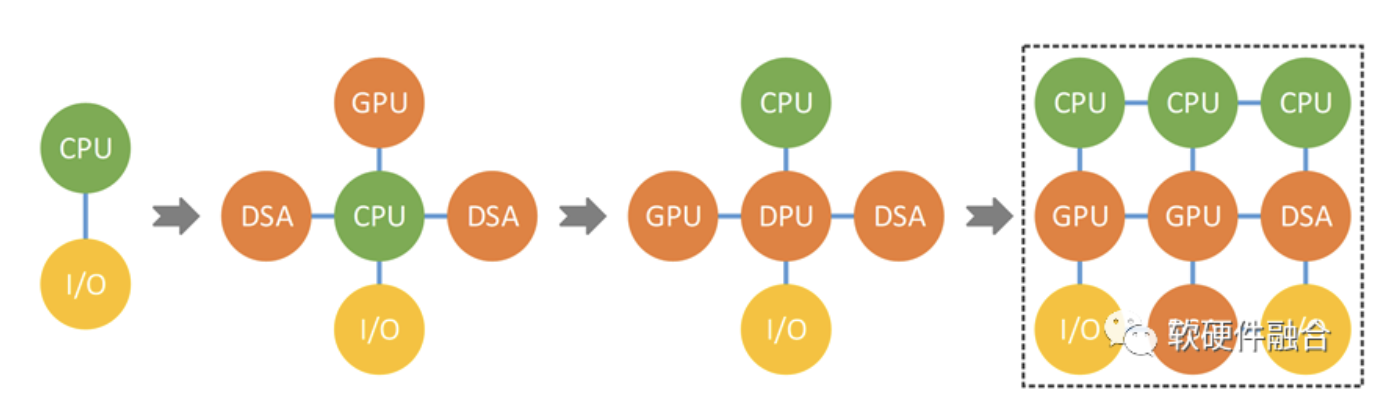

我们回顾一下从开始到现在,计算架构所经历的四个阶段:

- 阶段一:单CPU的串行阶段;

- 阶段二:多CPU的同构并行阶段;

- 阶段三:CPU+GPU的异构并行阶段;

- 阶段四:CPU+DSA的异构并行阶段;

第五个阶段,新一代的计算架构,应该是什么样子?我们将在后面的章节中揭晓。

3 从异构走向超异构

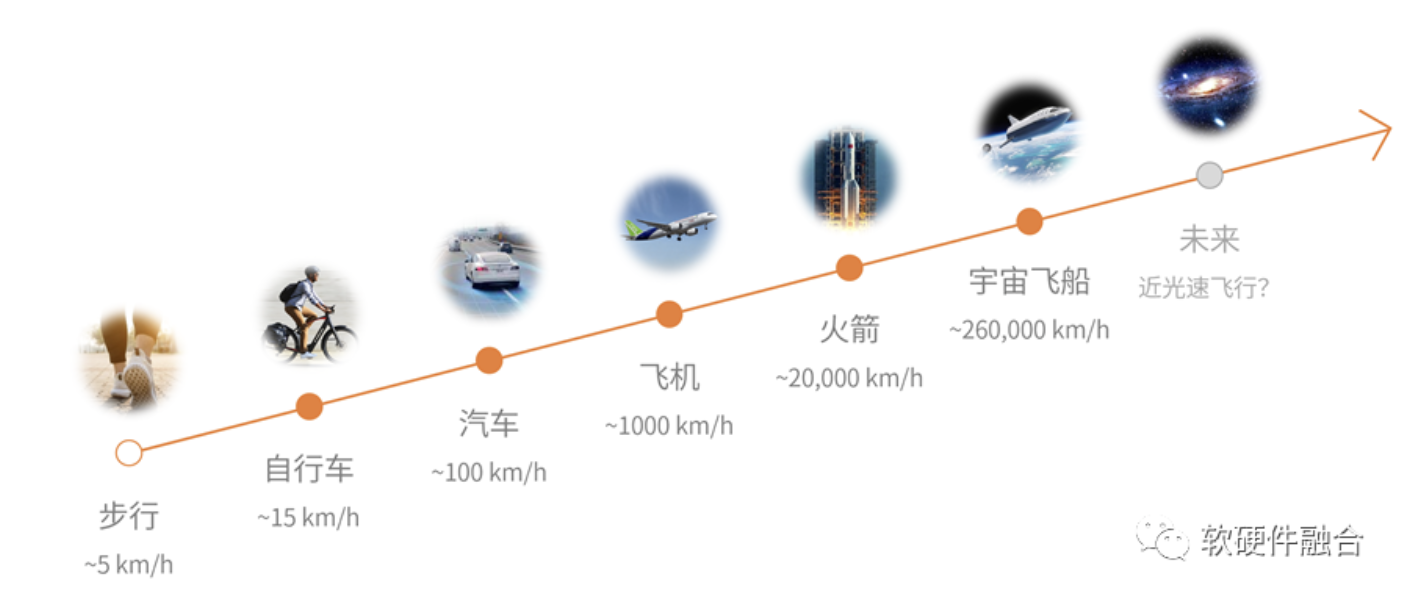

3.1交通工具——一个形象的例子

如果一个交通工具,需要达到200公里每小时,这是汽车的覆盖范围;如果需要500公里每小时,一些专用的汽车(如跑车)也是可以做到的;但要达到2000公里每小时,汽车平台肯定是无法做到的,此刻我们需要更高级别的交通工具平台——飞机。

更高的速度需求,就需要更高级别的交通工具;同样的,更高的算力需求,就需要更加先进的芯片(架构)。

3.2 工艺和封装创新,支撑更大规模的计算

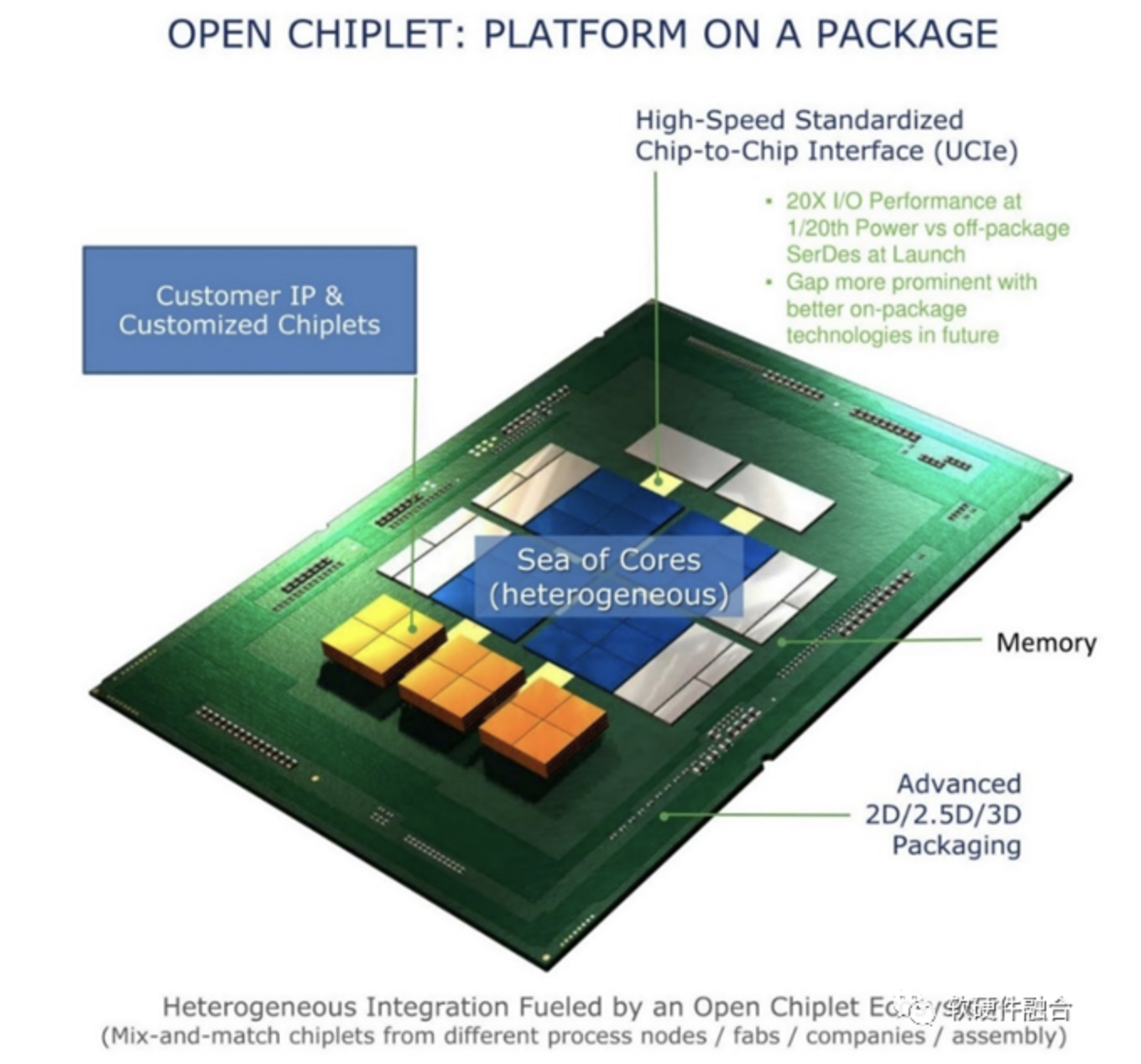

工艺进步,单芯片容纳的设计规模越来大;Chiplet封装,使得在单芯片层次,可以构建规模数量级提升的超大系统。

工艺持续进步、3D堆叠以及Chiplet多Die封装,在芯片上可以容纳更多的晶体管,也意味着芯片的规模可以越来越大。

未来,量子工艺,可以代替现在的CMOS工艺。有了量子门级电路的强力支撑,上层的芯片和软件生态,可以更加蓬勃地发展。

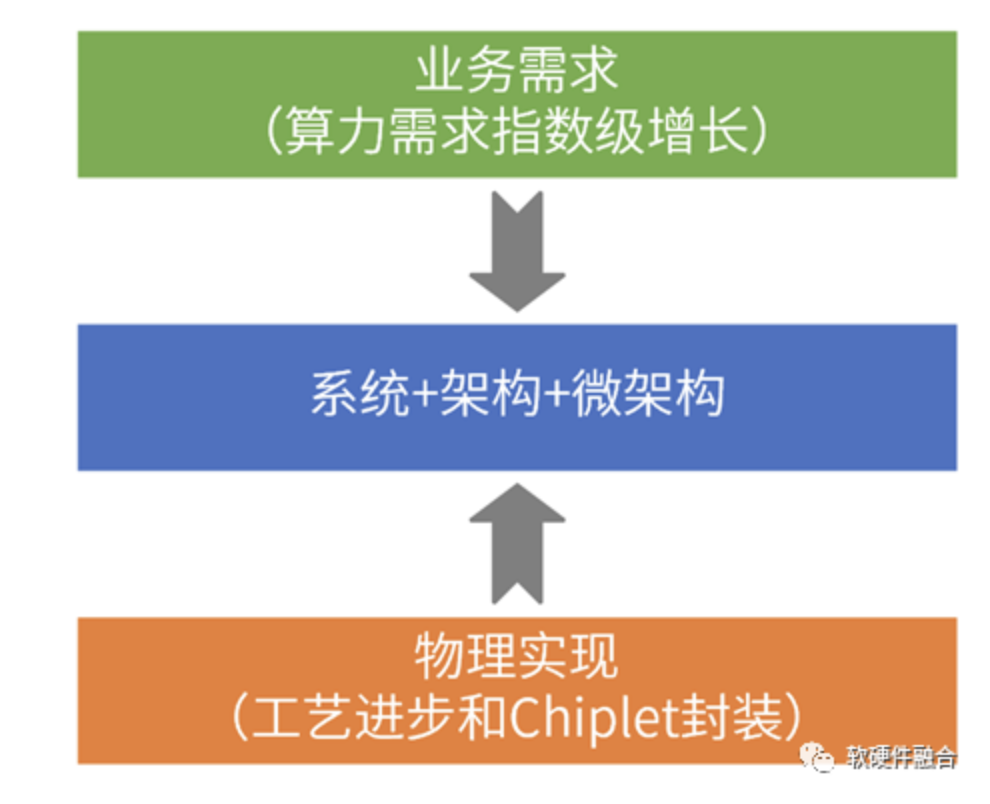

3.3 需求牵引,工艺支撑,系统架构必然需要创新

一方面,是业务需求的算力指数级增长,例如,目前AI算力需要每两个月增加1倍;另一方面,工艺和封装进步,使得单芯片设计规模从百亿级晶体管,逐渐增加到千亿级甚至万亿级,系统设计规模扩大接近100倍。

处于中间层次的系统架构设计,目前却没有重大的变化:不管是传统的CPU、GPU、FPGA还是相对较新一些的AI芯片、存算一体芯片以及DPU芯片等等,在本质上都没有改变现有以CPU为中心的计算架构。

量变必然引起质变,计算的架构必然走向一个新的阶段。

3.4 各类处理器都在拓展自己的能力边界

处理器“内卷”:每个处理器引擎都突破了通常意义上的各自边界,侵入到其他处理器引擎的领地:

- CPU集成协处理器。CPU不断扩展硬件加速指令集,形成协处理器集成进CPU。例如Intel Xeon支持AVX和AMX。

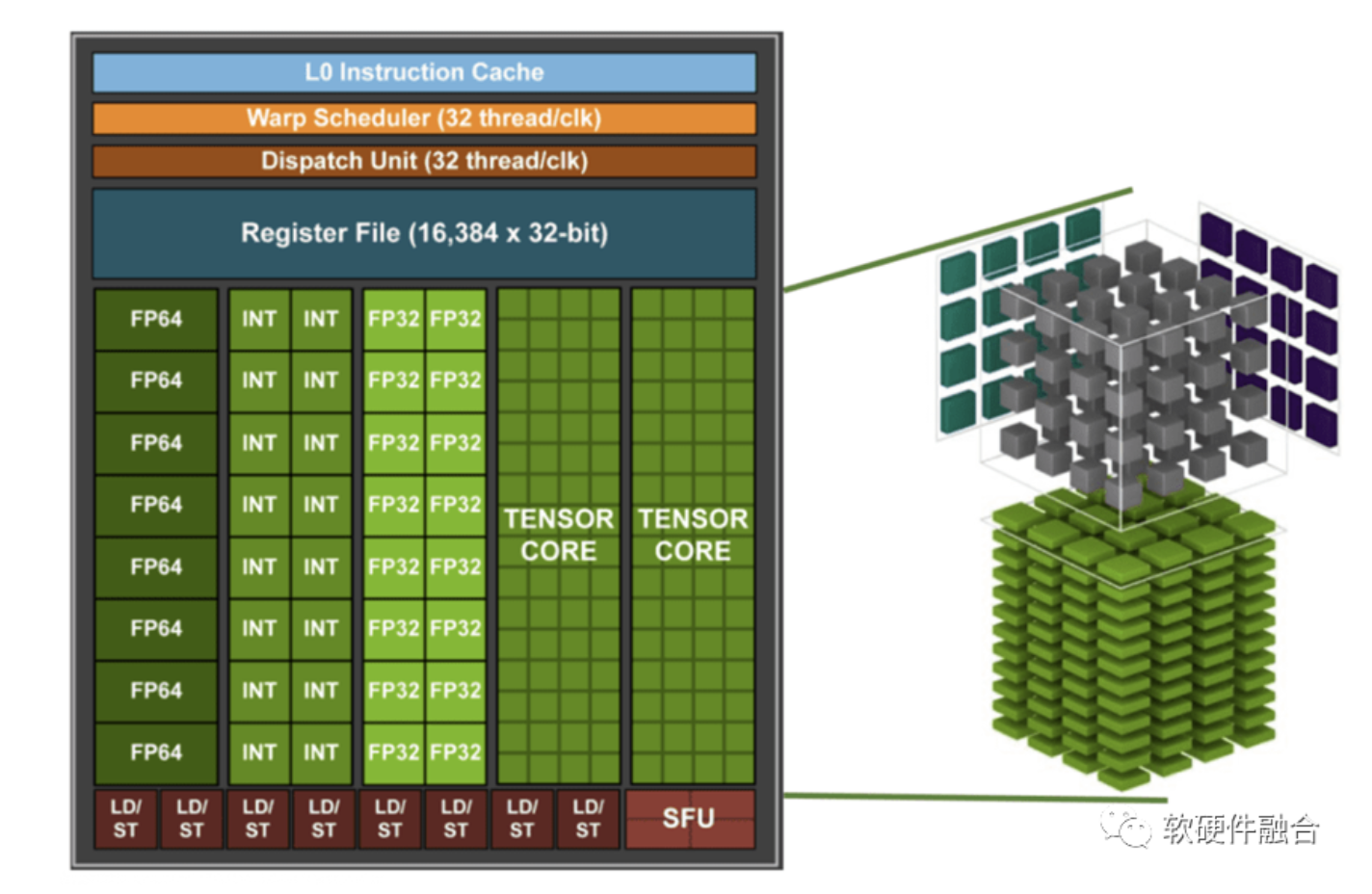

- GPU集成CUDA核,还集成DSA性质的Tensor核。

- FPGA集成CPU以及ASIC,形成SoC。例如AMD Xilinx Zynq。

- ASIC不断回调,变成部分可编程的DSA,可以当作是ASIC+DSA。

这样,就在单个处理器内部,已经形成了某种程度上的异构和融合。

3.5 从单异构走向多异构融合——超异构

要想高性能,势必降低灵活性,增加系统复杂度,使得系统难以驾驭。

并行计算难驾驭,异构并行难上加难。但我们不得不“迎难而上”,在难上再加难:为了更高的性能,计算架构需要进一步单异构走向多异构融合,形成超异构。

超异构难以驾驭,我们需要一些办法,来降低超异构系统的复杂度,使得超异构计算真正落地。

3.6 (新)计算架构的发展阶段

在前面我们讲了计算架构的发展阶段,也因此,未来计算架构会走向第五个阶段:超异构并行。

超异构并行计算,是新一代的(也可能是终极一代的)计算架构。

4 相关趋势案例

4.1 Intel在超异构的布局

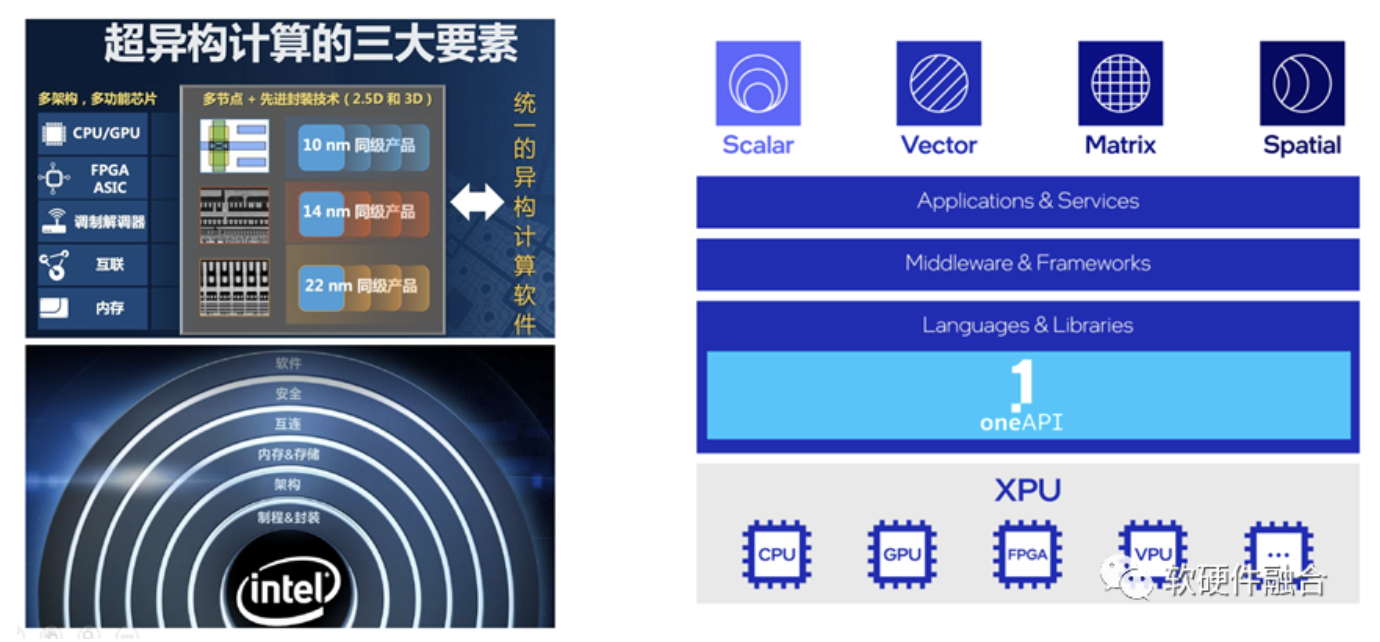

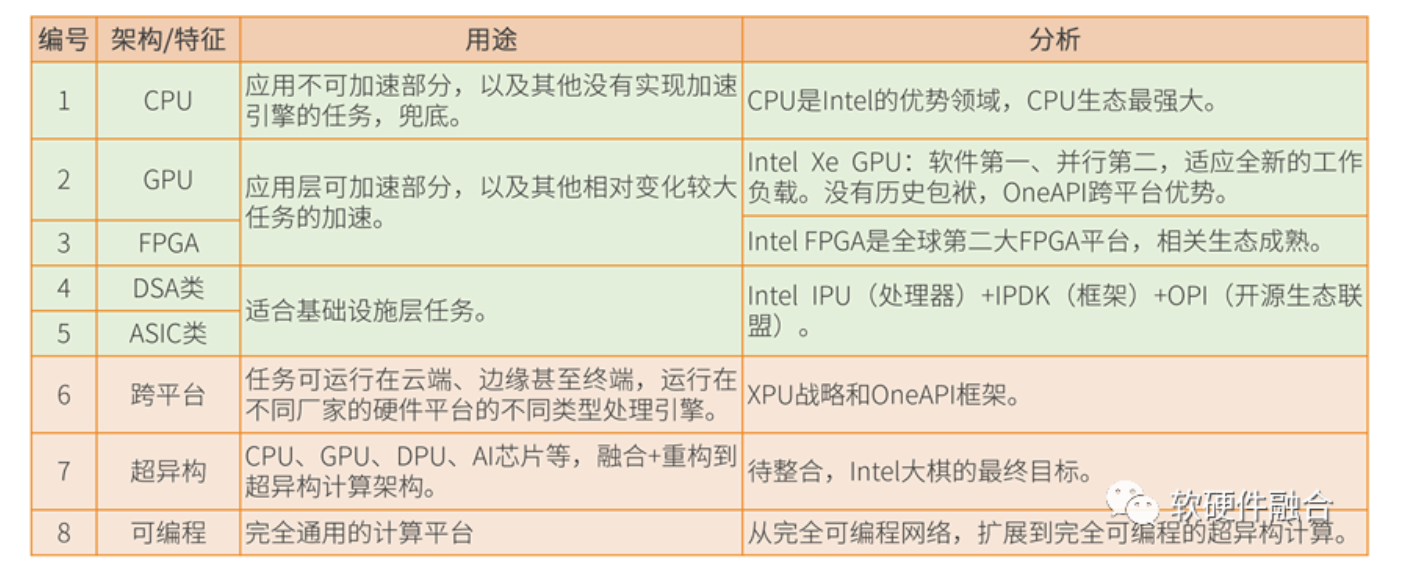

2019年,Intel提出超异构计算相关概念:XPU是架构组合,包括CPU、GPU、FPGA 和其他加速器。

并且推出了用于XPU编程的oneAPI。oneAPI是开源的跨平台编程框架,底层是不同的XPU处理器,通过OneAPI提供一致性编程接口,使得应用跨平台复用。

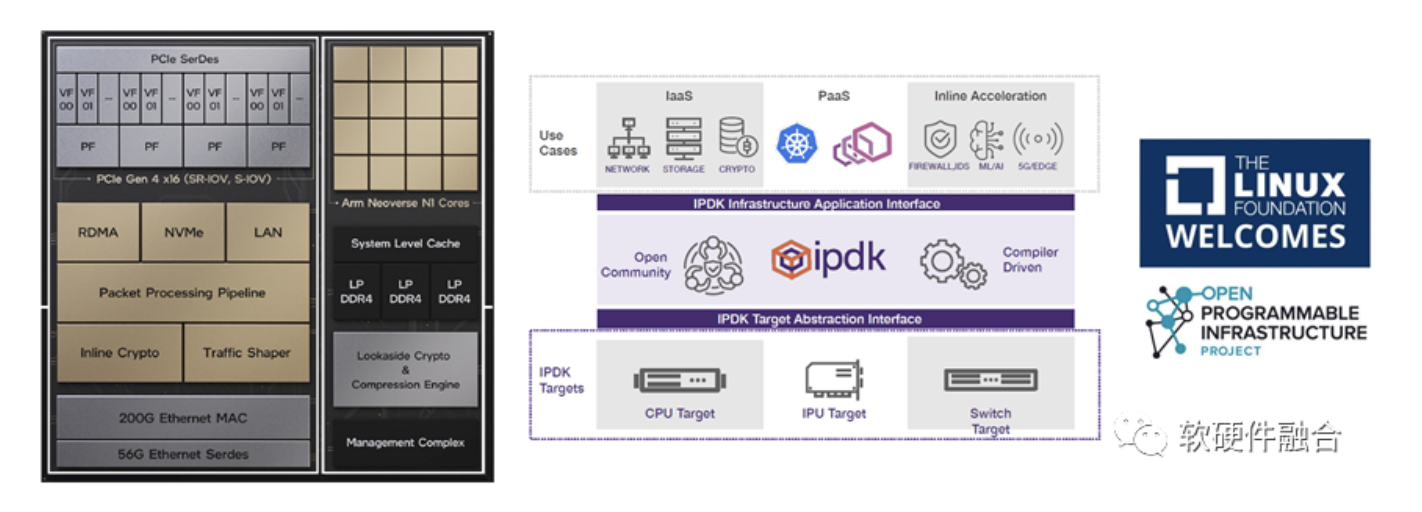

Intel IPU和NVIDIA DPU类似,可以看作是基础设施层DSA加速的集成平台。

IPDK是开源的基础设施编程框架,可运行在CPU、IPU、DPU或交换机。

2022年6月21日,Linux基金会宣布了开放可编程基础设施(OPI)项目。OPI的目标:为基于 DPU/IPU 类技术的下一代架构和框架培育一个社区驱动的基于标准的开放生态系统。

Intel在超异构计算的布局分析如下表所示。

不谋全局者,不足谋一域;不谋万世者,不足谋一时。

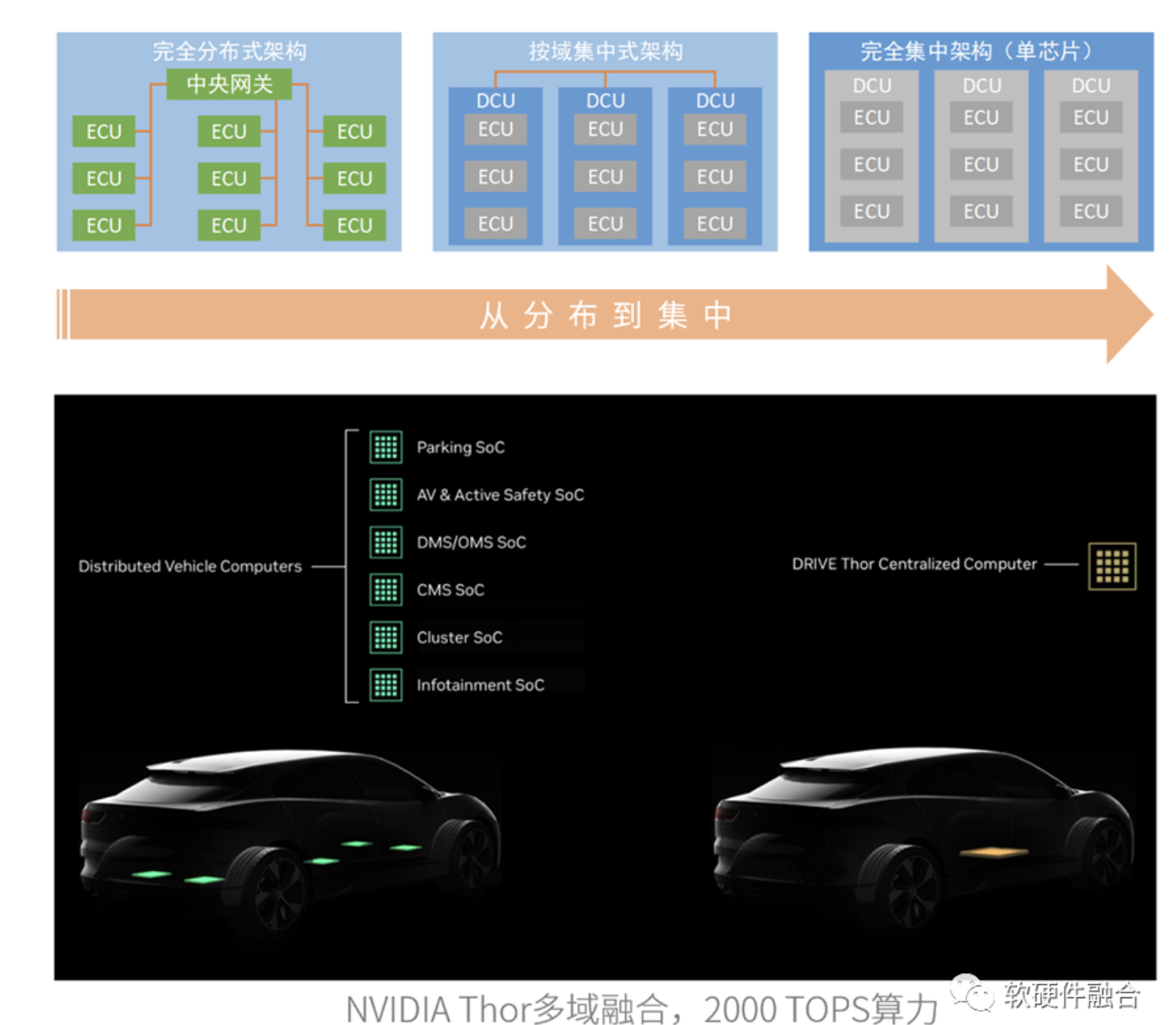

4.2 NVIDIA在超异构的布局

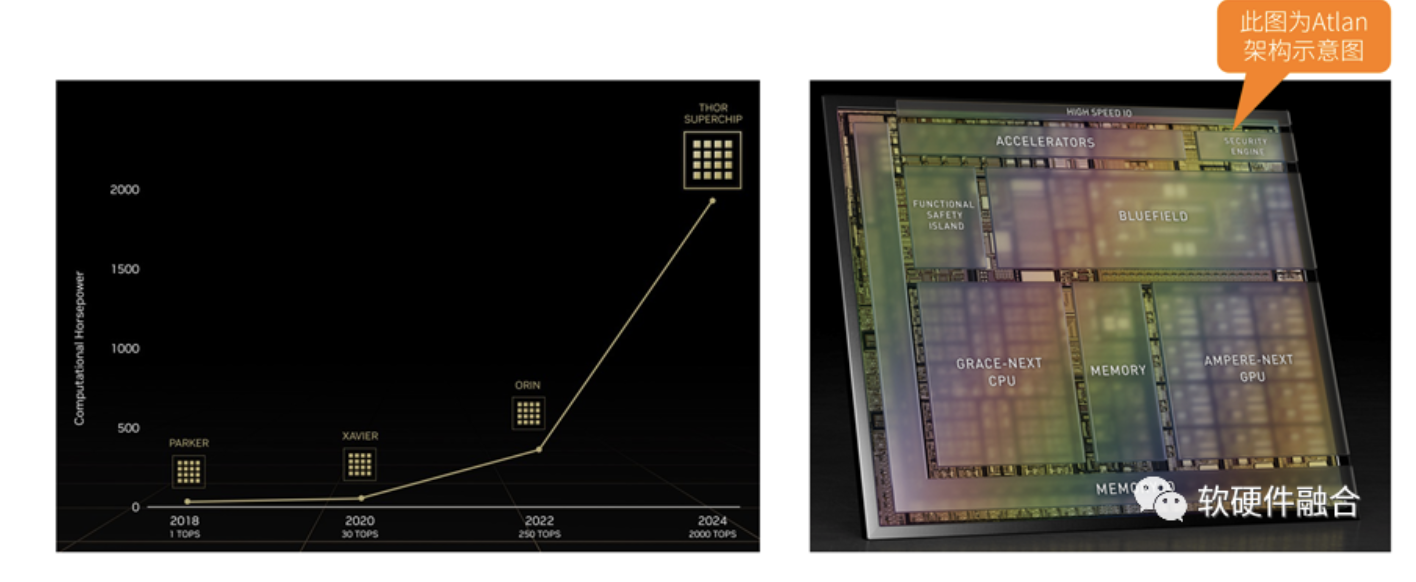

NVIDIA自动驾驶Thor芯片,由数据中心架构的CPU+GPU+DPU三部分组成,算力高达2000 TFLOPS的超异构计算芯片。

上图采用Atlan架构图,Atlan和Thor架构相同,性能上有差异。

Thor是符合超异构计算理念的全球第一款产品!

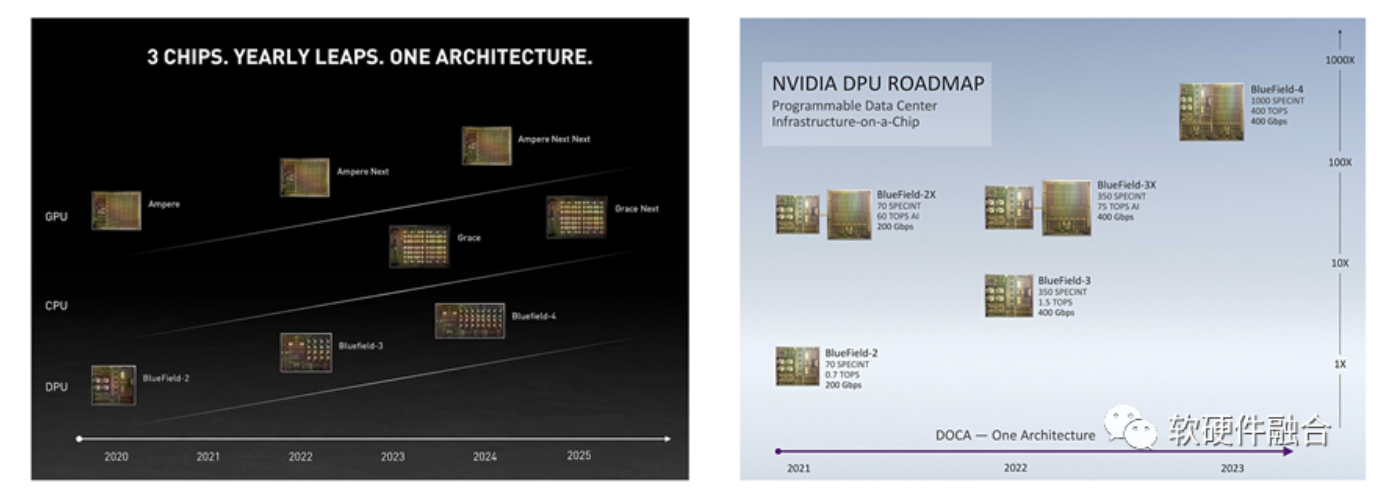

在数据中心,由于服务器计算规模较大,目前还没有CPU+GPU+DPU的融合型产品,但趋势已经很明显:NVIDIA Grace Hopper超级芯片是CPU+GPU,NVIDIA计划从Bluefield DPU四代起,把DPU和GPU两者集成成单芯片。

未来,Chiplet技术逐渐成熟,以及工艺的持续进步,CPU+GPU+DPU的超异构融合单芯片必然会出现。

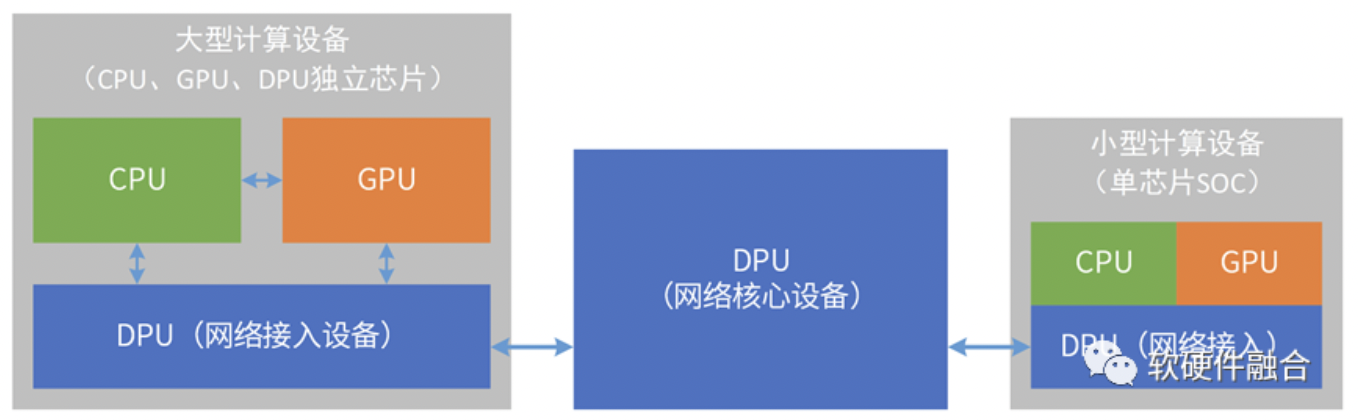

计算和网络不断融合:计算的很多挑战,需要网络的协同;网络设备也是计算机,加入计算集群,成为计算的一部分。

数据在网络中流动,计算节点依靠数据流动来驱动计算,所有系统的本质是数据处理,那么所有的设备就都是DPU。

以DPU为基础,不断地融合CPU和GPU的功能,DPU会逐渐演化成数据中心统一的超异构处理器。

5 超异构处理器HPU

5.1 微观性能和宏观算力

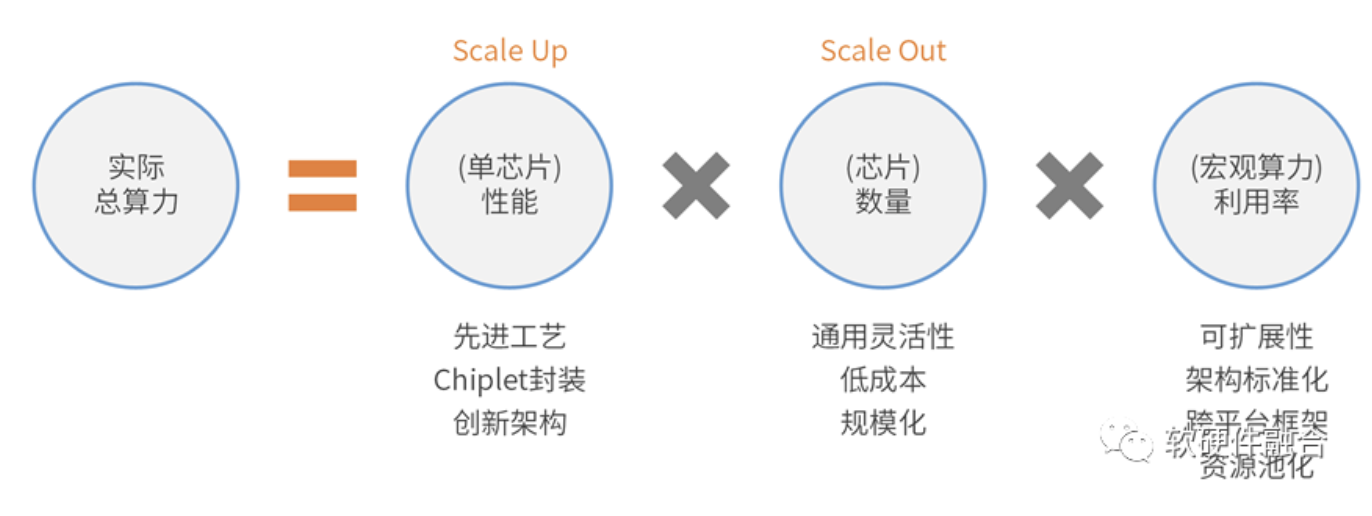

回归底层逻辑,我们该如何提升实际总算力?详细分析一下。

- 首先,Scale Up的方式,即快速提升单芯片的功能。比如通过先进工艺和先进封装,可以实现更大规模的设计。比如通过创新架构,从单位晶体管数量中挖掘更多性能的潜力。

- 其次,是Scale Out,即通过扩规模的方式提升性能。比如,我们国家战略“东数西算”就是要通过建设非常多的数据中心和放置更多数量的服务器,以此来提升宏观算力。但规模扩张的挑战还是在芯片层次,即芯片如何更好地支持规模化扩张。芯片如何能够覆盖更多用户的更多场景,以及在一个比较长的生命周期里能够胜任“工作”,这就需要芯片有足够的通用性、灵活性、适应性、易用性等等的能力。此外,还需要考虑单芯片成本降低的问题,降低单芯片成本,才能够更好地支持芯片的规模化扩张。

- 最后,是算力资源利用率。通过可扩展性,很好地跨芯片设备把资源集中起来;此外还需要尽可能标准化的架构,使得资源能够汇集;再通过跨平台能力的支持,实现宏观所有资源的统一的资源池。给软件提供最灵活的资源使用和管理方式,才能最大限度地实现计算资源的高利用率。

5.2 计算机体系结构演进:从合到分,再从分到合

随着CPU和GPU逐渐走向性能瓶颈,图灵奖获得者John H.和David P. 在2017年提出“计算机体系结构的黄金年代”,给出的解决方案是特定领域架构DSA。

但DSA架构分散的趋势会导致平台和生态的碎片化,这不利于芯片的大规模部署和成本摊销。

因此,我们认为,未来正确的趋势应该是从分离再回到融合。

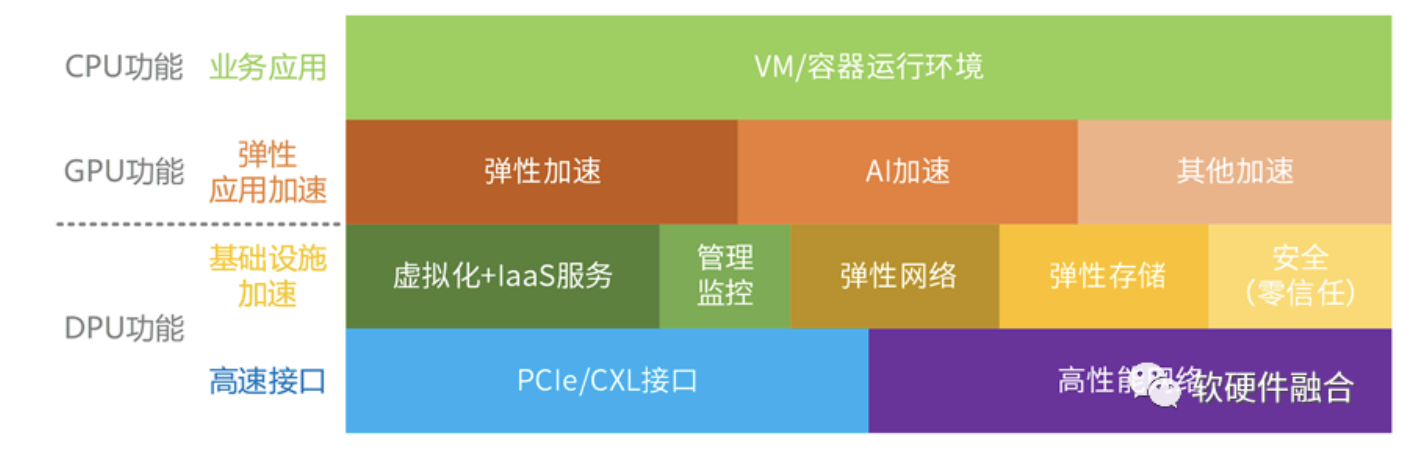

5.3 超异构融合芯片的典型功能

从系统视角出发,我们可以把系统中的众多工作任务划分为三类:

- 相对比较稳定的任务可以划归到基础设施层;

- 相对最不确定的任务放在应用层。应用层是用户自己的运行任务。在硬件平台设计或采购的时候,并不知道最终用户会用来运行什么,并且应用还会持续升级演进。因此,应用是最不确定的。

- 弹性应用加速层,灵活性处于两者之间。

我们把支持这些功能的单芯片称为SGP-HPU(Extremely Scalable General Purpose Hyper-heterogeneous Processing Unit,极致可扩展的通用超异构处理器)。

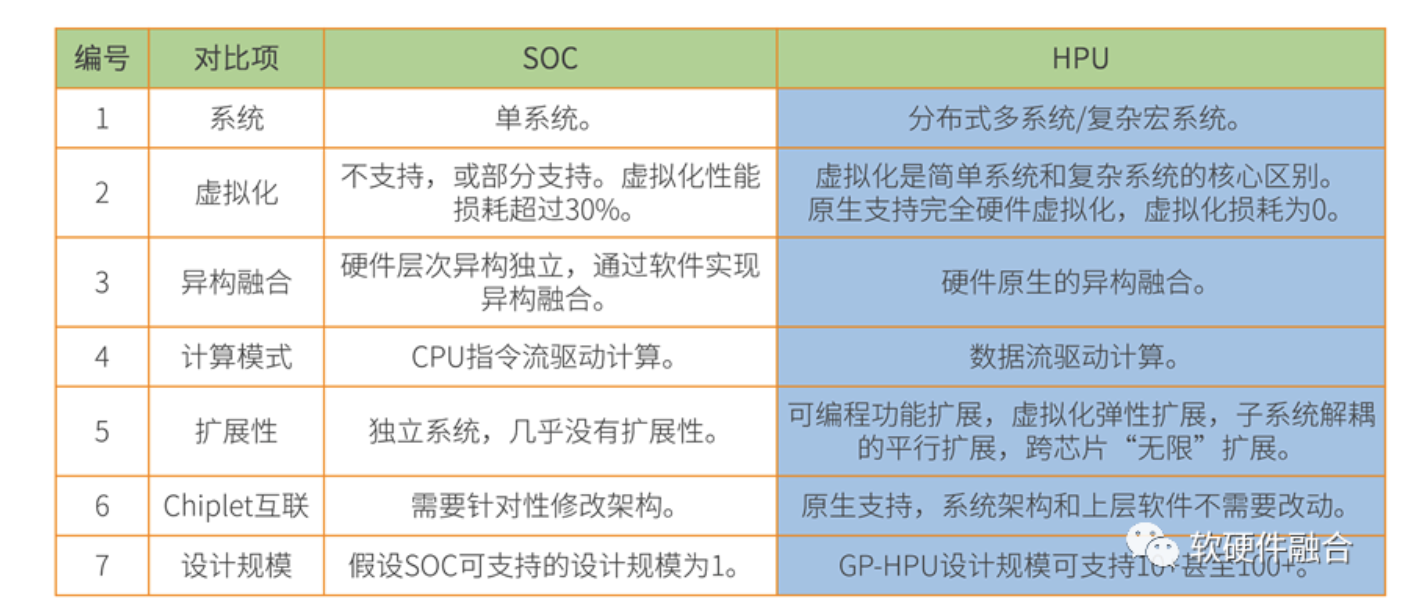

5.4 HPU与传统SOC的区别

HPU本质上也是SOC,但和传统的single-SOC相比,HPU是Multi-SOC融合而成的Macro-SOC。下表是HPU和传统SOC的典型区别。

5.5 HPU应用场景广泛

5.5.1 用在边缘等轻量服务器场景

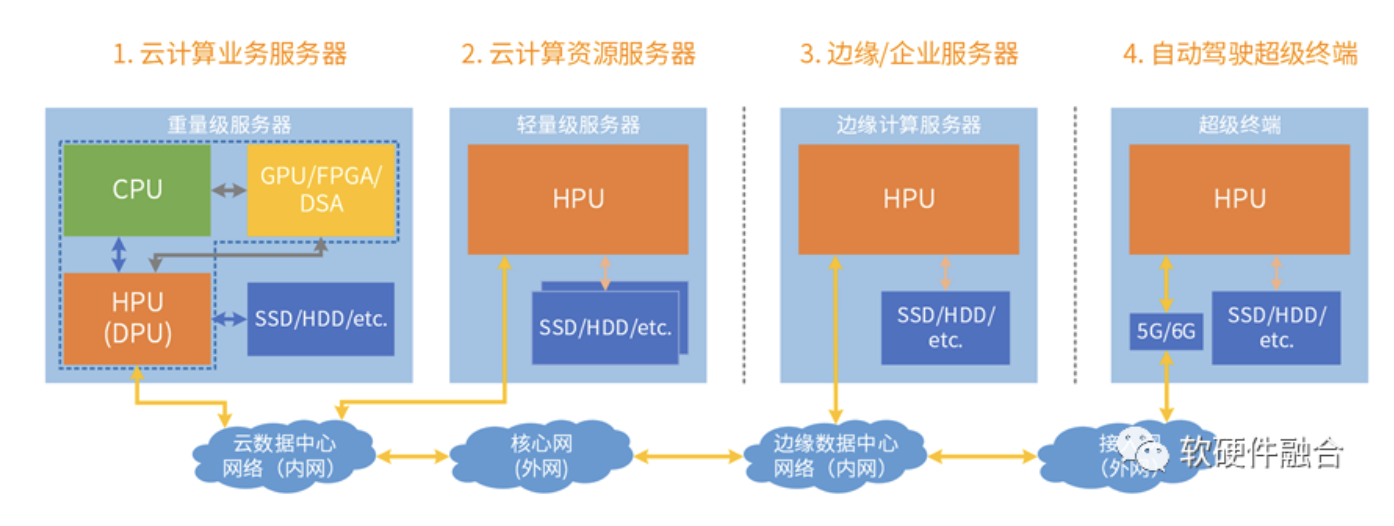

HPU单芯片,可广泛使用在边缘计算服务器、存储服务器、企业云服务器等轻量级服务器场景,轻量级服务器占整体服务器数量的80%以上。

5.5.2 HPU用在自动驾驶&智能网联汽车场景

汽车的EE架构,目前在经历非常大的变革。从传统300多甚至上千颗小ECU芯片组成的分布式架构,逐渐的过渡到了按相近功能域融合成SOC的域控制器DCU的半集中架构,再进一步发展到完全集中的超级计算大芯片架构。

这个演进思路和HPU的发展趋势是完全吻合的,集中式的超大算力自动驾驶汽车芯片的计算平台本质上就是HPU。

自动驾驶汽车更像手机,还是更像服务器?

从我们目前的分析看,自动驾驶汽车更像服务器一些:数据中心的技术在逐步“下沉”车端,如虚拟化、SOA、SDx等技术;并且需要在单个硬件支持多个软件系统,并且做到系统间应用、数据、性能、故障、安全等方面的隔离。

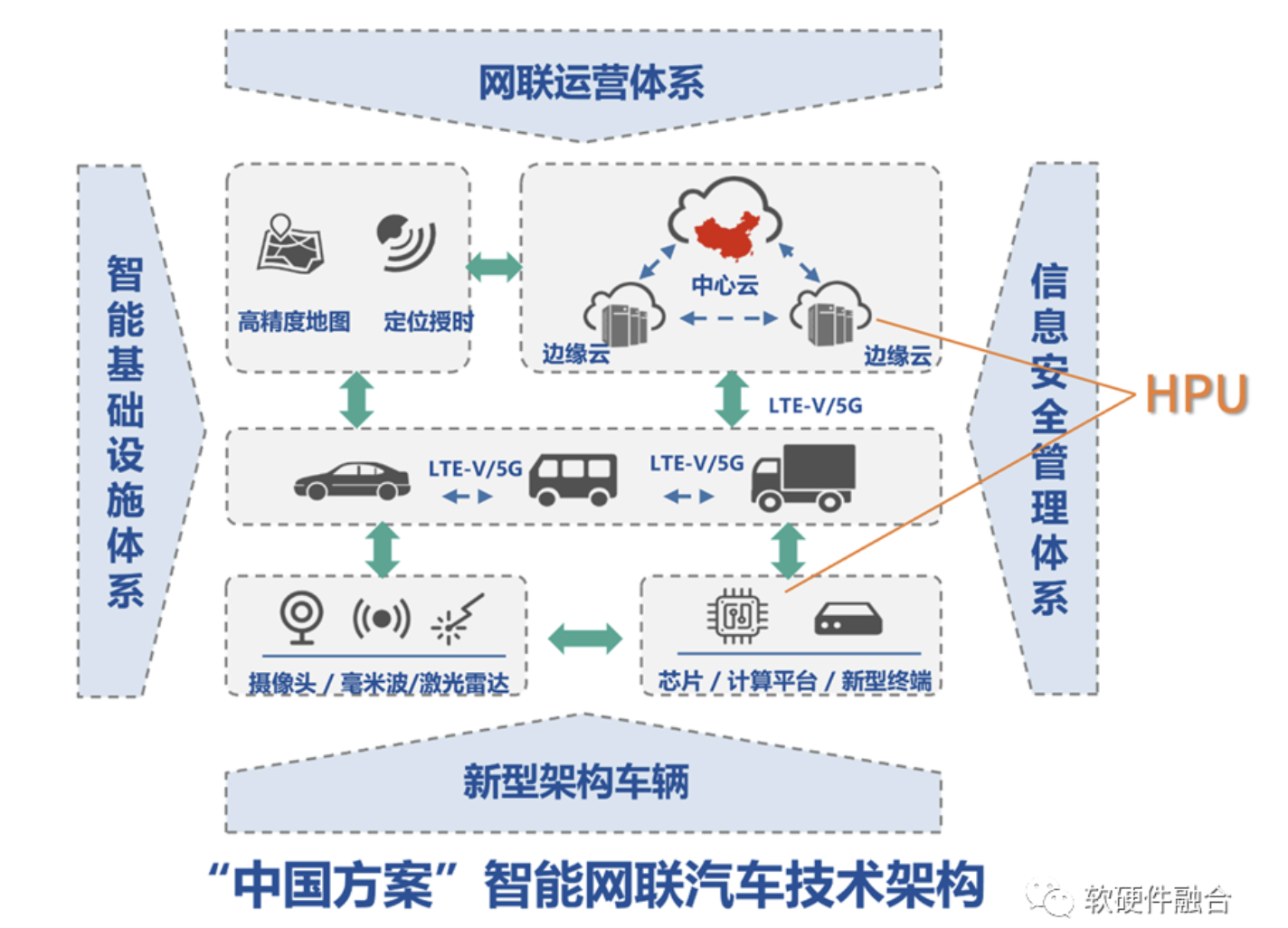

李克强院士提出智能网联汽车中国方案:通过边端深度协同,可以在单芯片能力较弱情况下,实现系统级能力更优。

在目前无法拿到最先进工艺的情况下,智能网联汽车系统解决方案是我们迈向智能+自动驾驶汽车时代的必由之路。

5.5.3 超异构更加广泛的应用领域

云网边端融合,计算架构趋于统一。超异构可广泛地应用在云计算、边缘计算、超级终端,甚至网络端。

(正文完)

来源:软硬件融合

相关文章推荐

更多软硬件技术干货请关注软硬件融合专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。