【爱集微点评】华邦电的封装专利,通过将管芯设置在凹槽中,且使用三维打印导线将引线框架与接垫进行电性连接,因此不存在引线接合的弧高及距离的限制,进而可缩小管芯与引线框架的间距并降低封装结构的厚度,使得封装尺寸微小化。

集微网消息,近日,闪存制造商华邦电近日宣布加入UCIeTM(Universal Chiplet Interconnect ExpressTM)产业联盟,结合其先进的封装经验,推动接口标准普及。

传统半导体封装的内部接合方式可分为引线接合、带式自动键合与倒装芯片结合。其中引线接合由于工艺成熟、成本低、布线弹性高,是目前应用最广的接合技术。然而,引线接合的缺点是有输入/输出(Input/Output,简称I/O)引脚数的限制。此外,在先进工艺封装希望封装尺寸微小化的情况下,因为使用引线接合有弧高及距离的限制,使得封装尺寸无法往微小化来前进。

为此,华邦电于2020年6月23日申请了一项名为“封装结构及其制造方法”的发明专利(申请号:202010579756.1),申请人为华邦电子股份有限公司。

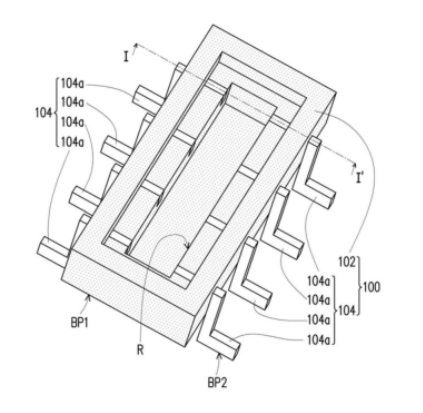

图1A 封装结构的制造流程立体图

图1A为本专利提出的一种封装结构的制造流程立体图。引线框架结构100包括载板102与引线框架104。载板102可用以固定与承载引线框架104,其具有凹槽R,可用于容置管芯。引线框架104设置在载板102上,载板102可覆盖部分引线框架104,使得载板102高于引线框架104。

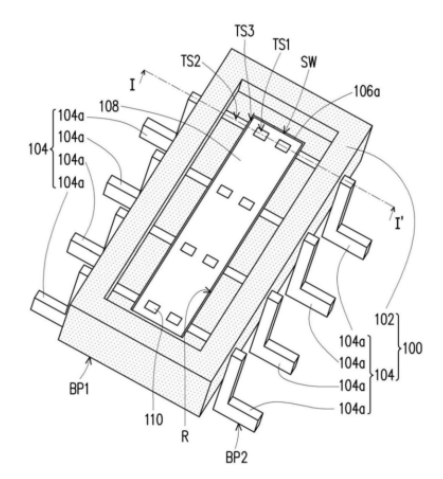

图1B 封装结构的制造流程立体图

之后将黏合剂106填入凹槽R中,黏合剂106的材料包括丙烯酸黏合剂、聚氨酯黏合剂、硅胶黏合剂或橡胶黏合剂等。参照图1B,将管芯108放置在凹槽R中,使得黏合剂106由管芯108的底面BS与载板102之间溢出至管芯108的侧壁SW与载板102之间,而形成黏合剂层106a。管芯108为集成电路元件,至少包括一个接垫110。

管芯108顶面TS1和黏合剂层106a顶面TS3的高度分别等于或高于引线框架104的顶面TS2的高度、管芯108的顶面TS1与引线框架104的顶面TS,有利于后续使用三维打印工艺形成导线。在黏合剂层106a的顶面TS3高于管芯108的顶面TS1与引线框架104的顶面TS2的情况下,黏合剂层106a不会完全覆盖接垫110与引线框架104,以防止黏合剂层106a在后续三维打印工艺中阻碍引线框架104与接垫110之间的电性连接。

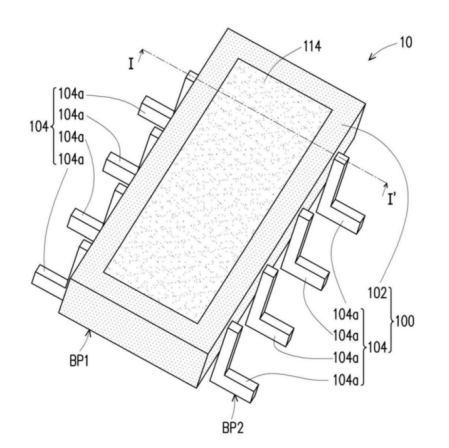

图1C 封装结构的制造流程立体图

参照图1C,使用三维打印工艺在引线框架104、黏合剂层106a与接垫110上形成至少一条三维打印导线112。三维打印导线112电性连接于引线框架104与接垫110之间,可利用三维打印机的喷头200进行列印。之后可形成覆盖管芯108、三维打印导线112与部分引线框架结构100的包封体114。

简而言之,华邦电的封装专利,通过将管芯设置在凹槽中,且使用三维打印导线将引线框架与接垫进行电性连接,因此不存在引线接合的弧高及距离的限制,进而可缩小管芯与引线框架的间距并降低封装结构的厚度,使得封装尺寸微小化。

华邦电创立于1987年9月,现在是中国台湾最大的IC公司之一,华邦电以三大事业群为核心,不断追求产品与技术的创新,致力于先进半导体设计及生产技术。此次加入UCIe产业联盟,可谓强强联合,希望后续华邦电子可以凭借此机会继续发力,稳扎稳打。