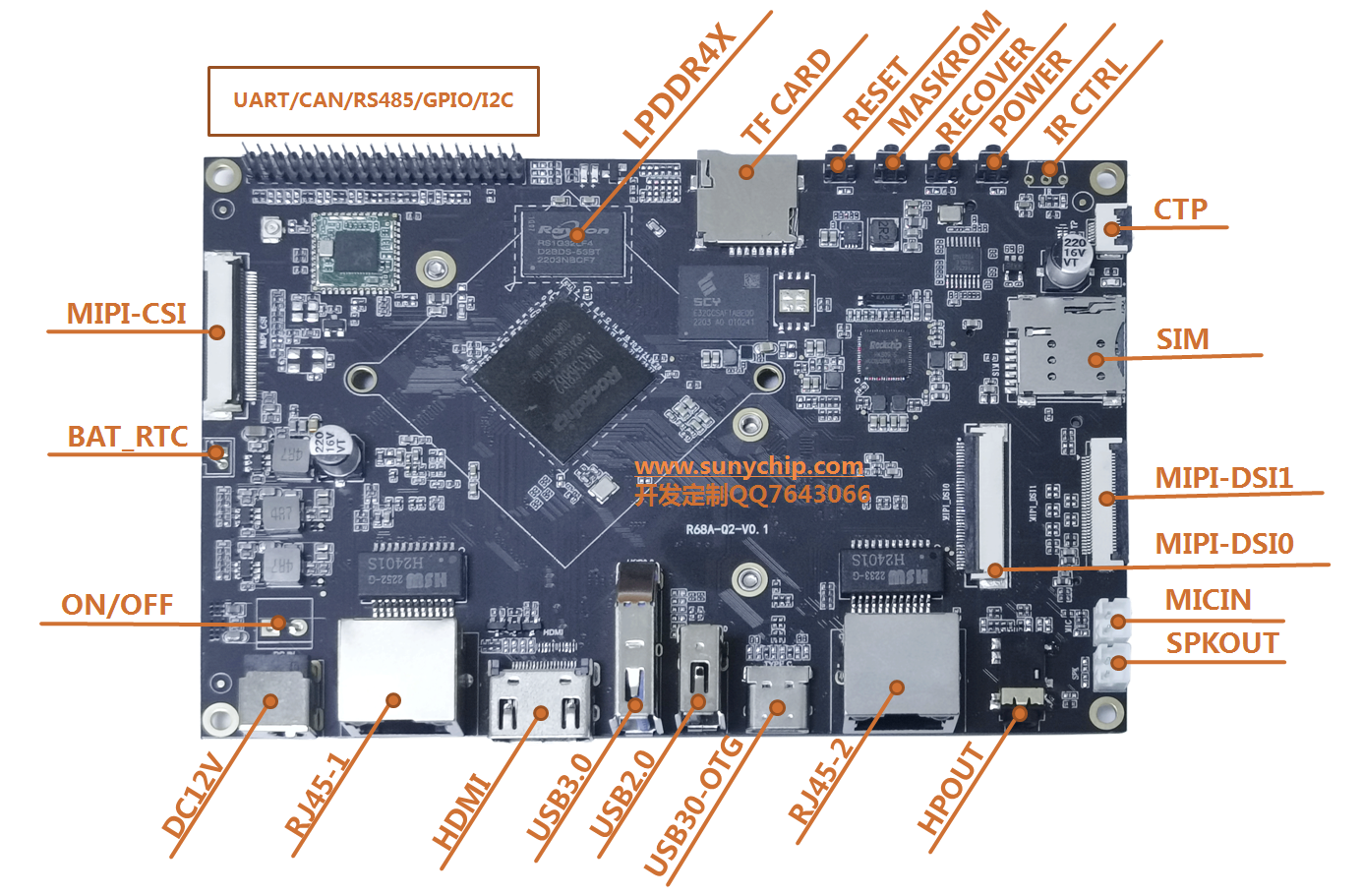

rk3568硬件开发笔记(第四篇 ) 固态硬盘电路设计

开发板上使用标准 PCIe3.0 连接座,可安装外部 PCIe 板卡进行通信。

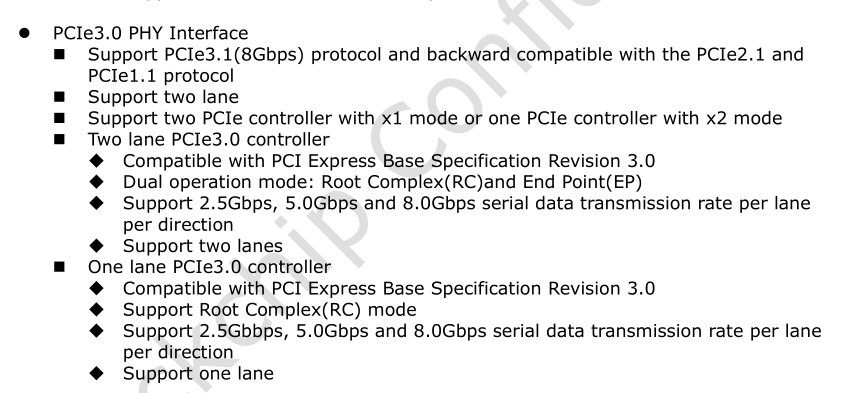

工作模式:Root Complex(RC)。

链路支持 4 lane 数据接口。

100MHz 时钟是由外挂时钟芯片提供的。

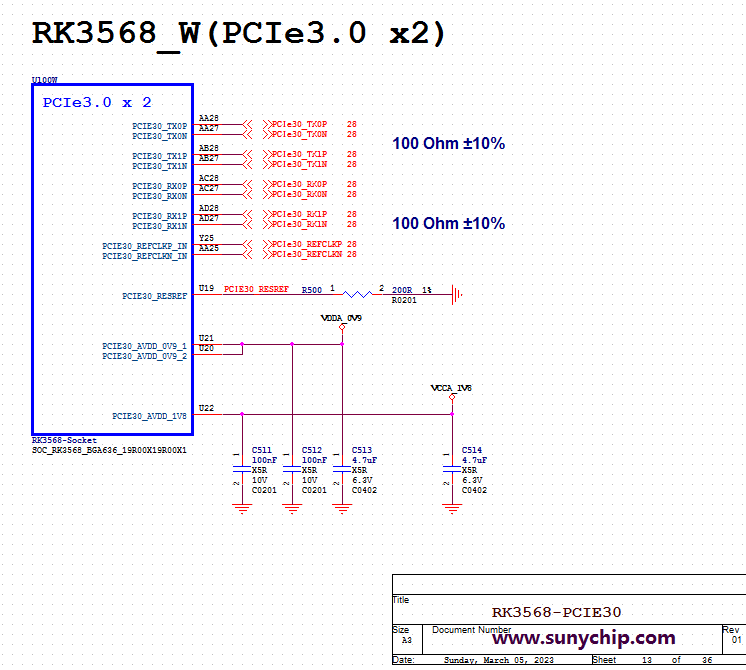

第一节:pcie3.0接口CPU端

主要网络有2组TX、2组RX、1组clk,以及1组供电,分别是0.9和1.8V;

差分线需要做100 Ohm阻抗控制,其中R500是参考电阻可调节驱动能力;

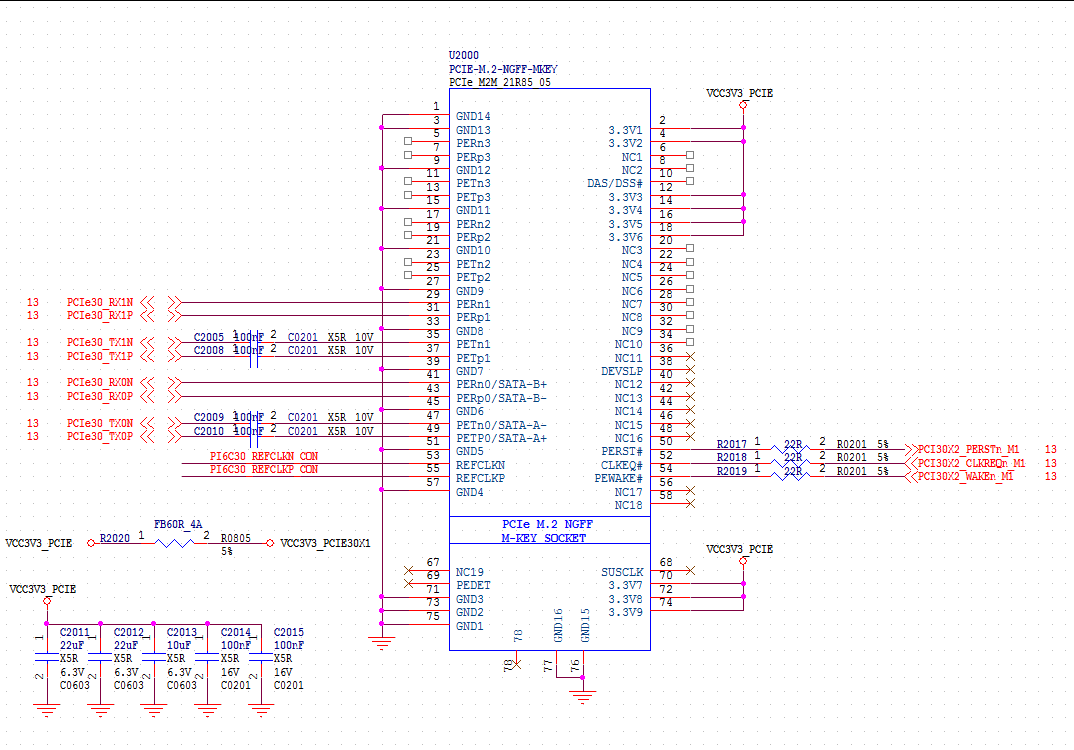

第二节:pcie3.0接口电路

说明:

1、接口采用M.2连接器,接口类型M-KEY,75PIN;

2、2组TX信号加耦合电容,一般为100pf;

3、其他信号有复位、唤醒、和参考时钟;

4、PCIE3.0默认接SSD固态硬盘,电流一般在3A以内,电压3.3V;

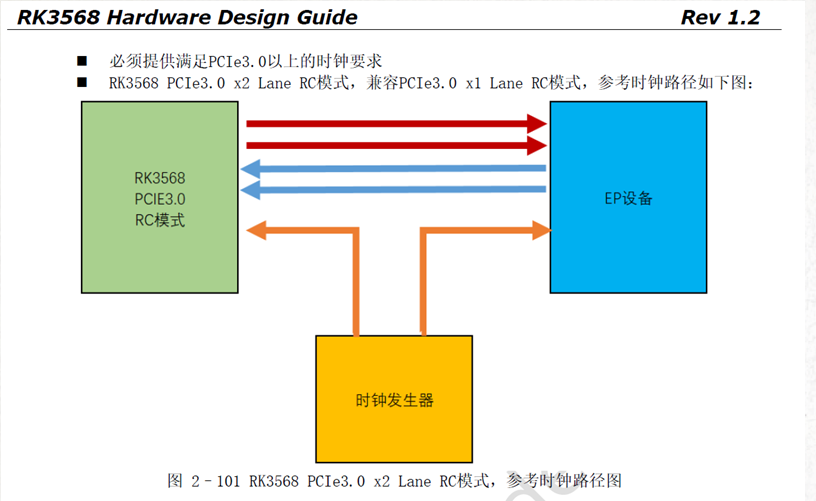

第三节:rk3568 pcie3.0对于clk的处理

RK开发文档明确指出,PCIE30和EP设备连接,CLK信号需要外接

因此增加PI6C557-03BLE时钟发生器,

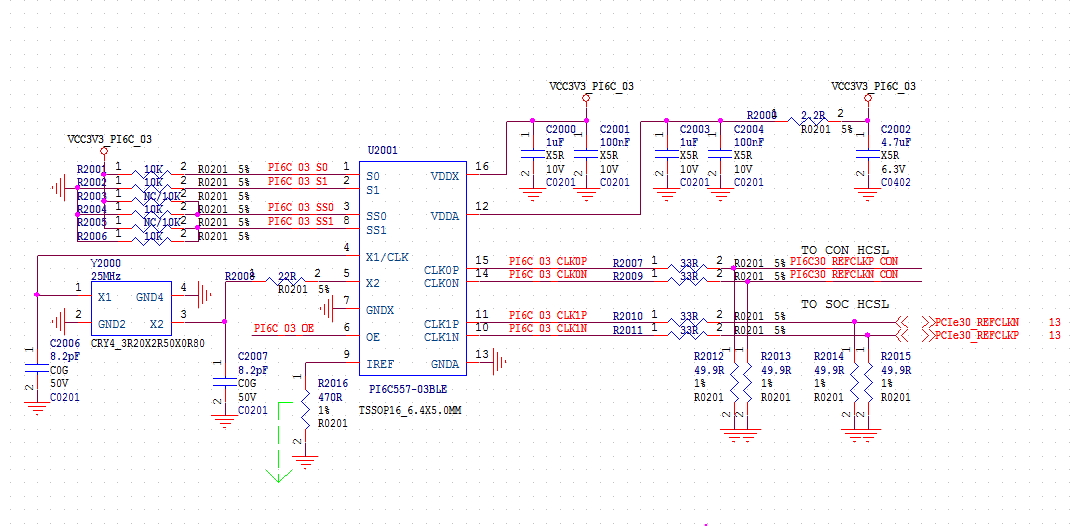

时钟发生器外围电路说明:

1、时钟发生器1 2 3 8脚通过上拉/下拉电阻进行配置,

2、需要外挂25MHZ晶振,匹配电容选8.2pf;

3、如果主板走 50ohm阻抗

那么R2016 = 475ohm 提供的 IREF=f 2.32 mA . 输出电流 ( IOH ) i= 6 * IREF .6x2.32X50=696mV

4、时钟信号输入输出上面加33R匹配电阻,对接加49.9R;

附图

以上电路设计基于下图新创云R680A-Q2开发板