本文最初由笔者本人以 Zynq SDK 驱动探求(一):ARM 核与外设的故事开始了 为题发布于知乎,署名ljgibbs

- -

Processor is ready. Configure programable logic.- -

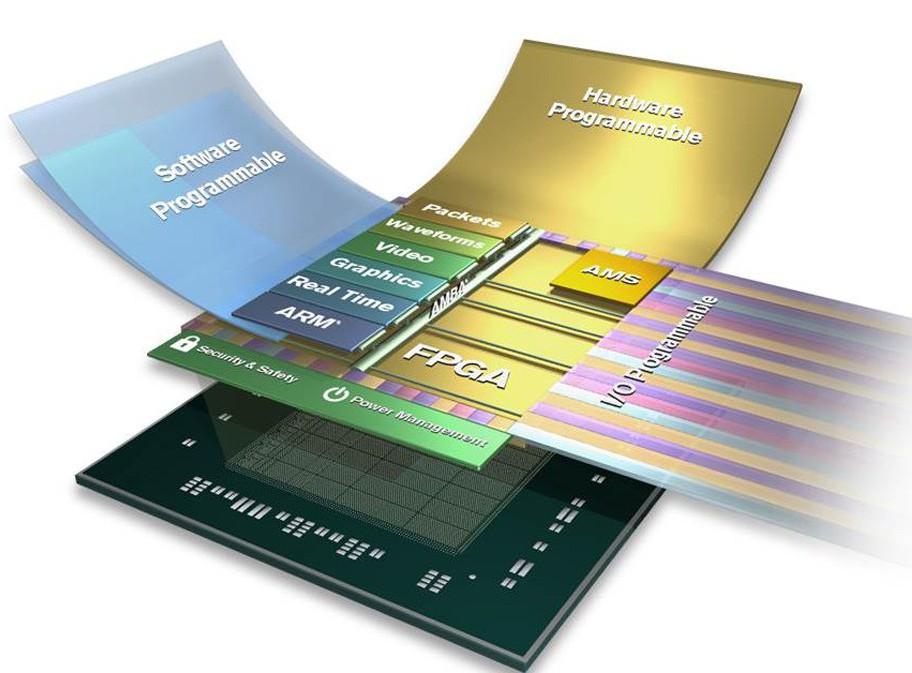

在新专栏 Rapid TCP/IP on Zynq 中,将围绕 Xilinx Zynq 系列芯片,从 SDK 驱动,PS-PL 协同加速,嵌入式协议栈 LWIP 分析以及 TCP/IP 硬件加速等方面,一起探求可灵活配置,软件定义,硬件加速的 TCP/IP 协议栈的实现。在专栏的首篇文章中,我们将从 Processor 处理器核和微处理器的概念辨析切入,为大家介绍 Zynq 外设相关的概念。

Zynq 出身自 FPGA 大厂 Xilinx,是赛灵思的一个产品系列。

区别于传统的 FPGA 系列产品,Zynq 芯片中除了 FPGA 逻辑资源以外,还包括了两个 ARM A9 硬核。

在嵌入式领域中,往往很容易将处理器核(Processor)和 微处理器 (单片机)搞混。

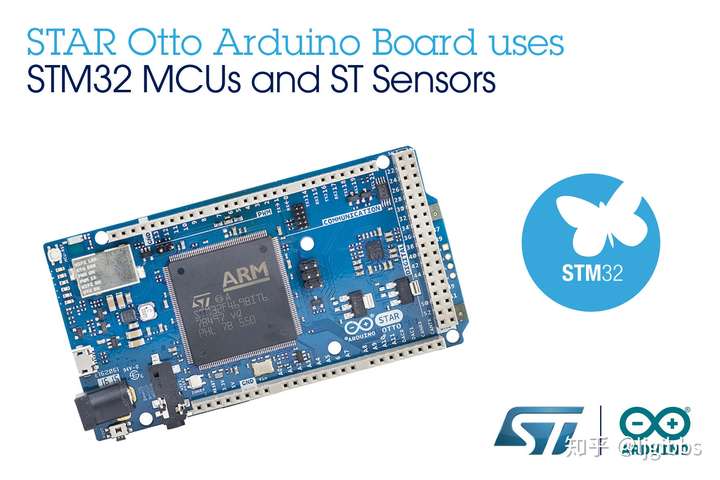

这里以大家熟悉的 STM32 为例,理清这个概念。

(STM32 大家应该熟悉的吧)

蝴蝶在线下有很多活动,大家可以关注下

处理器与处理器核

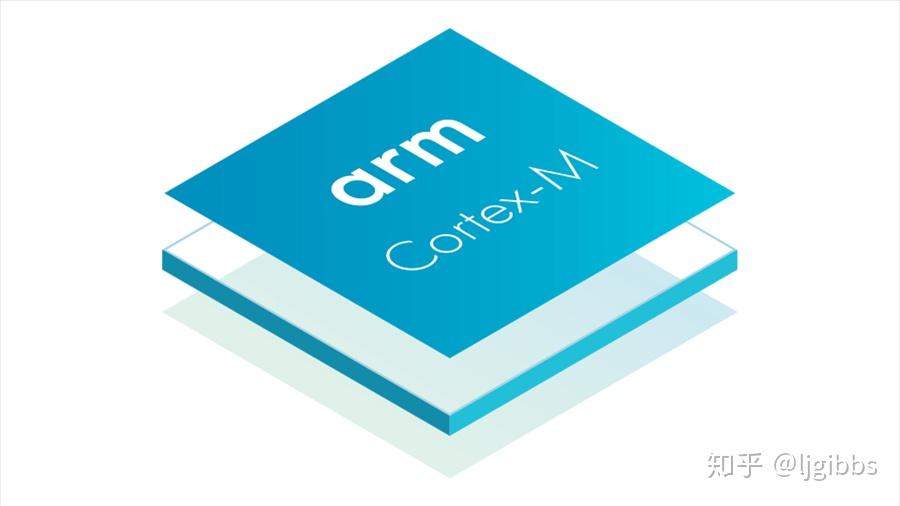

STM32 系列处理器中使用 ARM Cortex M0/3/4/7 核作为处理器核。

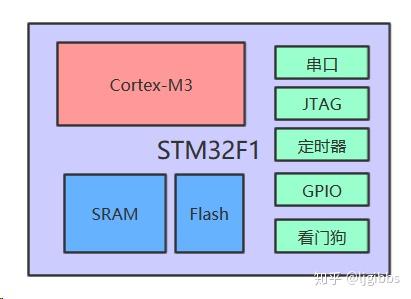

在 ARM 提供的处理器核 IP(Processor IP) 基础上,ST 为其添加了一系列外设,包括串口,定时器,DMA等,以及 SRAM 和片上 FLASH 这样的 Memory ,一起流片做成了一颗 STM32 ,这样一个微处理器,其实也是一个 SoC (System on Chip)片上系统。

SoC(微处理器)= Processor + 外设 + Memory 注1那么我们断言:STM32 就是一个 SoC ,而其处理器核为 ARM M 系列。目前主流的单片机实际上都是 SoC,但这些 SoC 的处理器核并不都是由 ARM 设计提供的。

接着断言:Zynq 与其说是 FPGA ,不如说 Zynq 就是 SoC。而其处理器核为 ARM A9。

那么 Zynq 的 FPGA 逻辑部分怎么说,实际上 PL (Programable Logic 指 FPGA 中的可编程逻辑资源)需要听 ARM 核的指挥,某种程度上 PL 是 ARM 核的一项外设,或者说协处理器,在之后我们会详细讨论 PL 的从属地位。

说起来我们的 X86 CPU ,Intel 或者 AMD 其实都不是 SoC,你知道为什么?

处理器外设

接着我们说回外设( peripheral device ),外设在处理器系统中指的是 GPIO,UART,DMA 这些处理器的组件,他们听从处理器核的指挥,干他们自己的活儿,比如打印串口信息。对于 STM32 这样的单片机来说,外设只有一种,那就是固化的硬件电路,这和处理器核是一样的,都是不能修改的 ASIC (专用硬件电路)。

但 Zynq 的情况就有所不同,拥有两类不同的外设。

一类是和 STM32 单片机相同的硬件电路外设,这部分硬件电路和处理器核一起组成了 Zynq 的处理器系统(Processor System)。这部分和单片机完全相同,所以我们与其说 Zynq 嵌入了双核 A9 硬核,不如说嵌入了一个硬件处理器系统(近似于一个完整的单片机)。

PS = Processor + 片上外设另一类外设由 FPGA 部分的可编程逻辑(PL)构成,它们最大的特点在于可编程,无论是外设的数量还是类型。某个部分的逻辑资源可以在先前作为串口使用,过会儿就可以作为 SPI 接口,这种变化甚至能够动态进行。另外,我们知道 STM32 的硬件串口在 F103C8T6 上可能就是 3 个,但在 Zynq 上,我们可以使用硬件资源部署 30 个硬件串口,300 个也。。这个或许夸张了。PL 外设相比 PS 外设的缺点在于速度要慢一些,稳定性也可能稍差。

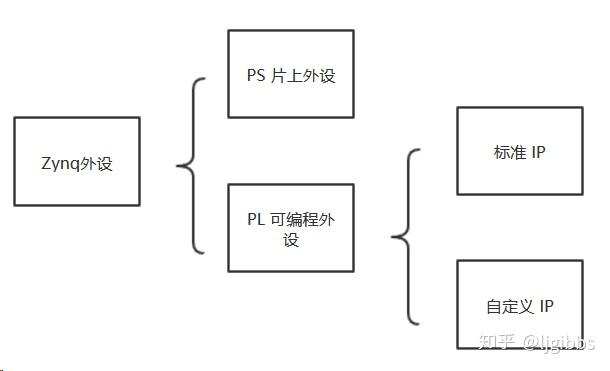

所以,Zynq 拥有两类外设:PS 或者 PL。其中 PL 外设又可以分为两类:标准 IP 和自定义 IP。Xilinx 和其他厂商提供了基础的标准 IP,包括 FIFO,RAM,AXI-Uart,AXI-Jtag 等等,这些电路模块都久经考验,在基础的功能上可以充分地信任他们。

另一类是由用户完全自定义的 IP,用来实现定制化的功能,比如我需要一个加法器,这个加法器不一般,每次进行加法计算时,能模拟一些粗心的一年级小朋友,以小朋友犯错的概率出现一些运算失误。

4 + 7 = 12这类 IP 可以从心所欲,但没有经过历史的考验,有时侯就会太年轻,出现一些问题。另外标准化的 IP 得到了厂商的很多支持,比如 Xilinx 为一些 IP 提供了 Linux 上的驱动。至于自定义 IP ,那这些支持就完全不存在了。

总线

SoC 还有一个很重要的组成部分是总线,或者片上网络。总线将处理器核和外设连接到一起。处理器核与外设的通信通过总线进行。如果把处理器核比作大秦帝国的都城,要将一条条敕令发往帝国各地,总线就好比是帝国的一条条驰道一样必不可少。处理器核的指令就通过总线传输到各个外设。

Zynq 中主要的总线是 AXI4 总线,这是一种由 ARM 提出的标准化 IP 间总线,你可以从以下系列文章的链接中略微了解 AXI4:

https://zhuanlan.zhihu.com/p/44766356

Zynq 中不只存在 AXI4 系列总线,在 PS 中 ARM 核和片上外设之间的连接通过 APB,AHB 总线进行,和 STM32 使用相同的总线。APB,AHB 总线和 AXI4 类似,实际上他们都属于 ARM AMBA 协议族。

在软件编程的过程中,总线操作由底层 IO 驱动负责,所以并不需要加以关注。但在编写硬件 IP 的过程中,需要对总线的接口加以了解。

注1:Memory 对于 SoC 不是必须的,或者说很多 SoC 的存储器不完全在片上。

结语

本文通过对处理器核与微处理器这对概念进行梳理,大致地介绍了 Zynq 中 ARM 核和外设之间的关系,可以说是故事的开始。

在下一篇的 SDK 驱动探求文章中,我们将以定时器为例,追溯一个外设从初始化到工作的过程,了解外设是如何和处理器一起工作的。

更多FPGA相关知识请关注我的FPGA 的逻辑专栏