【爱集微点评】云途半导体公开的高可靠性的锁相环模块及其输出时钟的切换方案,能够实现锁相环输出时钟的自动切换,降低了功耗,节约了成本。且能够避免因锁相环失锁以及锁相环输入参考时钟发生抖动所导致的系统故障、崩溃等问题,极大地提高了系统的稳定性和可靠性。

集微网消息,锁相环路是一种反馈控制电路,称为锁相环(PLL)。其利用外部输入的参考信号控制环路内部振荡信号的频率和相位。在处理电子信号过程中,因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常广泛应用于闭环跟踪电路。

现有技术中,锁相环通常包括分频器、鉴相器、压控振荡器等部分,锁相环的输出时钟连接系统时钟控制单元,通过系统时钟控制单元输出系统时钟。现有技术通过设置锁相环配置寄存器来配置锁相环中的多个分频器的分频系数,从而来修改锁相环的输出时钟频率,以满足不同的应用需求。

目前,现有技术在修改锁相环的输出时钟频率时,通常包括如下几个步骤:

1)先要将系统时钟切换至稳定的时钟源;

2)第二步:修改锁相环的配置信息(分频系数等);

3)第三步:等待锁相环锁定标识被置起;

4)第四步:当锁相环锁定标识置起后,再将系统时钟切回锁相环输出时钟。

现有技术在上述修改锁相环的时钟频率时,需要4个步骤才能完成,修改过程较为繁琐。且上述修改方式均需要软件参与,一旦软件执行出现错误或者异常,会导致系统时钟出现超频、降频甚至时钟丢失等严重后果,进而增加系统故障几率。此外,需要提供一个稳定可靠的时钟源作为系统时钟,因为增加了一个额外的时钟源,会增加芯片成本和芯片功耗。

为此,云途半导体在2020年9月9日申请了一项名为“一种高可靠性的锁相环模块及其输出时钟的切换方法”的发明专利(申请号:202010940406.3),申请人为苏州云途半导体有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项技术方案吧。

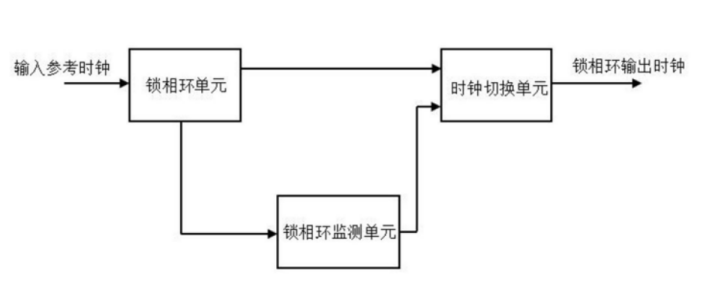

如上图,为该专利中公开的高可靠性锁相环模块的架构示意图。锁相环模块包括锁相环单元、锁相环监测单元、时钟切换单元。锁相环单元连接至锁相环监测单元,锁相环监测单元的输出和锁相环单元的输出分别连接至时钟切换单元。锁相环监测单元用于对锁相环单元的工作状态或参数进行监测,时钟切换单元根据锁相环监测单元的监测结果对锁相环模块的输出时钟进行切换。

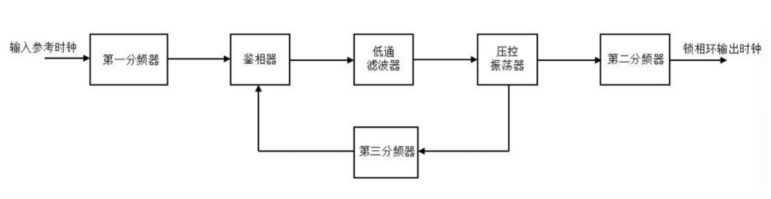

如上图,为上述锁相环单元的电路图。锁相环单元包括:第一分频器、第二分频器、第三分频器、鉴相器、低通滤波器以及压控振荡器。其中,第一分频器为输入参考时钟分频器,第二分频器为输出时钟分频器,第三分频器为锁相环分频器。

输入参考时钟输入到第一分频器的输入端口,第一分频器的第一输出端口连接鉴相器的第一输入端口,鉴相器的第一输出端口连接低通滤波器的输入端口。低通滤波器的输出端口连接压控振荡器的输入端口,压控振荡器的第一输出端口连接第二分频器的输入端口,第二分频器的第一输出端口用于输出时钟信号。

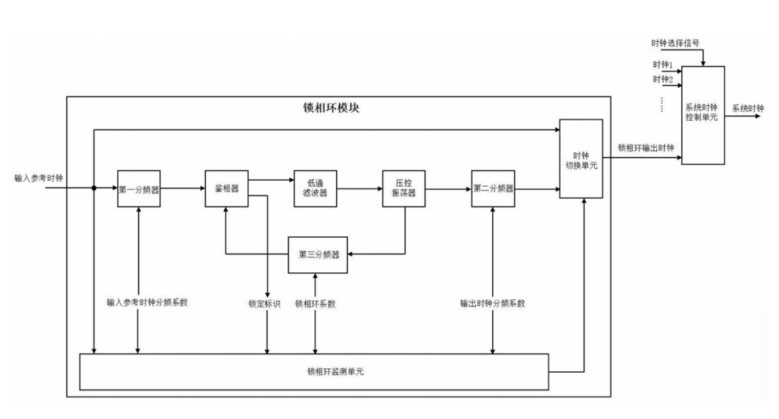

如上图,为锁相环模块的电路图,该锁相环模块还包括锁相环监测单元。第一分频器的第二输出端口、第二分频器的第二输出端口、第三分频器的第二输出端口、鉴相器的第二输出端口、输入参考时钟分别连接至锁相环监测单元。从而锁相环监测单元能够监测第一分频器的输入参考时钟分频系数、第二分频器的输出时钟分频系数、第三分频器的锁相环系数和鉴相器的锁定标识的变化,以及监测锁相环输入参考时钟频率是否在锁相环输入参考时钟频率阈值范围内。

因此,该锁相环单元不仅仅能够用于监测上述工作状态或参数,还能够用于监测锁相环单元的其他工作状态或参数的变化。根据锁相环监测单元监测的锁相环单元的工作状态或参数的类型和数量,锁相环监测单元还包括其他的器件,比如更多的触发器、比较器、检测器等,以更全面地监测锁相环单元的工作状态。

以上就是云途半导体公开的高可靠性的锁相环模块及其输出时钟的切换方案,该方案能够实现锁相环输出时钟的自动切换,降低了功耗,节约了成本。且能够避免因锁相环失锁以及锁相环输入参考时钟发生抖动所导致的系统故障、崩溃等问题,极大地提高了系统的稳定性和可靠性。