【爱集微点评】平头哥的RISC-V专利,通过对多条指令进行融合,从而在不增加指令的情况下,实现硬件加速,提升处理器核的性能。并且,因为没有增加额外的指令,也避免了与已有的处理器指令系统兼容性差的问题。

集微网消息,面对美国的制裁,阿里巴巴持续加大对RISC-V的投入,其芯片部门平头哥一直在加速RISC-V芯片架构在中国的商业应用。

精简指令集计算机(Reduced Instruction Set Computer,RISC)的指令系统相对简单,要求硬件执行有限且常用的一组指令,通过结合编译技术实现复杂的操作。精简指令集由简单指令合成,能够覆盖管线式处理器的大多数使用场景。随着现代处理器对性能要求的逐步提高,精简指令集覆盖不到的使用场景也需要进行硬件加速,目前的方式多为通过增加相应的指令来实现硬件加速,导致需要增加额外的指令编码来实现,且与现有的处理器指令系统的兼容性也较差。

为此,平头哥于2022年9月29日申请了一项名为“处理器核、处理器、芯片、控制设备和指令融合方法”的发明专利(申请号:202211197891.5),申请人为平头哥(上海)半导体技术有限公司。

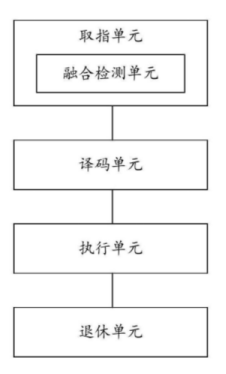

图1处理器核的示意性结构图

图1为本专利提出的一种处理器核的示意性结构图,包括取指单元、融合检测单元、译码单元以及执行单元。其中,取指单元用于获取时序相邻的两条机器指令,对于指令融合来说,可进行融合的指令通常为时序上连续的指令,因此,处理器核会对时序相邻的两条机器指令进行融合判断和处理。

融合检测单元用于判断两条机器指令是否满足融合条件,其中,该融合条件至少包括:两条机器指令分别为用于指示加减操作的第一操作指令和用于指示掩码操作的第二操作指令;若满足融合条件,则融合第一操作指令和第二操作指令,得到融合指令。

在此基础上,译码单元用于对融合指令进行译码操作,获得译码结果及融合指令对应的操作数。执行单元用于按照融合指令的操作指示,对操作数进行掩码操作,获得融合指令的执行结果。

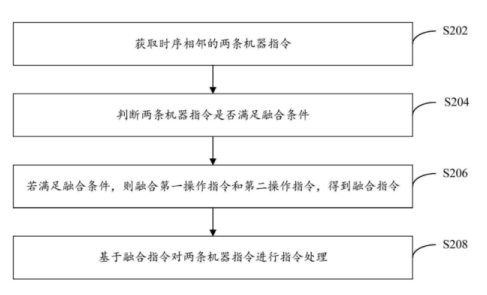

图2 指令融合方法的步骤流程图

图2为本专利提出的指令融合方法的步骤流程图,首先获取时序相邻的两条机器指令,不管何种应用或程序,其所实现相应功能或操作的代码最终都将被编译为计算机可懂的机器语言,即机器指令,交给处理器执行。指令的具体执行时序由编译结果确定,对于处理器来说,其通过获取机器指令,来进行相应的指令处理,实现机器指令所指示的操作和功能。例如,可通过如图1中所示的取指单元124来获取机器指令(步骤S202)。

然后,判断两条机器指令是否满足融合条件,为保证指令融合的顺利进行,在本发明中设置了相应的融合条件,当时序相邻的两条机器指令满足该融合条件时,则认为它们可以融合;否则,则认为它们不能融合(步骤S204)。

接着,若满足融合条件,则融合第一操作指令和第二操作指令,得到融合指令。两条机器指令被融合生成融合指令后,需要继续进行处理,为了使后续的处理单元能够明确获知当前指令为融合指令的信息,该生成的融合指令中除指令数据外,还携带有:用于指示当前指令是否为融合指令的指示信息(可通过指示位指示,如0表示非融合指令,1表示融合指令)、用于指示在当前指令为融合指令时的融合类型的信息(即用于指示第一操作指令在先还是第二操作指令在先的信息,如0表示第一操作指令在先,1表示第二操作指令在先)、立即数信息(步骤S206)。

最后,基于融合指令对两条机器指令进行指令处理。具体地,对融合指令进行译码操作,获得译码结果及融合指令对应的操作数,按照融合指令的操作指示,对操作数进行掩码操作,获得融合指令的执行结果。进而,在融合指令被成功执行后,也即在获得融合指令的执行结果后,还可以对融合指令对应的第一操作指令和第二操作指令一同进行退休处理,以完成指令的生命周期,并回收相关资源。

简而言之,平头哥的RISC-V专利,通过对多条指令进行融合,从而在不增加指令的情况下,实现硬件加速,提升处理器核的性能。并且,因为没有增加额外的指令,也避免了与已有的处理器指令系统兼容性差的问题。

阿里巴巴非常关注科技发展,认为RISV-C是未来计算机发展的方向,因此旗下平头哥加大了对RISV-C的研发投入,推出了一系列基于RISV-C的产品和解决方案,为公司带来了不少商业机会和竞争优势。可以说,平头哥的发展战略是十分明智和成功的。