文章来源:阿里云开发者社区

作者:云言·云议

简介:为了使处理器的处理能力得到充分发挥,存储系统必须能够提供与处理器性能相匹配的存储器带宽。 因此,处理器与主存储器之间的速度差距一直是处理器结构设计中必须考虑的问题。由于处理器内的核心数目增多,并且各核心采用共享存储器结构进行信息交互,对主存的访问需求进一步增加,在单处理器时代面临的存储墙问题依然存在,而且问题更加严重。 故必须针对多核处理器进行相应的存储结构设计,并解决好存储系统的效率问题。

1.多核系统的存储结构

目前的存储系统设计仍然采用存储器分级的方式解决存储速度问题,高性能的处理器采用二级甚至三级cache提高存储系统的等效访问速度,并且处理器片内的cache容量尽可能增大。但多核系统中的存储系统设计必须平衡系统整体性能、功耗、成本、运行效率等诸多因素。

因此,在多核处理器设计时,必须评估共享cache和私有cache孰优孰劣、需要在芯片内设置几级Cache等因素,cache的大小也是需要考虑的重要问题。

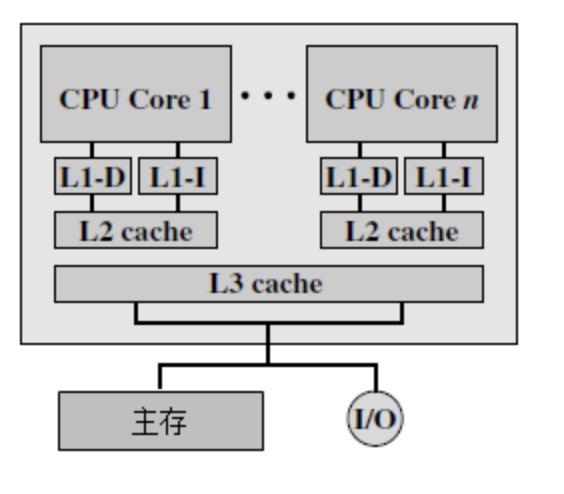

根据多核处理器内的cache配置情况,可以把多核处理器的组织结构分成以下四种,如图1所示。

- 片内私有L1 cache结构:简单的多核计算机的cache结构由L1和L2两级组成。处理器片内的多个核各自有自己私有的L1 cache,一般被划分为指令L1(L1-I)cache和数据L1(L1-D)cache。而多核共享的L2 cache则存在于处理器芯片之外。

- 片内私有L2 cache结构:处理器片内的多个核仍然保留自己私有的指令L1 cache和数据L1 cache,但L2 cache被移至处理器片内,且L2 cache为各个核私有。多核共享处理器芯片之外的主存。

- 片内共享L2 cache结构:结构与片内私有L2 cache的多核结构相似,都是片上两级cache结构。不同之处在于处理器片内的私有L2 cache变为多核共享L2 cache。多核仍然共享处理器芯片之外的主存。对处理器的每个核而言,片内私有L2 cache的访问速度更高。但在处理器片内使用共享的L2 cache取代各个核私有的L2 cache能够获得系统整体性能的提升。

- 片内共享L3 cache结构:随着处理器芯片上的可用存储器资源的增长,高性能的处理器甚至把L3 cache也从处理器片外移至片内。在片内私有L2 cache结构的基础上增加片内多核共享L3 cache使存储系统的性能有了较大提高。下图给出了这种结构的示意。

2.多核处理器的cache一致性

在多核系统设计时必须考虑多级cache的一致性(cache coherency)问题。

对内存的基本操作包括读操作和写操作。cache一致性问题产生的原因是:在一个处理器系统中,不同的cache和主存空间中可能存放着同一个数据的多个副本,在写操作时,这些副本存在着潜在的不一致的可能性。

在单处理器系统中,cache一致性问题主要表现为在内存写操作过程中如何保持各级cache中的数据副本和主存内容的一致,即使有I/O通道共享cache,也可以通过全写法或写回法较好地解决cache一致性问题。

而在多核系统中,多个核都能够对内存进行写操作,而cache级数更多,同一数据的多个副本可能同时存放在多个cache存储器中,某个核的私有cache又只能被该核自身访问。即使采用全写法,也只能维持一个cache和主存之间的一致性,不能自动更新其他处理器核的私有cache中的相同副本。这些因素无疑加大了cache一致性问题的复杂度,同时又影响着多核系统的存储系统整体设计。

维护cache一致性的关键在于跟踪每一个cache块的状态,并根据处理器的读写操作及总线上的相应事件及时更新cache块的状态。

一般来说,导致多核处理器系统中cache内容不一致的原因如下:

可写数据的共享:某个处理器采用全写法或写回法修改某一个数据块时,会引起其他处理器的cache中同一副本的不一致。

I/O活动:如果I/O设备直接连接在系统总线上,I/O活动也会导致cache不一致。

核间线程迁移:核间线程迁移就是把一个尚未执行完的线程调度到另一个空闲的处理器核中去执行。为提高整个系统的效率,有的系统允许线程核间迁移,使系统负载平衡。但这有可能引起cache的不一致。

对于I/O活动和核间线程迁移而导致的cache不一致,可以分别通过禁止I/O通道与处理器共享cache以及禁止核间线程迁移来简单解决。因而多处理器中的cache一致性问题主要是针对可写数据的共享。

在多核系统中,cache一致性可以使用软件或者硬件维护。

软件方法采取的手段是“预防”。在使用软件方式维护cache一致性时,处理器需要提供专门的显式cache操作指令,如cache块拷贝、cache回收和使cache失效等指令,让程序员或编译器分析源程序的逻辑结构和数据相关性,判断可能出现的cache一致性问题,利用这些指令维护cache一致性。软件维护cache一致性的优点是硬件开销小,缺点是在多数情况下对系统性能有较大影响,而且需要程序员的介入。

由于引入cache的主要目的是提升存储器的等效访问速度,故多数情况下cache一致性由硬件维护。硬件方法采取的手段是“通过硬件发现和解决所发生的cache一致性问题”。不同的处理器系统使用不同的cache一致性协议维护cache一致性。cache一致性协议维护一个有限状态机,并根据存储器读写指令或者总线上的操作进行状态转移并完成相应cache块的操作,以维护cache一致性。

目前,大多数多核处理器采用总线侦听(bus snooping)协议,也有的系统采用目录(directory)协议解决多级cache的一致性问题。目录协议在全局的角度统一监管不同cache的状态;而在总线侦听方式中,每个cache分别管理自身cache块的状态,并通过广播操作实现不同cache间的状态同步。

3.UMA架构与NUMA架构

可以根据处理器对内存储器的访问方式将共享存储器方式的计算机系统分为两大类,即统一内存访问(Uniform Memory Access,UMA)架构和非统一内存访问(Non Uniform Menory Access,NUMA)架构。

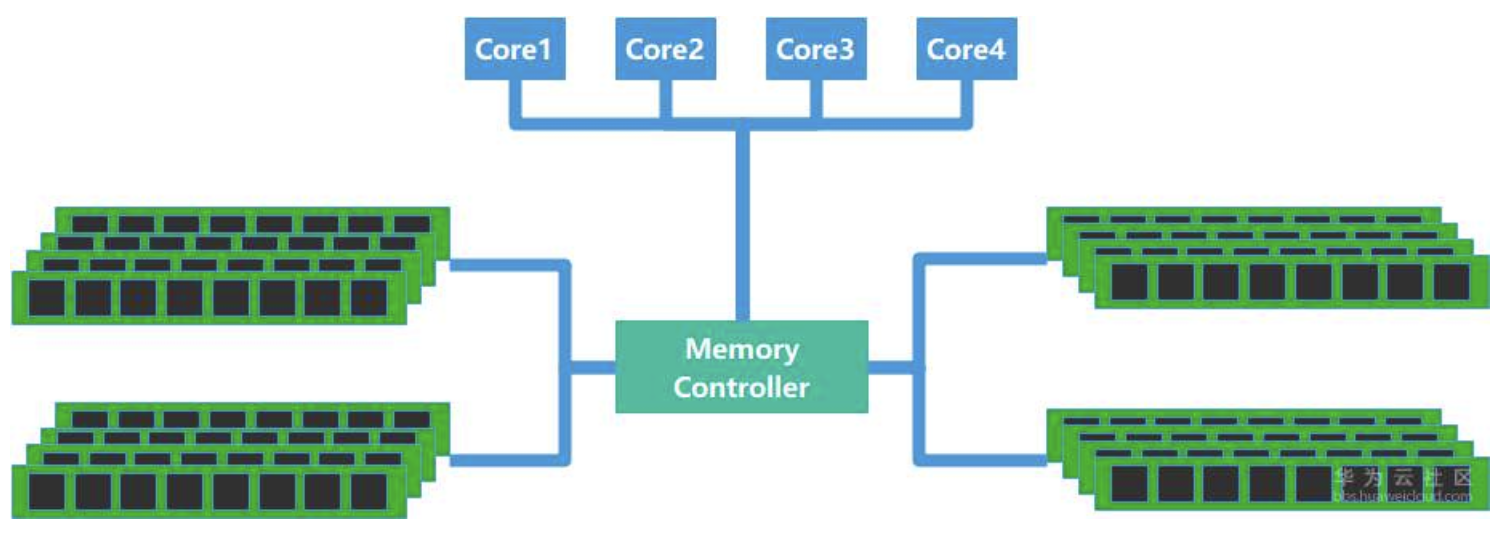

UMA是SMP计算机采用的存储器架构,因此SMP系统有时也被称为UMA架构系统。如图2所示,在SMP架构下,系统中的每个处理器核地位相同,其看到的存储器和共享硬件也都是相同的。在UMA架构的多处理器系统中,所有的处理器都访问一个统一的存储器空间,这些存储器往往以多通道的方式组织。在UMA架构下,所有的内存访问都被传递到相同的共享内存总线上,不同的处理器访问存储器的延迟时间相同,任何一个进程或线程都可以被分配到任何一个处理器上运行。每台处理器还可以配备私有的cache,外围设备也可以通过某种形式共享。因而UMA架构可以在操作系统的支持下达到非常好的负载均衡效果,让整个系统的性能、吞吐量有较大提升。

但从存储器访问的角度看,SMP架构的缺点是可伸缩性较差。这是因为多个核使用相同的总线访问内存,随着处理器核数的增加,总线将成为系统性能提升的瓶颈。因而UMA架构只适用于处理器核数量相对较少的情况,不适用于系统中配置数十个甚至数百个处理器核的情况。

文章来源:阿里云开发者社区

作者:云言·云议

推荐阅读

更多Arm服务器相关技术及移植干货请关注Arm服务器专栏。如要加入Arm Server微信群,请添加极术小姐姐(微信id:aijishu20)备注Arm服务器邀请加入。