最近,业界首个以算网融合为核心的多元算力研究报告《算力经济时代·2023新型算力中心调研报告》出版,我们将对报告内容开启连载模式。

结合算力经济时代的算力基础设施发展,第二章主要探讨了以下话题:

☞ 多元算力:CPU + GPU

☞ 摩尔谢幕,Chiplet 当道

☞ Chiplet 与芯片布局

☞ Arm 新升:NVIDIA Grace 与 AmpereOne

☞网格架构的两类 Chiplet

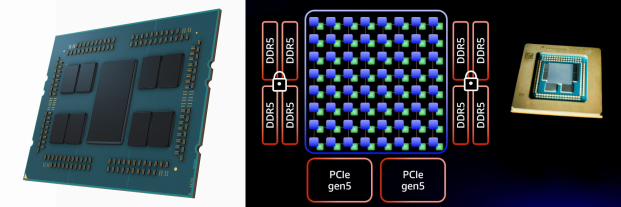

AmpereOne毕竟有多达192个核心和384MB L2缓存,采用渐趋流行的 Chiplet技术并不出人意料。目前比较普遍的推测是做法与AWS Graviton3 类似,即CPU及缓存单独一个die,DDR 控制器的die在其两侧,PCIe 控制器的 die在其下方。

把CPU核心及缓存,与负责外部 I/O 的控制器,分离在不同的die上,是服务器CPU实现 Chiplet 的主流做法。

△IOD居中的AMD第二代EPYC处理器与核心die居中的 AWS Graviton3 处理器

前面已经提到,AMD EPYC 家族处理器采取星形拓扑,把 I/O 部分集中放在1个IOD上,CPU核心及缓存(CCD)环绕四周的设计。网格架构的特性决定了CPU 核心及缓存必须在中间,I/O 部分分散在外围,所以拆分开时就是一个相反的布局。

共同点是中间的die大,四周的die小。

与EPYC家族的架构比,网格架构的整体性比较强,天生的单体式(Monolithic)结构,不太利于拆分。

网格架构必须考虑交叉点(节点)的利用率问题,如果有太多的交叉点空置,会造成很大的资源浪费,不如缩小网格的规模。

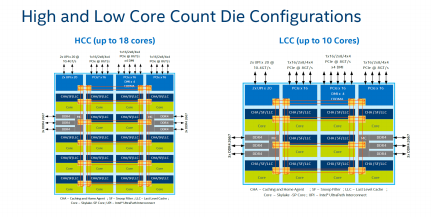

以初代英特尔至强可扩展处理器为例,为了满足从4 ~ 28个的核数(Core Count,CC) 变化范围,提供了3种不同构型的die(die chop),分别是:

● 6×6的XCC(eXtreme CC,最多核 or 极多核),可支持到 28 个核心;

● 6×4的HCC(High CC,高核数),可支持到18 个核心;

● 4×4的LCC(Low CC,低核数),可支持到10 个核心。

从这个角度来看,AmpereOne 不支持128 核及以下也是合理的, 除非增加die 的构型,而这又离不开公司规模和出货量的支持——量的问题还得量来解决。

第四代英特尔至强可扩展处理器就提供了2种构型的die,其中,MCC(Medium CC,中等核数)主要满足 32 核及以下的需求,这个核数要求比代号Ice Lake的第三代英特尔至强可扩展处理器的40核还要低,所以网格的规模也比后者的7×8还少1列,为7×7,在布局上最多可以安置 34 个核心及其缓存。

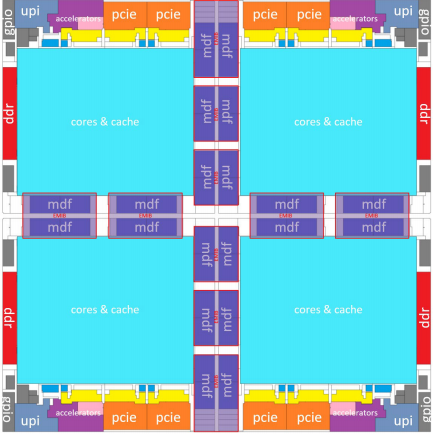

36 ~ 60 个核心的需求就必须由XCC来满足了,它就是前面提到过的 Chiplet 版本,把网格架构从中间切成了4等分,可谓独树一帜。

XCC 版的第四代英特尔至强可扩展处理器由2种互为镜像的die拼成2×2 的(大)矩阵,所以这个整体高度对称——上下、左右都对称,前三代产品和同代的 MCC 版都没有如此对称。

英特尔认为(XCC 版)的第四代英特尔至强可扩展处理器4个die拼接的效果是一个准单体式(quasi-monolithic)的die。单体式不难理解,常见的网格架构就是如此,第四代英特尔至强可扩展处理器外圈的左右有 DDR 内存控制器,上下是PCIe控制器和集成的加速器(DSA/QAT/DLB/IAA),UPI 位于四角,也是典型的网格 架构布局。

单体式前面的“准”是怎么达成的呢?就要看网格结构内部的“缝合” 技术了。

EMIB 及其带宽估算

如果没有采用Chiplet技术,XCC版本的第四代英特尔至强可扩展处理器应该是一个10 × 8的网格架构,最多60个核心,留下20个(节点)给 I/O。

如果直接把这个单体式的die四等分,那每一部分就应该是一个5×4的小网格。

但事实是这4个die要连为一体,就要为它们增加一行一列的连接 点,其中多出来的一行有4个,一列有6个。4个die对接到一起,就用20个交叉点形成了10个EMIB的“桥”。

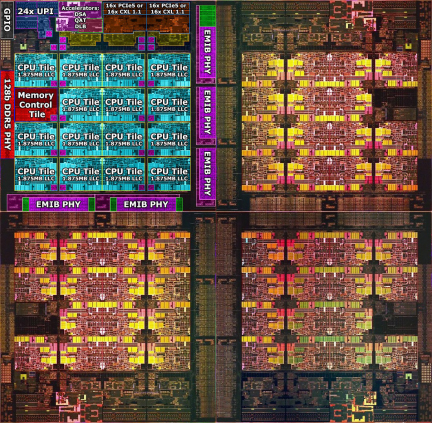

△ 第四代英特尔至强可扩展处理器的 EMIB 连接

EMIB(Embedded Multi-die Interconnect Bridge,嵌入式多芯片互连桥接)是英特尔用于实现2.5D封装的技术。第四代英特尔至强可扩展处理器内部封装了4个XCC 的die,每个die拥有14条EMIB互联,其中4条用于对外连接HBM2e内存,10条(6 横4 纵)用于相邻 XCC Tile 之间的互联。目前英特尔尚未公布 die 层面 EMIB 互联的具体带宽,我们仅能从工艺角度获知EMIB互联总线每对触点可以提供5.4Gb/s 以上的带宽(Pin Speed),凸块间 距为 55μm(微米),die之间的距离为100μm。

我们可以通过间接的方式进行估算。每die的4条EMIB对应16GB 8-Hi HBM2e。HBM2e每个引脚的数据传输率为3.2Gb/s,每堆栈(Stack)为 1024bit 位宽,总带宽为400GB/s 量级。因此,每条连接HBM2e的 EMIB PHY至少可以提供约100GB/s的带宽。将每堆栈HBM2e的1024bit 位宽均摊到4条EMIB,则为每条至少256bit。将EMIB每pin 5.4Gb/s 的带宽代入,则每条 EMIB 的理论带宽起码可以达到173GB/s。

将上述估算套回XCC的die间互联,则可知第四代英特尔至强可扩展处理器每个XCC 的互联带宽约为1 ~ 2TB/s 量级(1TB ~ 1.7TB/ s),相邻两个 XCC之间的互联为600GB/s ~ 1TB/s(左右向6组PHY)或400GB/s ~ 691GB/s(上下向 4 组 PHY)。(未完待续)