最近,业界首个以算网融合为核心的多元算力研究报告《算力经济时代·2023新型算力中心调研报告》出版,我们将对报告内容开启连载模式。

结合算力经济时代的算力基础设施发展,第三章主要探讨了以下话题:

☞ 报告连载 | 算存互连:Chiplet 与 CXL

☞ 报告连载 | 向上堆叠,翻越内存墙

☞ 报告连载 | HBM 崛起:从 GPU 到 CPU

☞ 报告连载 | 向下发展:基础层加持

☞ 报告连载 | 标准化:Chiplet 与 UCIe

☞ 报告连载 | UCIe 与异构算力

☞ 报告连载 | Chiplet 的中国力量

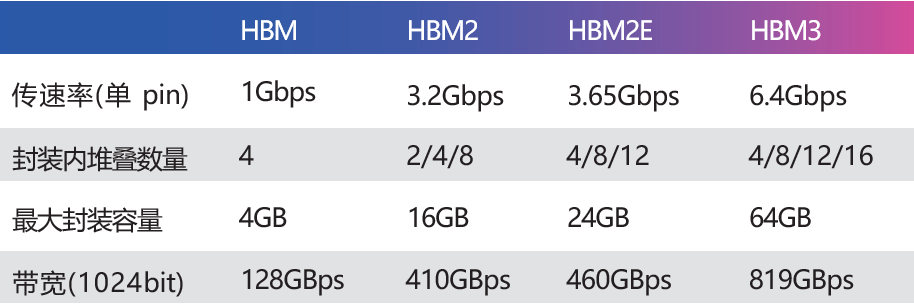

HBM是2014年AMD、SK海力士共同发布的,使用TSV技术将数个DRAM Die(晶片)堆叠起来,大幅提高了容量和数据传输速率。随后三星、美光、NVIDIA、Synopsys 等企业积极参与这个技术路线,标准化组织JEDEC也将从HBM2列入标准(JESD235A),并陆续迭代了HBM2e(JESD235B)以及HBM3(JESD235C)。得益于堆叠封装,以及巨大的位宽(单封装 1024bit) ,HBM提供了远超其他常见内存形态(DDR DRAM、LPDDR、GDDR 等)的带宽和容量。

典型的实现方式是通过2.5D 封装将HBM与处理器核心连接,这在CPU、GPU等产品中均有应用。早期也有观点把HBM视作L4 Cache,从TB/s级的带宽角度看,也算合理。而从容量角度,HBM就比SRAM或eDRAM大太多了。由此,HBM 既可以胜任(一部分)的工作,也可以当做高性能内存使用。

AMD是HBM的早期使用者,发展至今,AMD Instinct MI250X计算卡在单一封装内集成了2颗计算核心和8颗HBM2e,容量共128GB,带宽达到 3276.8GB/s。

NVIDIA应用HBM的主要是专业卡,其2016年的TESLA P100的HBM版搭配了16GB HBM2,随后的V100搭配了32GB HBM2。目前当红的A100和H100也都有HBM版,前者最大提供 80GB HBM2e、带宽约 2TB/s;后者升级到 HBM3,带宽约 3.9TB/s。

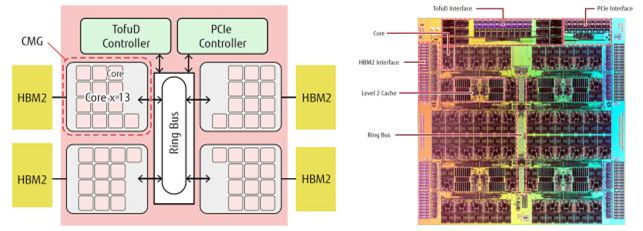

华为的昇腾910处理器也集成了4颗HBM。对于计算卡、智能网卡、高速 FPGA 等产品,HBM作为一种 GDDR 的替代品,应用已经非常成熟了。

CPU也已开始集成HBM,其中最突出的案例是曾经问鼎超算TOP500 的富岳(Fugaku),使用富士通研发的A64FX处理器。A64FX基于Armv8.2-A,采用7nm制程,每封装内集成了4颗HBM2,容量32GB,带宽1TB/s。

△ 富士通 A64FX CPU

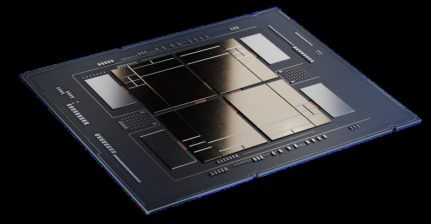

英特尔在2023 年1月中与第四代至强可扩展处理器一同推出的至强 Max 系列,在前者的基础上集成了64GB的HBM2e。这些HBM2e可以作为内存独立使用(HBMOnly 模式),也可以搭配DDR5内存共同使用(HBMFlat Mode 和HBM Caching Mode两种工作模式)。

△ Intel Xeon Max 系列,注意外围的 4 颗 HBM 芯片

中介层:CoWoS与EMIB

值得一提的是,目前 HBM与处理器“组装”在一起都需要借助硅中介层。传统的ABS材质基板等难以胜任超高密度的触点数量和高频率。但硅中介层有两种技术思路,代表是台积电的CoWoS(chip-on-wafer-on-substrate)和英特尔的EMIB(Embedded Multi-Die Interconnect Bridge)。

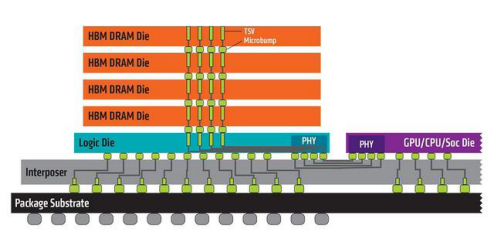

△ HBM的基本结构。左侧彩色的5层结构为HBM封装。灰色为中介层

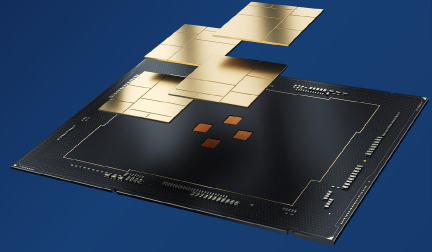

台积电CoWoS-S通过硅中介层承载处理器和HBM。其硅中介层也被称为硅基础层,因为中介层会完全承载其他芯片。换句话说,处理器和若干 HBM的投影面积决定了硅基础层的大小,而基础层的面积会限制HBM的使用数量(常见的就是 4 颗)。硅中介层使用65nm之类的成熟工艺制造,其成本并不高昂,但尺寸受限于光刻 掩膜尺寸。

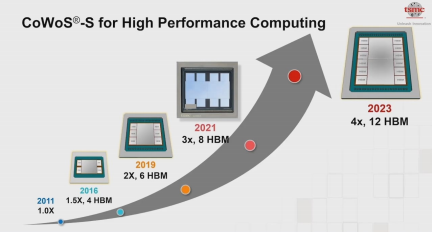

这就成为了早期HBM应用的瓶颈—— 需要HBM的往往是高性能的大芯片,而大芯片的规模本身就已经逼近了掩膜尺寸极限,给HBM留下的面积非常有限。到了 2016 年,台积电终于突破了这个限制,实现1.5倍于掩模尺寸的中介层,从此单芯片内部可封装4颗HBM,这就是当前市场上的主流形态了。

△ 台积电 CoWoS-S 发展路线

2019年,台积电宣称实现2倍掩膜尺寸,可以支持6颗HBM了。很快,2020年发布的NEC SX-Aurora TSUBASA 矢量处理器,集成6颗共48GB HBM2;同年的英伟达A100则是6颗共40GB HBM2e(有一颗HBM未启用)。

至于可以封装12颗HBM的巨型芯片,预计面积将达到3200平方毫米。硅中介层的面积如此发展,下一个瓶颈就是硅晶圆的切割效率了。

另一种思路是英特尔的 EMIB,使用的硅中介层要小得多。以第四代英特尔至强可扩展处理器的渲染图为例,棕色的小方块就是EMIB 的“桥”,用以将 4个 XCC的die拼为一个整体;而在至强Max 系列中,每个die还需要通过 EMIB去连接对应的HBM芯片。结合HBM的架构示意图可以看出,英特尔认为只需要通过硅中介层连接内存和处理器的 PHY 部分,其他信号依然可以直通基板。整体而言,EMIB充分利用了硅中介层和有机载板的技术特点和电气特性,但也存在组装成本高的缺点(需要在有机载板中镶嵌,增加了工艺复杂度,限制了载板的选择)。

当然,对于更复杂的“组装”,英特尔也有对应的方案,如代号Ponte Vecchio的英特尔数据中心GPU Max系列整合了基于5种制造工艺生产的47个小芯片,其中的基础层(Base Die)的面积为650m㎡。该产品综合了 Foveros 3D封装和 EMIB2.5D封装的特点,纵向横向齐发展。(未完待续)