1. 背景

伴随着摩尔定律近30年的持续生效,CPU的运算速度迅速提升,而存储器(主要是内存)的速度提升相对较慢。这导致了存储器与CPU之间的速度差异,也称为存储器墙(Memory Wall)。当CPU执行指令时,如果需要从内存中读取数据或指令,由于存储器速度的限制,CPU可能需要等待访存操作完成,从而导致性能瓶颈。

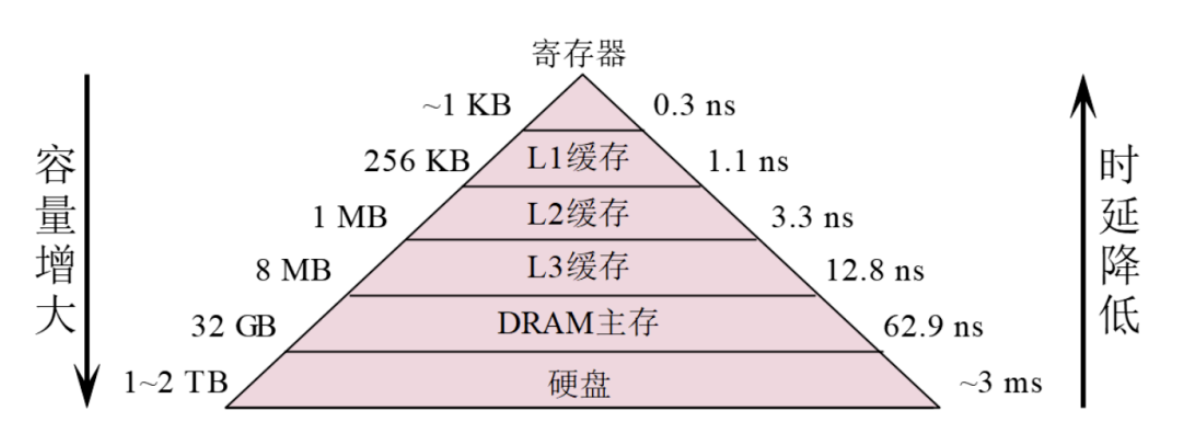

现代计算机系统为了解决访存瓶颈问题,一般采用了多级缓存和内存层次结构,包括L1、L2、L3缓存以及主存等。虽然高速缓存(Cache)能够提供更快的访问速度,但其容量有限。当CPU访问的数据无法在高速缓存中找到时,就需要从更慢的内存层级中获取数据,这会导致较高的访存延迟和性能下降。

2. 预取技术

预取(Prefetching)技术可以在一定程度上解决访存成为CPU性能瓶颈的问题。预取是一种提前将数据或指令从内存中预先加载到高速缓存中的技术[1]。通过预取,CPU可以在实际使用之前将数据预先加载到缓存中,从而减少对内存的访问延迟。这样可以提高访存的效率,减少CPU等待访存的时间,从而提升整体性能。

预取技术一般分为软件预取技术和硬件预取技术。

2.1 软件预取

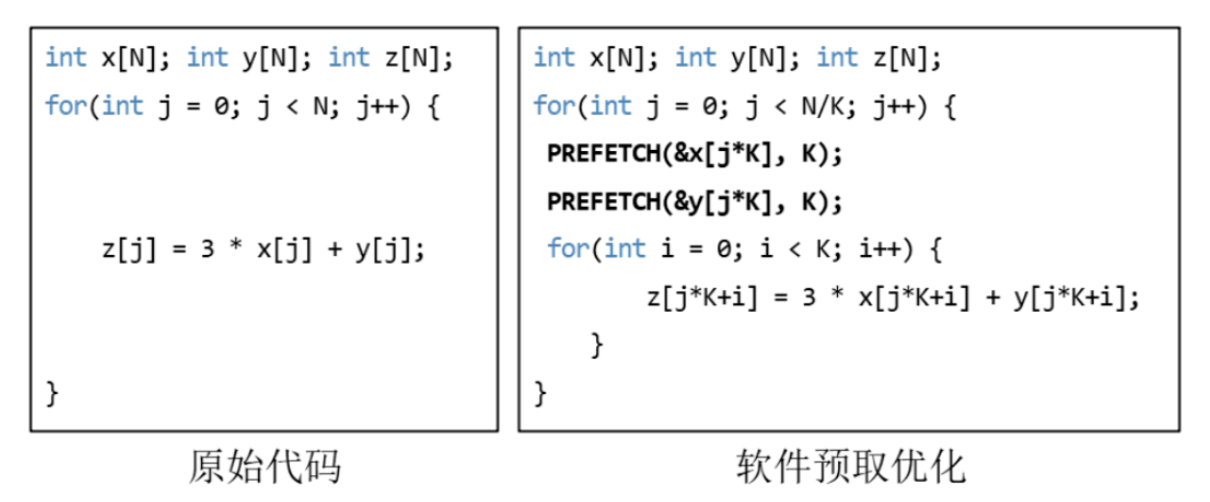

软件预取指的是软件可以通过编程的方式显式地指示CPU需要预取的数据。程序员可以通过一些特定的指令或者编译器选项来实现软件预取,以指导CPU进行数据的预取操作[2]。

软件预取技术主要分为:

- 显式预取指令:早期的软件预取技术是通过在程序中插入特定的指令来指示CPU进行预取操作。这些指令可以直接告知CPU需要预取的数据,但需要由程序员手动插入,且对程序员要求较高。

- 编译器优化:随着编译器技术的发展,编译器可以通过静态分析程序的访存模式和数据依赖关系,自动生成预取指令或者优化程序结构,以提高预取效果。编译器优化在一定程度上减轻了程序员手动插入预取指令的负担,并提供了更好的性能优化能力。

但是,软件预取技术同时也面临一些问题和挑战:

- 预取决策困难:软件预取需要程序员或编译器对程序的访存模式进行分析和决策,但准确预测程序的内存访问行为并不总是容易的。错误的预取决策可能导致额外的内存访问延迟,降低性能。

- 数据依赖关系:在存在数据依赖关系的情况下,过早的预取可能导致错误的结果,因为预取的数据可能在实际使用之前被修改或无效。因此,需要仔细分析程序的数据依赖性,避免错误的预取。

- 软件开销:软件预取可能需要在程序中插入额外的指令或使用特定的编译器选项,这会增加程序的复杂性和开发成本。此外,预取指令的插入可能会占用宝贵的指令缓存空间。

2.2 硬件预取

硬件预取指的是CPU内部的硬件逻辑可以通过预测程序的访存模式,主动地将预测的数据加载到高速缓存中。这种方式可以通过分析程序的访存模式和数据的局部性来预测需要预取的数据,并将其加载到高速缓存中[3]。主要包括:

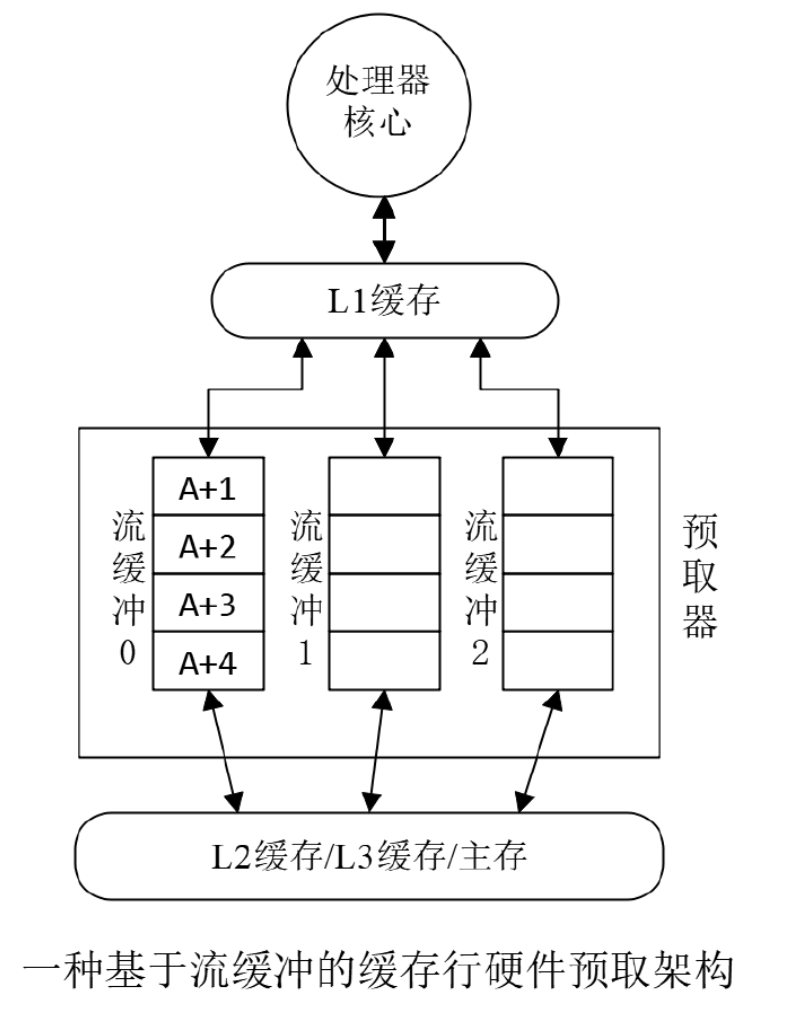

- 基于缓存行的预取:早期的硬件预取技术主要是基于缓存行(cache line)的预取,即将整个缓存行的数据一次性加载到高速缓存中。这种方式适用于具有良好局部性的程序,并能够提高数据的连续性访问。

- 基于访存模式的预测:随着CPU内部逻辑的发展,硬件预取技术开始引入更复杂的预测机制。通过分析程序的访存模式、数据依赖关系和历史访问模式,CPU可以预测下一个可能的内存访问并提前加载数据,从而减少等待时间。

同样,硬件预取技术也面临一些问题和挑战:

- 预取精度:硬件预取技术需要根据预测算法和历史访问模式来预测下一个可能的内存访问,并将数据加载到高速缓存中。然而,预测的准确性并不总是百分之百,可能存在预测错误的情况。错误的预取可能导致额外的内存访问延迟或浪费缓存空间。

- 内存带宽压力:高效的硬件预取可能导致大量的数据被预取到高速缓存中,这可能增加内存带宽的需求。如果预取的数据过多或过频繁,可能会对内存子系统造成压力,降低整体性能。

综上,软件预取技术和硬件预取技术都面临一些挑战,例如,预取需要准确地判断出什么时候、以及预取多少数据是最有效的,这需要对应用程序的访存模式和数据依赖关系有深入的理解。预取的策略选择、预取窗口的大小和预取触发时机等都需要进行合理的设计和优化。

3. 软硬件协同预取技术

软硬件协同预取是指软件预取技术和硬件预取技术的结合,通过软硬件协同的方式来提高预取效果和系统性能。随着计算机体系结构的发展和硬件设计的改进,软硬件协同预取得到了越来越多的关注和研究[4]。

软硬件协同预取可以在一定程度上解决软件预取和硬件预取各自的问题,但并不一定能够完全解决所有问题。它通过软件和硬件的协同工作,以及利用动态调整和智能化的技术,可以提高预取的准确性和效果,从而改善系统性能。

软硬件协同预取的优势和解决方面的问题如下:

- 提高准确性:软硬件协同预取可以结合软件的预测信息和硬件的预测机制,以提高预取的准确性。软件可以提供更精确的预取指令或指示,而硬件可以通过预测算法和历史访存模式进行智能预取。这种协同工作可以在一定程度上解决软件预取和硬件预取的决策困难和预测精度的问题。

- 动态调整和自适应性:软硬件协同预取可以根据实际运行时的程序行为和访存模式动态调整预取策略和算法。通过监测程序的执行情况和访存模式,软硬件可以自适应地调整预取决策,以适应不同的应用场景和数据访问模式。这种动态调整和自适应性可以一定程度上解决软件预取和硬件预取的数据依赖关系和预测精度的问题。

然而,软硬件协同预取仍然面临以下挑战和限制:

- 复杂性和开销:软硬件协同预取需要在软件和硬件层面进行协同工作,涉及到复杂的协议、通信和数据交互。这增加了设计和实现的复杂性,并可能引入一定的开销。

- 预测错误和冲突:即使软硬件协同预取可以提高预取的准确性,仍然存在预测错误的可能。预测错误可能导致额外的内存访问延迟、浪费缓存空间等问题。此外,软硬件之间的预取决策可能存在冲突,需要合理的协同策略来处理。

- CPU指令集生态的影响:软硬件协同预取一般需要修改软硬件之间的接口——指令集,这会导致对原有指令集的兼容性破坏,CPU指令集架构生态的分裂。

因此,虽然软硬件协同预取能够在一定程度上解决软件预取和硬件预取的问题,但仍然需要综合考虑各种因素,并根据具体情况进行权衡和优化。这需要继续进行研究和改进,以进一步提高预取技术的效果和性能。

4. 总结

本文提到的软件预取、硬件预取和软硬件协同预取技术均是针对访存性能瓶颈的优化技术。

软件预取是通过在软件层面分析应用程序的访存模式,提前将预测的数据或指令加载到缓存中,以减少访存延迟。软件预取可以根据应用程序的特点和访存模式进行灵活的调整,但需要对应用程序有深入的了解。

硬件预取是通过硬件设计和改进缓存子系统,在硬件层面自动预测和加载数据到缓存中。硬件预取可以在无需软件干预的情况下提高访存性能,但预测准确性可能受到限制。

软硬件协同预取结合了软件和硬件的优势,通过软硬件的协同工作来最大程度地提高访存性能。它结合了软件层面的访存分析和硬件层面的预取机制,以更准确地预测和加载数据到缓存中。

综上所述,软件预取、硬件预取和软硬件协同预取是针对访存性能瓶颈的优化策略。它们在不同层面上提供了不同的优化方案,旨在减少访存延迟、提高数据局部性,并通过预测和加载数据到缓存中来提高系统的整体性能。在实践中,需要综合考虑应用程序的特点、访存模式和硬件实现的限制,以选择合适的预取技术和策略,从而优化访存性能。

参考

- Introduction to Caches: Prefetching

- Compiler Algorithms for Prefetching Data

- A Primer on Hardware Prefetching

- An Integrated Hardware/Software Data Prefetching Scheme for SharedMemory Multiprocessors

作者:孙文博、张振东

来源:毕昇编译

推荐阅读

欢迎大家点赞留言,更多Arm技术文章动态请关注极术社区嵌入式客栈专栏欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。