数据和指令必须与合适的边界保持对齐(alignment)。访问是否对齐会影响ARM核的性能,并且在将代码从早期的体系结构移植到ARMv8-A时可能会出现可移植性问题。出于性能原因,或者在移植代码时,都值得去注意下对齐问题。本文将讲述了ARMv8-A AArch64的对齐。

一、指令对齐

指令对齐(Instruction alignment)比较简单,A64指令必须word对齐。如果从非对齐位置读取指令的话,会报PC对齐错误。

二、数据访问对齐(Alignment of data accesses)

数据访问对齐(Alignment of data accesses)稍微复杂点,取决于访问类型、地址属性、系统支持的特性和系统的配置等。

2.1 Device memory

Device memory可以分为多种,不过任何非对齐访问Device memory都会上报对齐错误。

2.2 Normal memory

对Normal memory的非对齐访问取决于以下所有条件:

- 访问内存的指令类型;

- 访问地址的内存属性;

- SCTLR_ELx.{A, nAA}寄存器域段的值;

- FEAT_LSE2是否实现;

以下可以分为几类指令来说:

1.对于Load or Store of Single or Multiple registers instructions,不包含exclusive,acquire/release,atomic和MCMS指令,如果访问的数据块与地址非对齐,那么:

- 如果SCTLR_ELx.A==1,那么上报alignment fault。

- 如果SCTLR_ELx.A==0,那么允许unaligned访问。但是访问是否保证single-copy atomic取决于地址属性和FEAT_LSE2是否实现。

2.对于Load-Exclusive/ Store-Exclusive and Atomic instructions,如果访问的数据块与地址非对齐,那么:

- 如果SCTLR_ELx.A==1,那么上报alignment fault。

- 如果SCTLR_ELx.A==0,那么是否允许访问取决于地址属性和FEAT_LSE2是否实现,如果允许访问,那么就算是非对齐,也要保证single-copy atomic。

3.对于Non-atomic and non-exclusive Load-Acquire/Store-Release instructions,如果访问的数据块与地址非对齐,那么:

- 如果SCTLR_ELx.A==1,那么上报alignment fault。

- 如果SCTLR_ELx.A==0,那么是否允许访问取决于地址属性和FEAT_LSE2是否实现,以及要看SCTLR_ELx.nAA的值。SCTLR_ELx.nAA决定了访问的数据块跨地址16-byte边界是否允许访问。

- 对于Memory Copy and Memory Set instructions, 如果访问的数据块与地址非对齐,那么:

- 无论SCTLR_ELx.A的值为多少,都会进行对齐检查,也就是会上报alignment fault。

- 如果Xn不是16的倍数,也会上报alignment fault。

- 如果Xd没有对齐到16的倍数,也会产生alignment fault。

三、总结

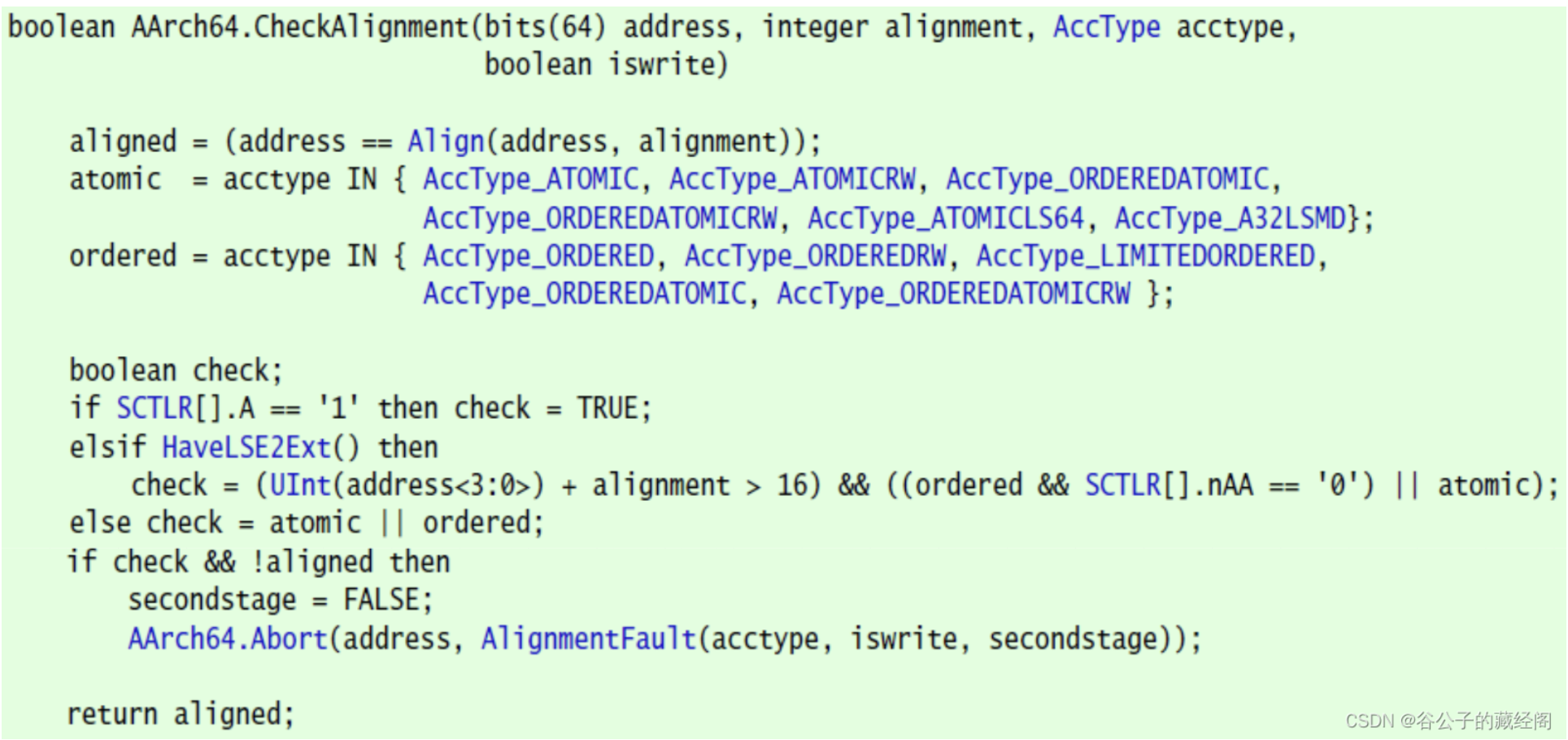

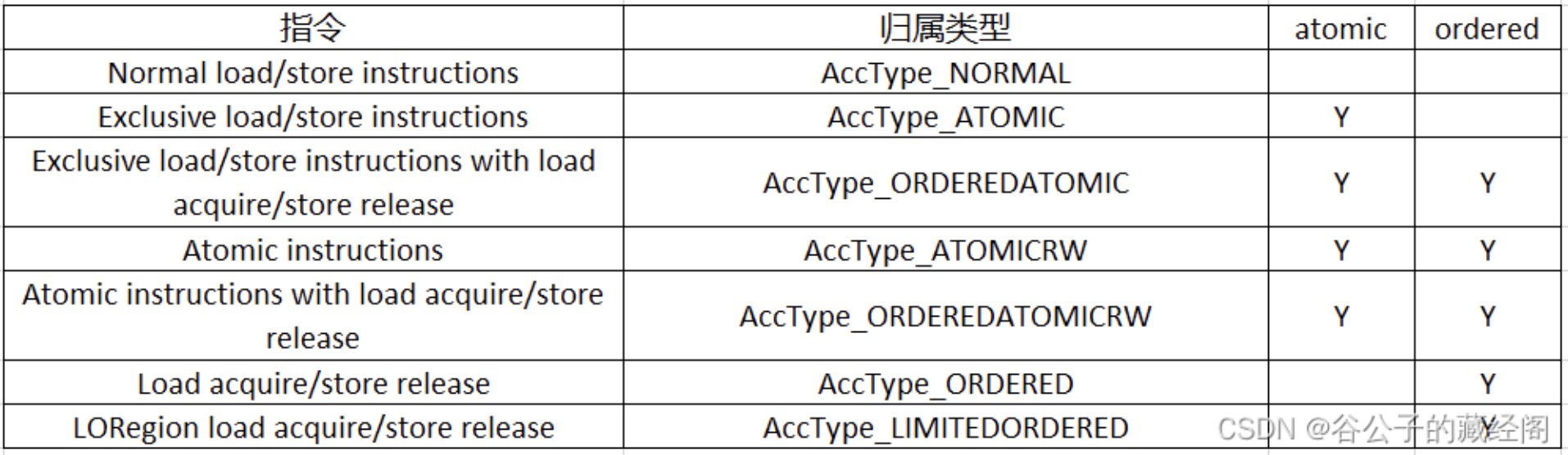

可以用下面的伪代码和指令归属类型来总结上述内容,就很容易明白了。

判断alignment fault伪代码:

指令归属类型:

作者:谷公子

文章来源:CSDN

推荐阅读

更多IC设计干货请关注IC设计专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。