使用异步FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法。在异步FIFO中,读指针在读时钟域,写指针在写时钟域,所以不能单独运用一个计数器去产生空满信号了。因此,须要将写指针同步到读时钟域去产生空信号,将读指针同步到写时钟域去产生满信号。

对异步FIFO的读、写指针进行判断,我们首先需要将其同步到统一的时钟域下,而这就引发出了新的问题—-读、写指针在大多数情况下都不是个单bit信号,而是个多bit信号。如果读、写指针直接使用二进制的形式进行同步,则难以避免同步过程中会出现的多个bit信号同时变化的问题。如7(0111)跳转到8(1000),此时有4个bit信号都发生了变化,如果直接同步,则由于不同信号之间的延迟(skew)差别,可能导致亚稳态、错采、漏采等等问题。为解决因可能的skew问题造成的亚稳态所以采用格雷码异步FIFO,格雷码每相邻位之间只有一个比特的变化。FIFO的指针是递增的,这使得在传输递增的多bit信号时,格雷码具有天然的优势。

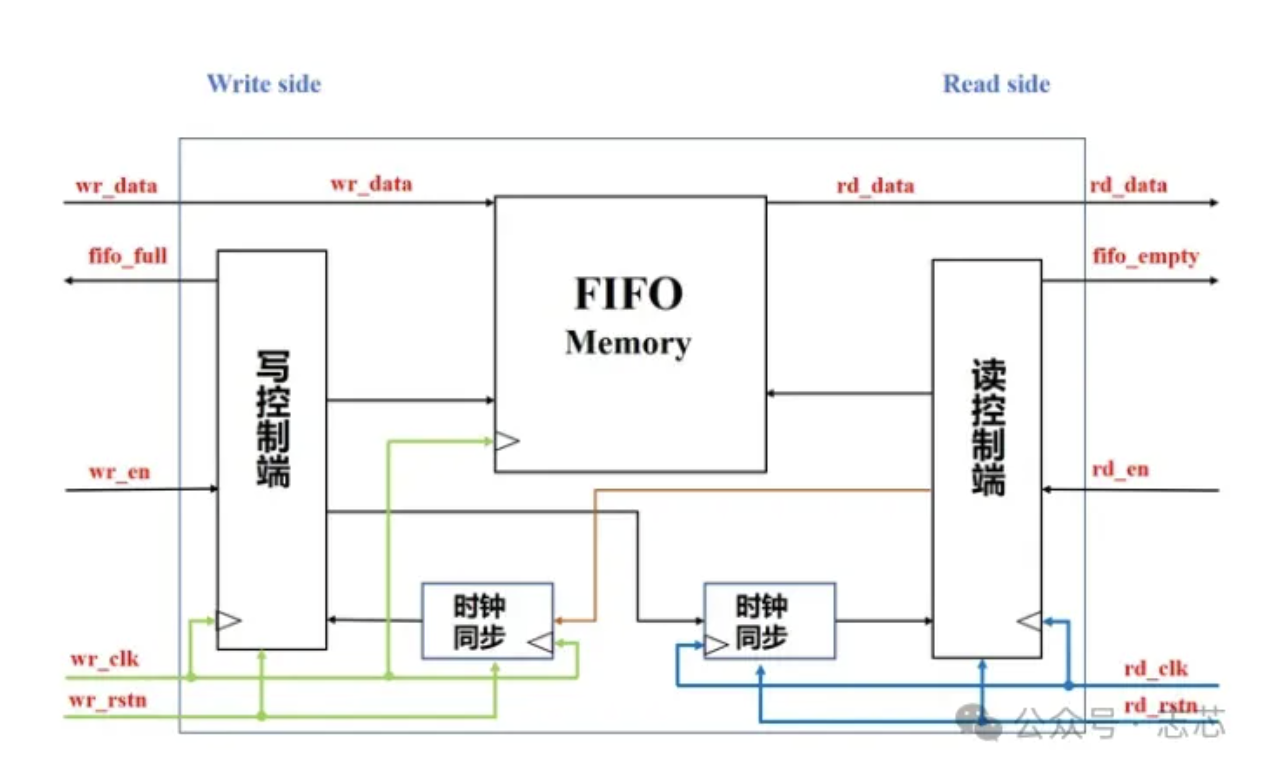

下图为常见格雷码异步FIFO组成框图,包含四个主要部分。FIFO写控制端用于判断是否可以写入数据,读控制端用于判断是否可以读取数据,FIFO Memory用于存储数据,两个时钟同步模块用于将读写时钟进行同步处理。

下图为时钟同步模块的组成示意图。写操作时,时钟同步模块先将写地址指针转换成格雷码,然后通过两级同步器(两级同步在读时钟下进行),将写地址指针同步到读时钟域下;读操作时,时钟同步模块先将读地址指针转换成格雷码,然后通过两级同步器(两级同步在写时钟下进行),将读地址指针同步到写时钟域下。

格雷码异步FIFO解决了跨时钟的数据同步化问题,但如果不额外约束还可能存在其他两个问题;一是格雷码各比特位延时不一致,导致同步器采样的地址不符合gray规律,导致FIFO功能异常;二是格雷码到两级同步器的延时太大,导致异步FIFO性能下降。

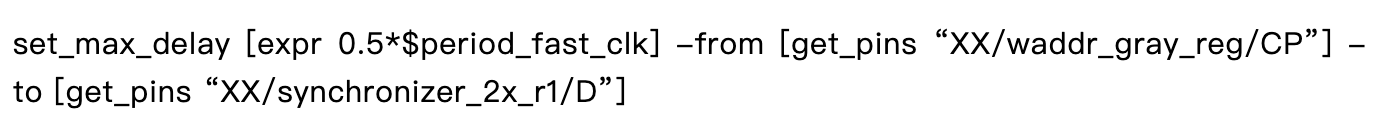

为了解决上述两个问题,一般采用set_max_delay来对写操作时from point(写地址格雷码转换模块中的最后一个寄存器的时钟端口)到to point(两级同步器的第一级寄存器的数据端口)的max delay进行约束;对读操作时from point(读地址格雷码转换模块中的最后一个寄存器的时钟端口)到to point(两级同步器的第一级寄存器的数据端口)的max delay进行约束;延时可设置为读写时钟中最快时钟周期的一半,也可以设置成源端时钟的一半。例如:

为了解决上述两个问题,还会使用set_clock_groups -asynchronous将所涉及的读写时钟设置为异步时钟群组。这种约束和false path的区别很大;false path会认为该path上的timing arc不用去分析时序、DRV(max trans、max cap 和max fanout 等)以及串扰噪声情况,也就是说工具会认为false path上的时序和信号质量对设计功能没影响;set_clock_groups -asynchronous也不分析两个时钟域之间的交互的path上时序情况,但是会分析该path上的timing arc的DRV和串扰噪声情况,保证信号质量。例如:

set_clock_groups -asynchronous -group clock1 -group clock2

END

作者:Jack Xu

文章来源:志芯

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。