PCI兼容的配置访问机制(Configuration Access Mechanism,CAM):完全兼容PCI

1. 一体机 (All-in-One Machine)2025年上半年最火的AI产品是什么?绝对是DeepSeek一体机。没有之一。一体机,顾名思义,就是将计算、存储和部分互联功能集成在单个机箱内的智算机器。一般配置 1到2颗通用型 CPU,核心数量适中,主要负责操作系统运行、任务调度以及一些非计算密集型的工作负载。当然AI一体机中少不了GPU...

上文我们讲了两种算法来量化单个任务的负载,同时遗留了一个问题,就是小任务,到底是选择大核运行还是小核运行。

Xcelium使用命令行选项来启用和控制低功耗仿真。所有与低功耗仿真相关的命令选项都以-lps_前缀开头的。

有人说FPGA和ASIC是一回事,这就跟认为种麦子的人一定会种水稻一样,这样的人低估了全人类的智慧,不管左脚还是右脚,随便用哪个脚趾头想一想就知道,如果是一回事,还用得着用两个名字吗?俗话说,不知道就不要说话,术业有专攻,专业的事交给专业的人去做。

Type[7:0] 表示了TLP Header Base的类型和Size。TLP Header Base之后紧跟的0到7DW的Orthogonal Header Content (OHC) 内容则由OHC[4:0]指定。

在芯片设计中,通常都会增加一些debug(调试)电路逻辑,方便定位软硬件问题。增加这些debug电路的基本要求对系统原有的正常操作无影响,否则可能会出现heisenbug。因此,debug逻辑电路通常用额外的专用资源去实现,debug面积占用超过总芯片面积5%的芯片也不在少数。

生成事务层数据报文(TLP):接收设备核心层(Device Core)的数据请求(如数据读写、完成反馈、信息传递等),将其转换为标准的 PCIe 总线事务,并封装成事务层数据报文(TLP,Transaction Layer Packet)。TLP 主要包含头部(Header)、数据负载(Data Payload,可选)和端到端循环冗余校验(ECRC,End - to - End CRC...

在进行编码时,我们时常会使用到乘法器,除法器,等较复杂功能模块,为此 fpga vendor 设计定制了 IP 核,用户通过调用 IP 核来实现所需功能,耗费资源少且利于时序收敛。我们在日常 verilog 编码过程期望通过参数化的方式调用 IP 核。例如 IP 的位宽,时延,部分关键特性期望可以通过参数调用的方式实现,而不是通过打...

锁相环(PLL)是通信和时钟系统的核心模块,其设计需在噪声、功耗、面积等多维度权衡。本文基于ISSCC 2021课程内容,系统梳理PLL的设计挑战与解决方案,为工程师提供技术参考。

在当今数字化时代,芯片作为现代科技的核心,其复杂度和重要性都在不断攀升。从智能手机到 AI,从汽车电子到 IOT,芯片无处不在,而其质量的优劣直接决定了产品的性能和可靠性。然而,随着芯片制程的不断缩小(如今已达到 18A 甚至更小),芯片的规模和复杂度急剧增加,测试难度也呈指数级增长。测试作为芯片尤为重要的...

在学习了比较简单的DDR3的大部分知识后,我们来增量的学习DDR4/DDR5,然后再去研究一下DDR控制器。

首先就要先来提一提ACPI (Advanced Configuration and Power Interface)。ACPI旨在为操作系统和应用程序提供所有芯片电源管理的接口。

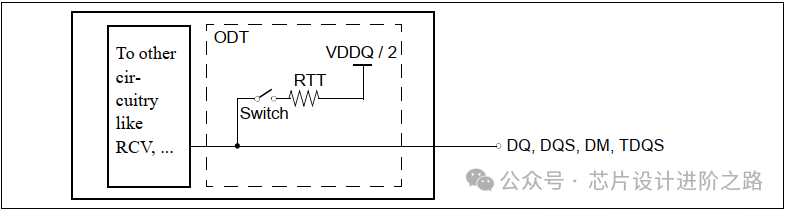

在 DDR 技术的演进过程中,ODT(On-Die Termination)和 OCD(Off-Chip Driver Calibration)成为了确保信号完整性和提升数据传输效率的关键技术。ODT 通过在内存芯片内部实现阻抗匹配,有效减少了信号反射和干扰,而 OCD 则通过动态调整输出驱动强度,优化了信号的稳定性和传输质量。本文将基于 DDR3 深入探讨这两种技...

这篇文章之前发过,当时主要是为 FPGA 的复位而写的文章,文章内的一些复位优缺点,对 IC 同样适用,考虑到这是面试常问的一个问题,所以重新发一下。一些基础的知识可以看看 Clifford E. Cummings 的一些论文。

在当今数字化时代,芯片作为现代科技的核心,已经渗透到我们生活的每一个角落。从智能手机到人工智能,从汽车电子到物联网设备。

虽然目前世界上都在推行可读性好、可维护性好的 RTL 编码规则,一大堆公司机构也都推出了各种各样的编码规范,网上一搜索各种好的编码规则规范一箩筐,但是当你实际打开代码后,你会发现理想很丰满,现实很骨感,你看到的代码简直比散文还要散。下面给出一些编写散装代码的建议。

这是Arm第一款做的比较成熟的服务器核Neoverse N2,前面的系列Neoverse N1是由移动端A76改进而来,但相对而言没有那么成熟,或者说性能没那么高,这款核在市场上反馈良好,并且以低功耗以及平衡性能的特点占据了一定的市场,本文将分析这款核的一些设计特点。

Arm Holdings 的商业模式独树一帜:它专注于设计和授权知识产权(IP),而非亲自制造芯片 1。这一模式是理解市场上为何存在如此多样化的基于 Arm 处理器的根本原因。Arm 架构已渗透到各个市场领域,从移动设备和嵌入式系统到汽车电子和基础设施,其无处不在的特性也促成了大量产品名称的出现 1。据统计,“Arm 是世界上...

我们在编写一些比较复杂的 Verilog 代码时,通常需要进行大量的手动连线工作,这种工作十分容易出错,并且在代码模块的嵌套层级较多时,更改里层的一个代码,可能就需要更改其外部一系列模块的端口信息等,因此,使用 emacs 工具能快速实现大批量的、复杂的 Verilog 模块之间的连线操作。