主要是 PC 和移动端,Arm,Apple,Intel,AMD,因为应用场景不同参数不一定有实际的比较价值。目前亦安最关注的是 Arm Server 的 V/N 系列,Arm 的 Server V3/N3 没有拿到什么可靠的数据也没法比,官方还没公开太多信息。后续我会发些 Arm 移动端的核,现在先宏观聊聊,有其它微架构问题可以加我微信讨论。

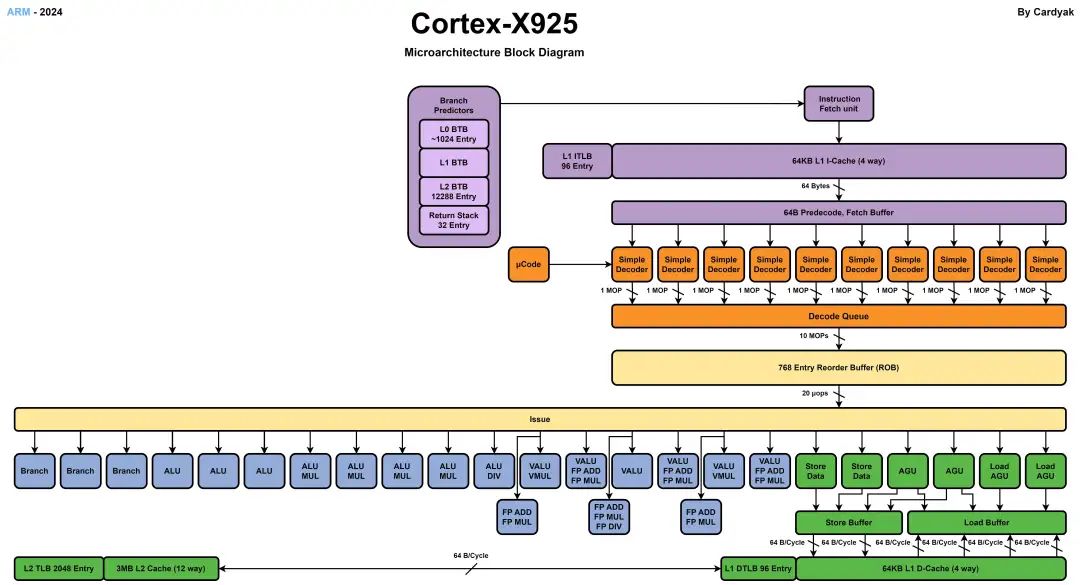

Arm X925

被 Arm 寄予厚望 X925,一度被宣传为将要超过 Apple 的重要大核,Decode 宽度达到 10,Dispatch 宽度达到 10,Issue 宽度达到 23,执行端口达到 23,786 的 ROB,L2 高达 3MB。进步的速度真的太快了,这次真的遥遥领先了,关键的是 X925 功耗比 AMD 和 Intel 低非常多,这样比较可能不那么公平,但 Arm 今年推出的 V3/N3 服务器核性能依然处在一线水准,并且由于 V2/N2 的良好市场反馈,不少云商已经逐步开始部署 Arm 架构的服务器。对 X86 而言,他们的危机可能刚刚开始。

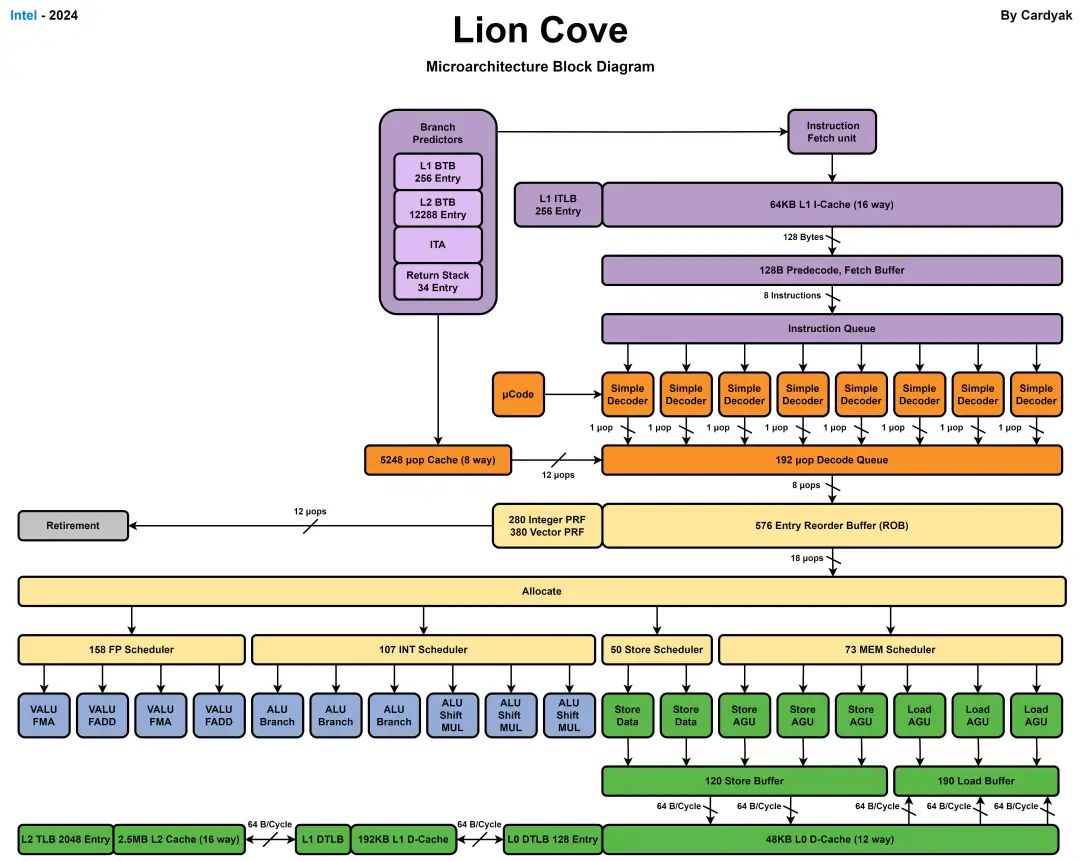

Intel Lion Cove

Intel 很少公开自己微架构的细节,并且已经多年被诟病为“牙膏厂”,这几年遭遇危机的 Intel 在今年推出了一款具备“改变的”性能核 Lion Cove,最重要的是做了一个违背祖宗的决定,取消了超线程。Decode 宽度为 8,Dispatch 宽度为 8,Issue 宽度 18,Retire 宽度为 12,执行端口为 18,ROB 为 576,L2 最高为 3MB。尽管 Intel 努力证明自己还在一线,但近 2 年 PC 核的负面新闻以及服务器份额被 AMD 超越可以说是雪上加霜,是时候大喊“Intel Yes”了。

AMD Zen5

就技术而言,这一代的 AMD 微架构是具备创意性的一代设计,尤其是前端的改变,采用双口 BTB 和 ICache,实现预测 2-taken/cycle。Decode 宽度 8,Dispatch 宽度 8,Issue 宽度 16,Retire 宽度 8,执行端口为 16,ROB 为 448,调度 entry 为 260。

AMD 手册中描述了 2 级的 BTB,并且 16K 的 L1 BTB 对一些分支可以 0 气泡定向,但奇怪的是,L1 MISS 而 L2 HIT 会有 8 个气泡,按照我朴素的理解是 L1 太大出于功耗的考量和 L2 没有并行访问,但即使这样,8 个气泡依然是很大,并且这句话似乎也有只有 L1 MISS 才会访问 L2 BTB 的意思。细节只能猜猜,对比下一代的 Zen6 也许可以获得更多信息,不过据外网的一些博主测试,AMD 的分支预测效果比较不错。

Apple M4P

亦安基本没有关注过 Apple 的微架构设计,但是它的设计处在领先水平是业界认可的。M4 的 ICache 是 192KB,这在微架构设计中不算很常见。Decode 宽度 10,Dispatch 宽度为 10,Issue 为 19,Retire 为 10,执行端口为 19。之前听说 Apple 的分支预测做的很特别,但没有搜集到很多的资料。

Qualcomm Oryon

高通的自研芯片,ICache 也是 192KB,挖的苹果的设计师。Decode 宽度 8,Dispatch 宽度 8,Issue 宽度 14,Retire 为 8,执行端口为 14。

总结

因为应用场景不同,架构差异,所以单纯的简单比较参数是不公平的,所以大家就横向看看就行,这些厂商基本能代表当前处理器核的一线水准,没有严重代差,设计水平都很高。后续亦安会收集一些资料分享一些处理器的微架构设计细节。

END

作者:亦安QAQ

文章来源:亦安的数据小站

推荐阅读

更多 IC 设计干货请关注IC 设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。