前文了解了LRU,对于LRU矩阵实现,由于矩阵的存在导致其所需要的资源会随着entry的增加而膨胀,今天来看下PLRU(tree-based Pseudo LRU)

✎ 编 者 按 凑巧看到一个有关LRU(Least Recently Used)的逻辑实现,其采用矩阵方式进行实现,看起来颇有意思,但文章中只写方法不说原理,遂来研究下。

✎ 编 者 按 最近收集一些代码覆盖率,其中牵涉到关于mem中streamReadSync的使用,在覆盖率收集过程中留意到其中具备的一些不可达的状态。

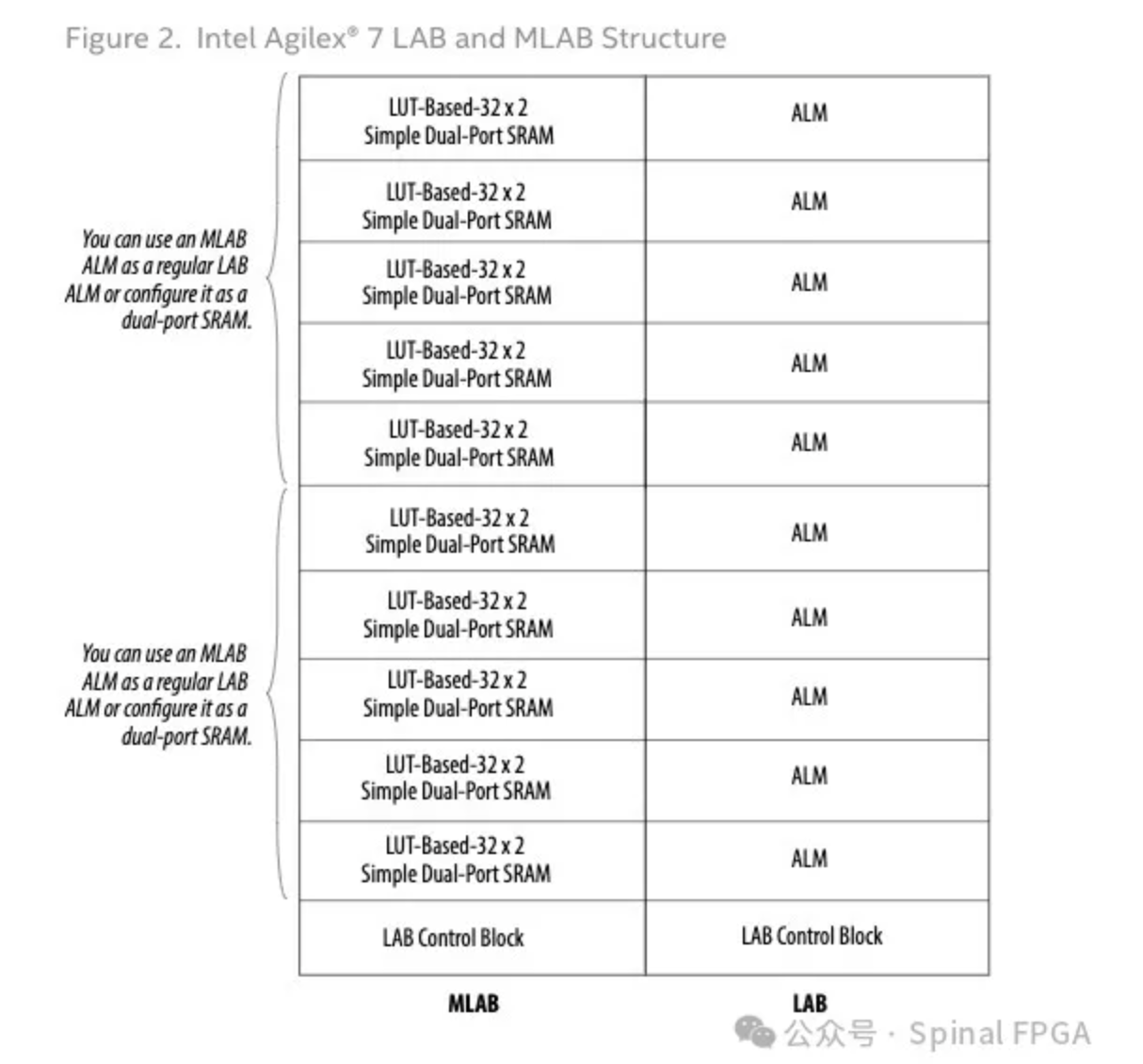

✎ 编 者 按 最近一些设计里需要极致的利用LUTRAM,借此总结下在Xilinx、Altera中LUT RAM的不同表现,一个“LUT”究竟能干哪些事儿。

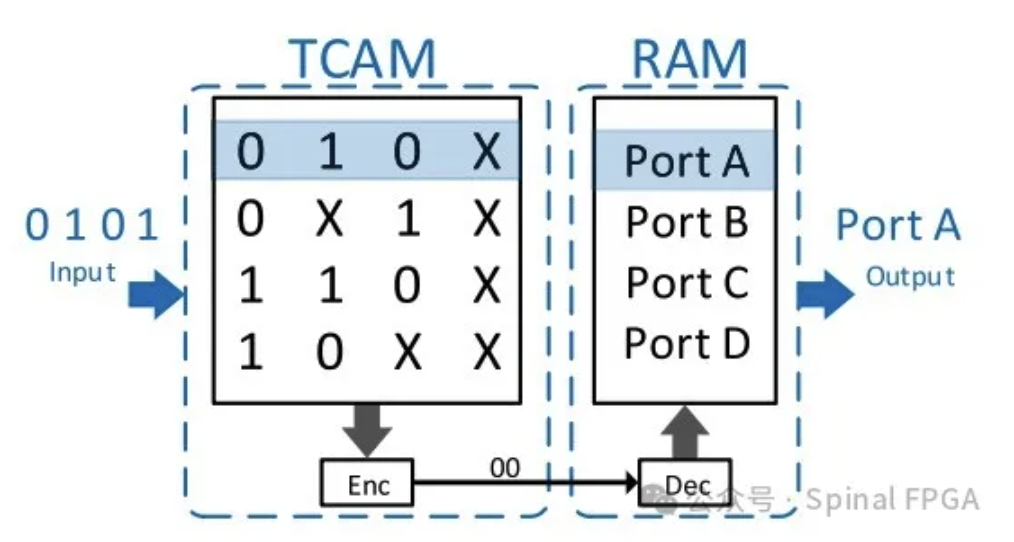

✎ 编 者 按 TCAM(Ternary content-addressable memory)在FPGA里并没有专门的资源,其在网络应用上是一个比较常见的资源。关于如何在FPGA中实现TCAM功能有不少的论文,在翻阅借鉴之后,本文就TCAM在FPGA上的最优化实现进行探讨。

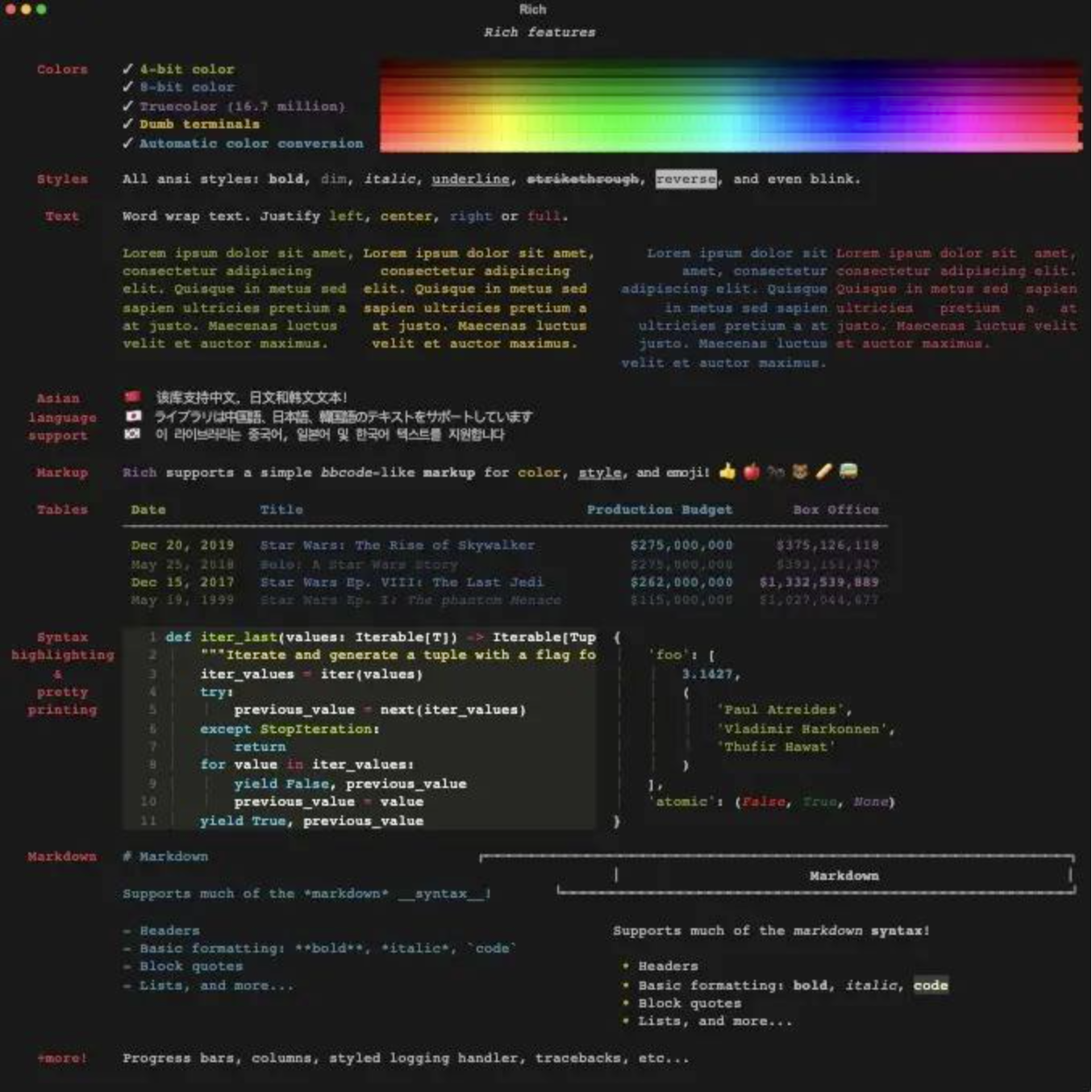

编 者 按 无论是FPGA还是ASIC,系统设计中总会存在配置寄存器总线的使用,我们会将各种功能、调试寄存器挂载在寄存器总线上使用。在SpinalHDL中,BusIf那套总线模型库写的还是相当不错的,能够同时生成对应的代码和文档(在公司里也做过一些修改,能够直接生成整个系统的寄存器文档而不仅仅是单个模块的寄存器文档)。今天...

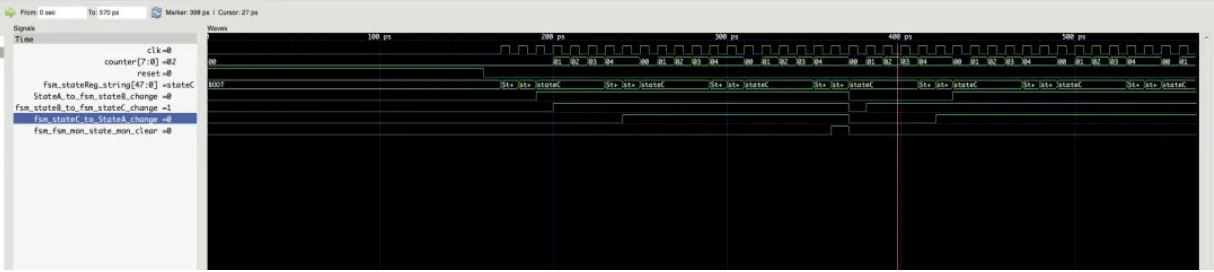

最近遇到一个关于状态机的问题,具体的业务就不讲了。关于FSM怎么写这种初级问题在这里也不讲了。这里我们只关注下在真实的应用场景里,从监控的角度来看,该如何去看待FSM。

✎ 编 者 按作为一个在数据中心搬砖的逻辑开发,日常不是仅仅简单的写写RTL就可以完事儿的。在数据中心,你可能连板卡都看不到,日常常打交道的,也就是PCIe。作为逻辑版本的生产者,出现问题往往需要自己有详细的定位手段和方式(没有谁比设计者更清楚逻辑的功能。专门的软件人员来做当然没问题,但增加沟通成本),那么一...

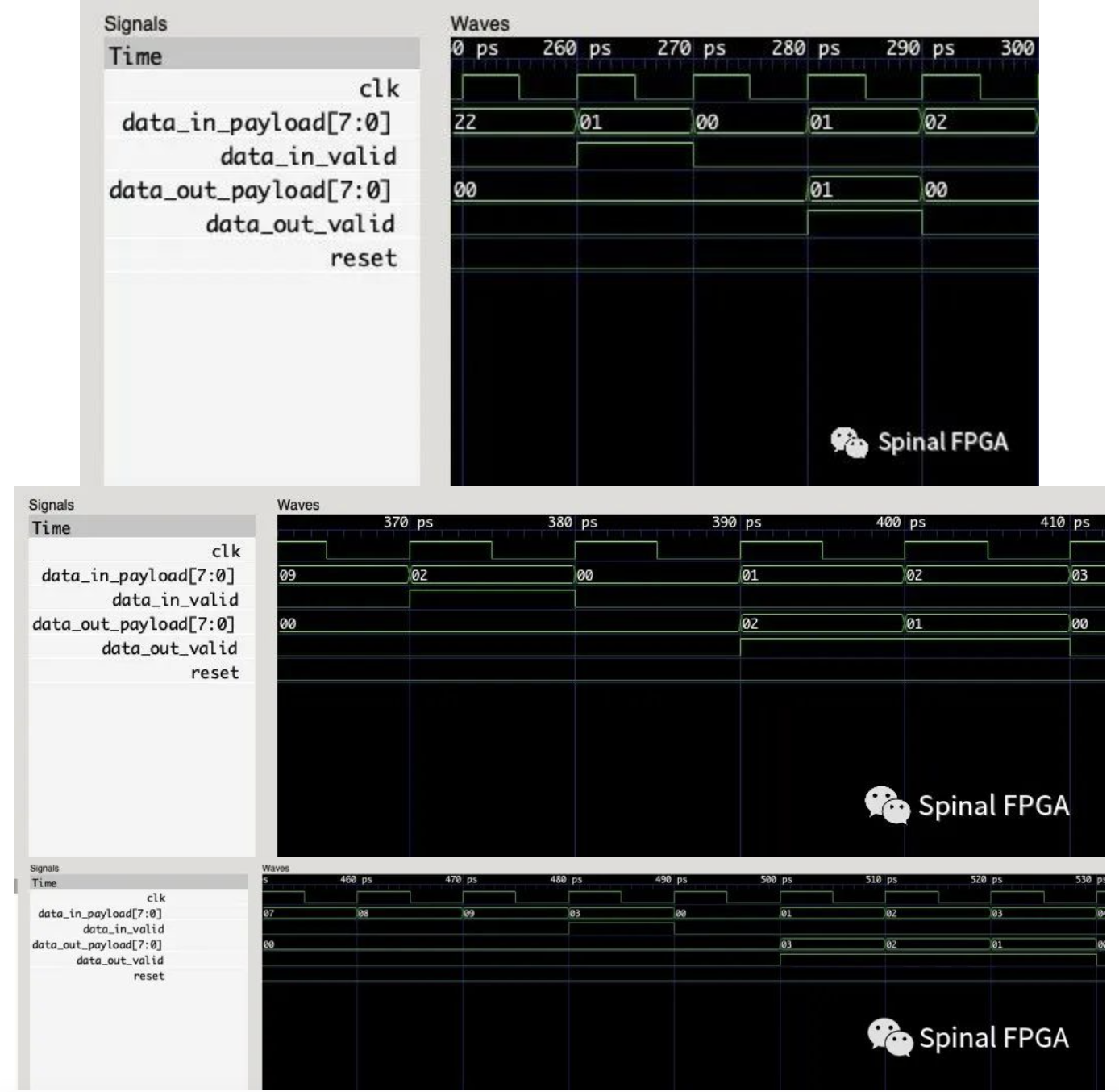

在SpinalHDL里在顶层一键优化代码中Stream/Flow代码生成的payload,fragment。

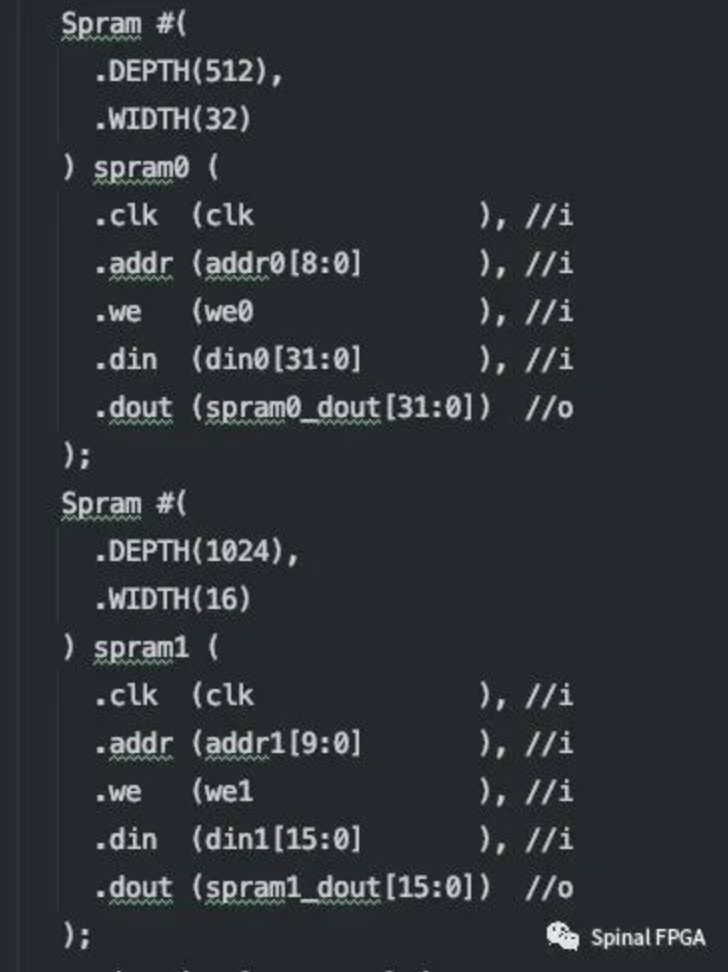

最近微信交流群里有小伙伴在讨论后端做memory时memory使用的大小不同例化时也需要使用不同的memory名称,这种情形往往采用BlackBox的形式来实现,来汇总下群里的结论,通过采用setblackname的形式来动态指定Blackbox模块名

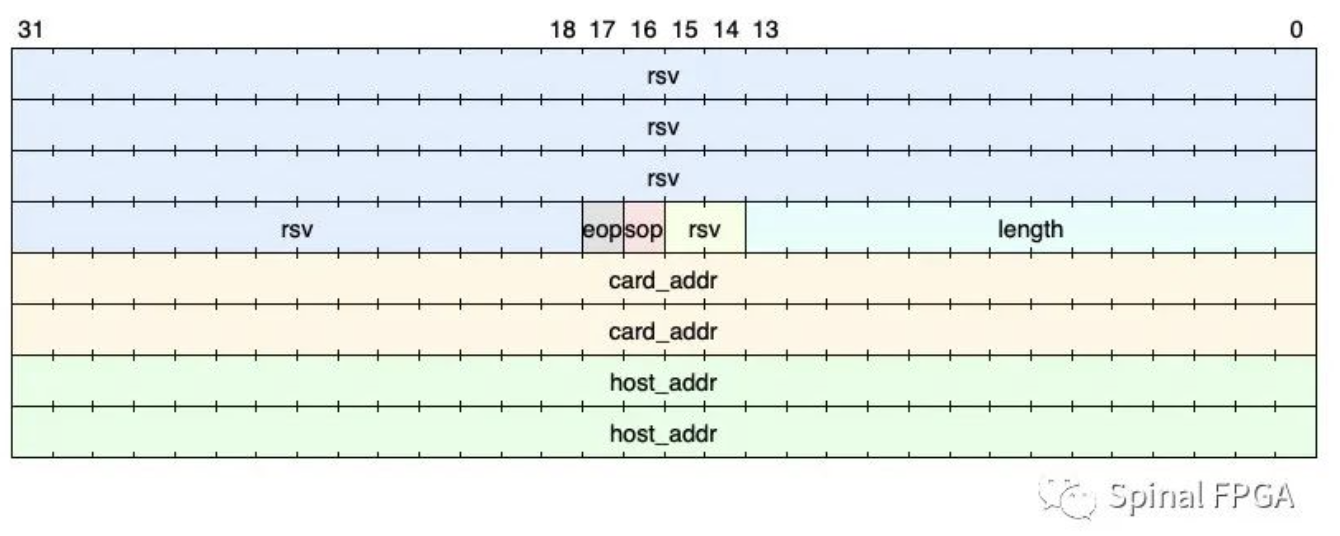

聊一聊SpinalHDL 1.9.4版本中的PackedBundle、PackedWordBundle的使用

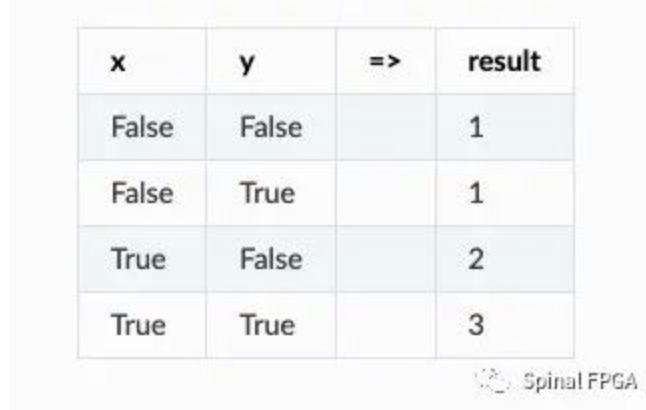

无论是SystemVerilog还是SpinalHDL,都有Last valid assignment wins的语法特征。如在SpinalHDL-Doc中所描述:

spawn的调用,最终会把触发条件cond存储至internals.request.spawns中去。

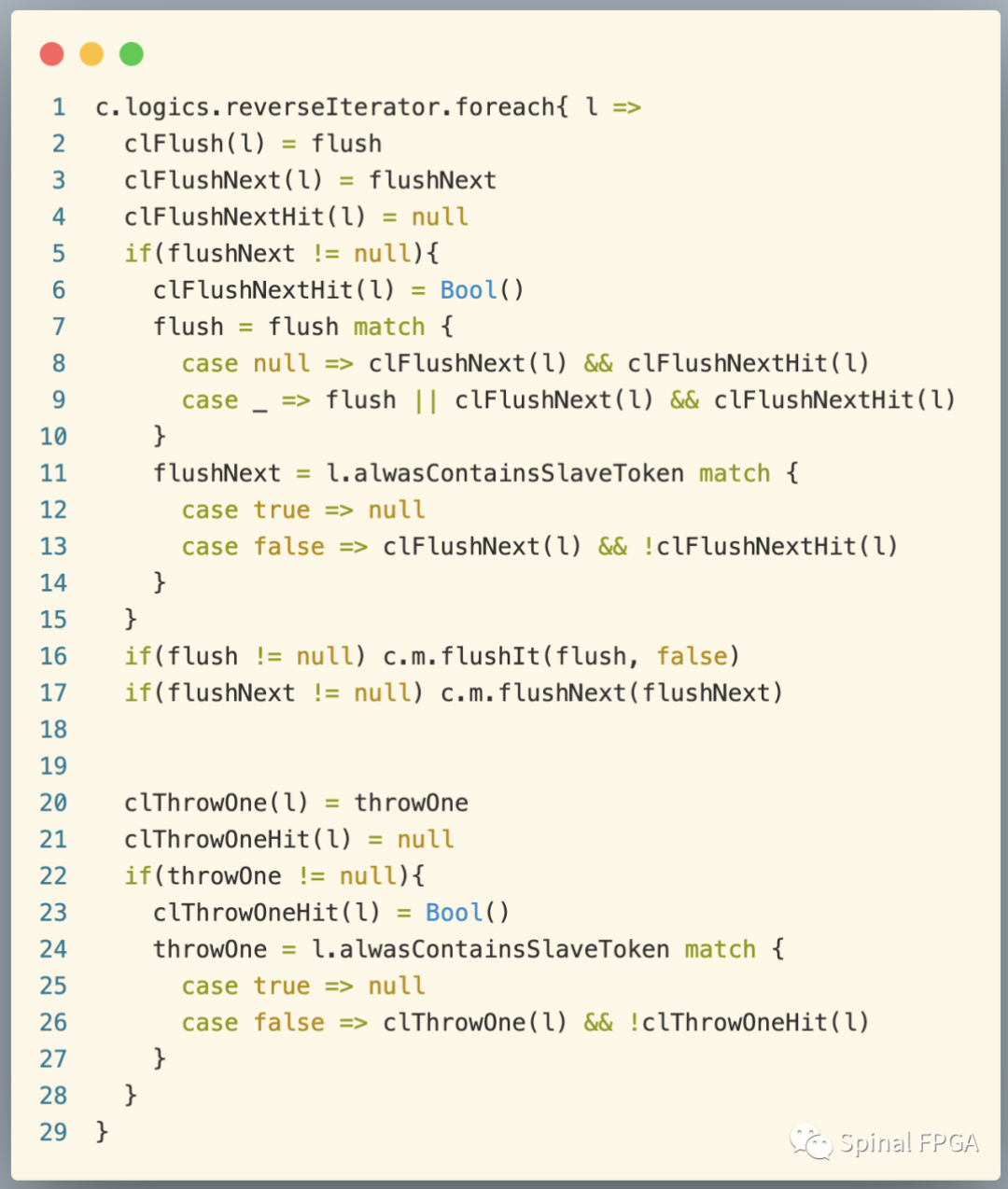

✎ 编 者 按 字如其名,来看下Pipeline中throwIt的用法,是怎么个丢弃方式API在Stage中,关于throwIt提供了下面的API: 函数中的动作出现了两个变量的使用:internal.request.throwsinternals.request.throwRoot那么去到Pipeline里面看都哪里使用到了它。在看之前,先再来回顾下在SpinalHDL中pipeline的编程模型:在Pipel...

✎ 编 者 按 来看下Pipeline中HaltIt的用法HaltIt看名字,就基本能猜到这个函数的大体功能是流水线暂停。 在Stage中,流水线暂停提供了这么几个API: {代码...} 三个API最终所实现的都是往internals.request.halts中添加cond条件。那么就看下request.halts在Pipeline构建时所起的作用。首先,在进行 connectionsWithoutSi...

调用flushNext,最终会将flushNext的需求暂存到internals.request.flushNext中。

可以看出,调用flush函数,会牵涉到internals.request中的fulsh以及flushRoot两个元素:

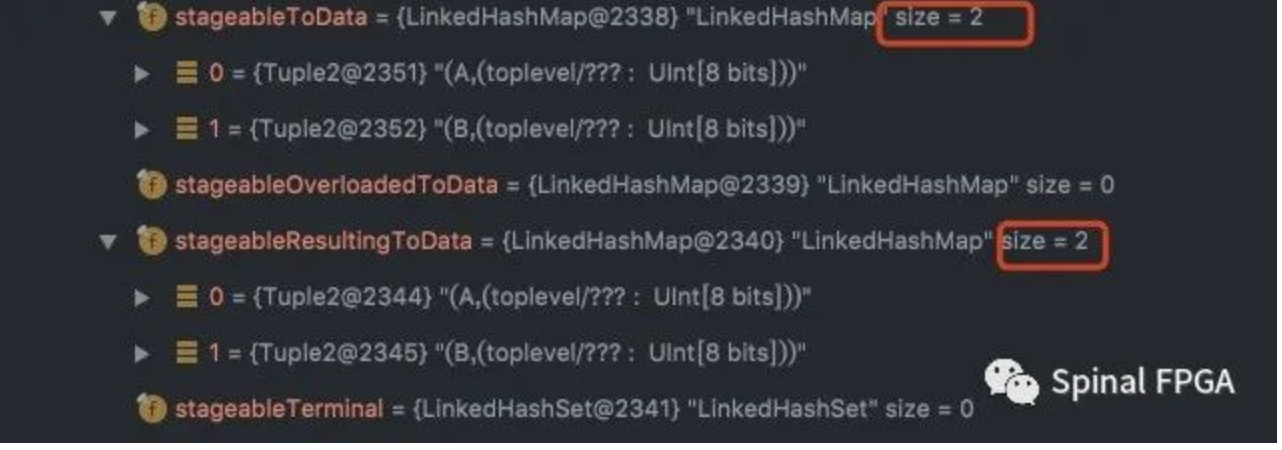

今天来看下SpinalHDL Pipeline组件里的resulting及overloaded的使用

看完了前面的系列,对于Stageable、StageableKey是如何起作用的应该有一定的了解。今天再来看下Stage中关于terminal的作用

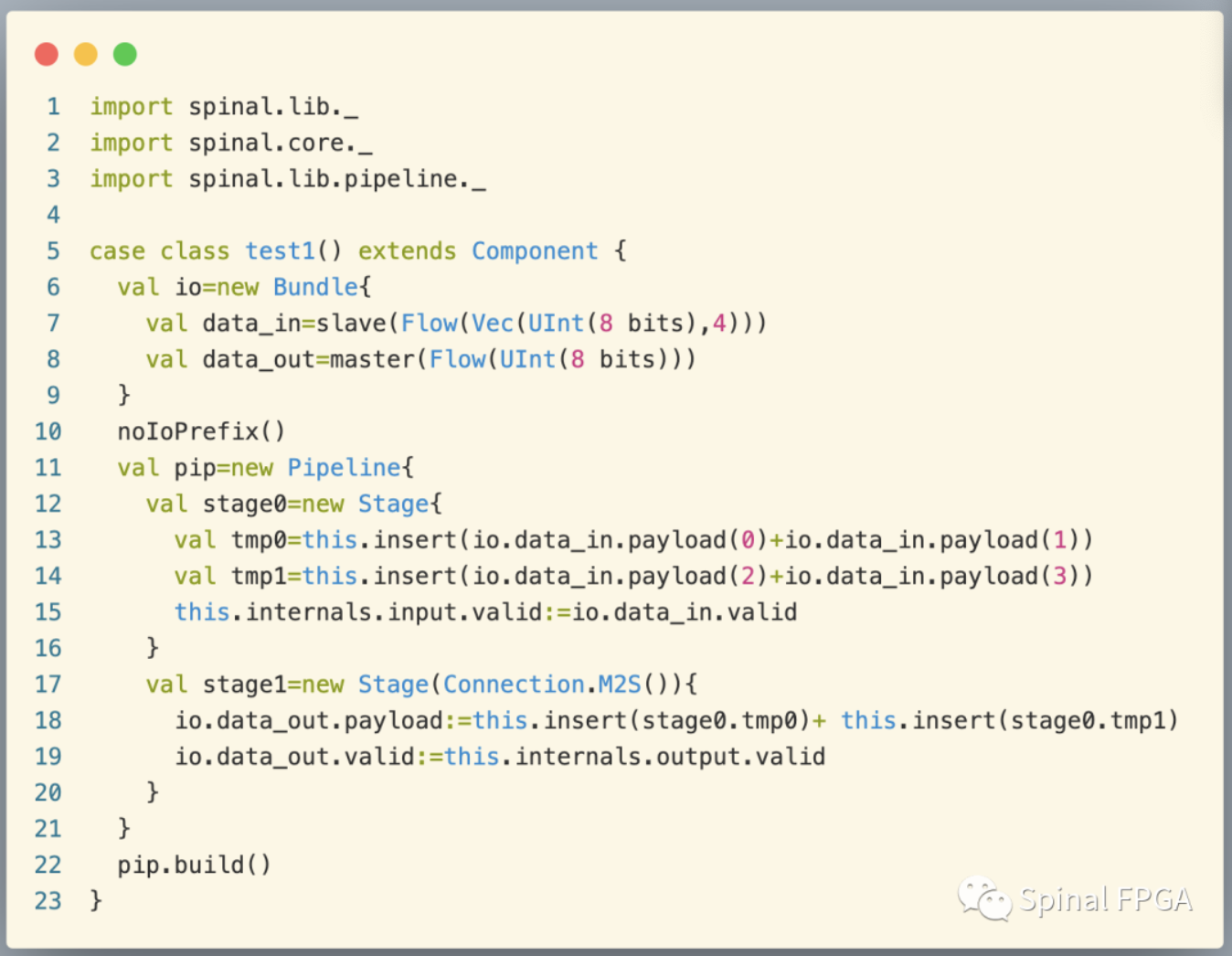

在pipeline的实现中,有五大要素:pipeline、Connection、Stage、StageableKey、Stageable。我们来看下面的代码: