✎ 编 者 按

最近一些设计里需要极致的利用LUTRAM,借此总结下在Xilinx、Altera中LUT RAM的不同表现,一个“LUT”究竟能干哪些事儿。

前言

当前无论是Altera还是Xilinx,FPGA里面的LUT资源主力配置无非还是6-input LUT。近段时间有个设计需要用到LUT RAM,如何减少LUT RAM的使用则需要结合器件的底层参数来衡量,不妨一块儿来看下。

Intel MLAB

在Intel的Agilex器件中,关于底层资源MLAB,有这样一段描述:

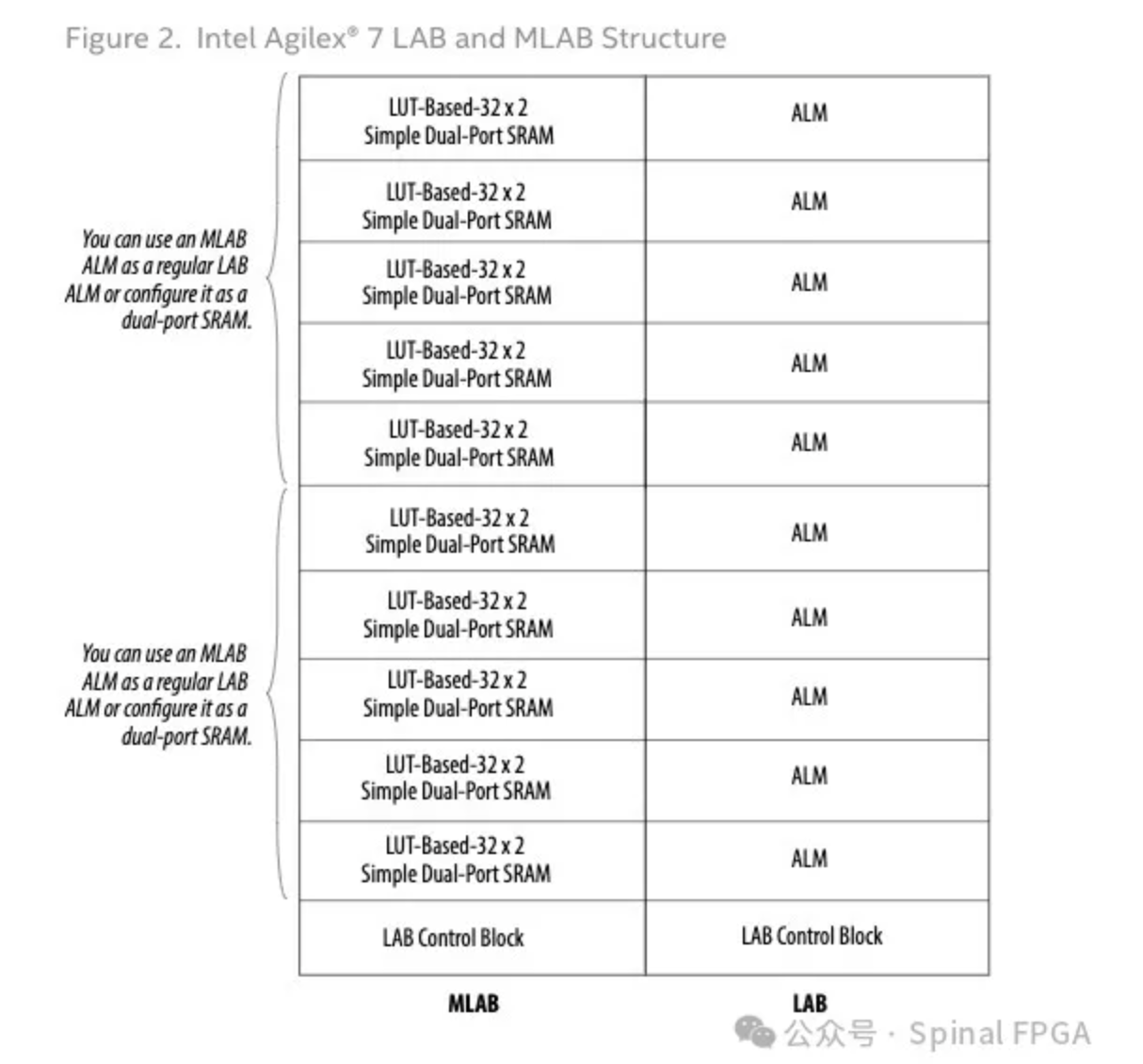

Each MLAB supports a maximum of 640 bits of simple dual-port SRAM. You can configure each ALM in an MLAB as a 32 (depth) x 2 (width) memory block, resulting in a configuration of 32 (depth) x 20 (width) simple dual-port SRAM block.

ALM作为FPGA上的基本单元,每个可以配置成一个32Dx2W的简单双端口RAM:

虽然在文档里面写明了每个LAM都可以作为一个32Dx2W的简单双端口RAM,但在真实的使用时你会发现,如果你在设计里例化使用了一个32Dx2W的简单双端口RAM,那么最终布局布线完成后Quartus报告显示消耗了10个ALM。而如果你例化成一个32Dx20W的简单双端口RAM,最终消耗的资源也为10个ALM。

在Agilex器件的使用中,如果作为分布式RAM,那么以MLAB为单位,最小的资源单位就是10个ALM。也就意味着32Dx(1~20)W所消耗的资源相同。一共640bit的存储单位,我们最大可以配置成为一个32Dx20W的简单双端口RAM,如果两拍输出一个结果,相当于一个16Dx40W的简单双端口RAM。

Xilinx CLB

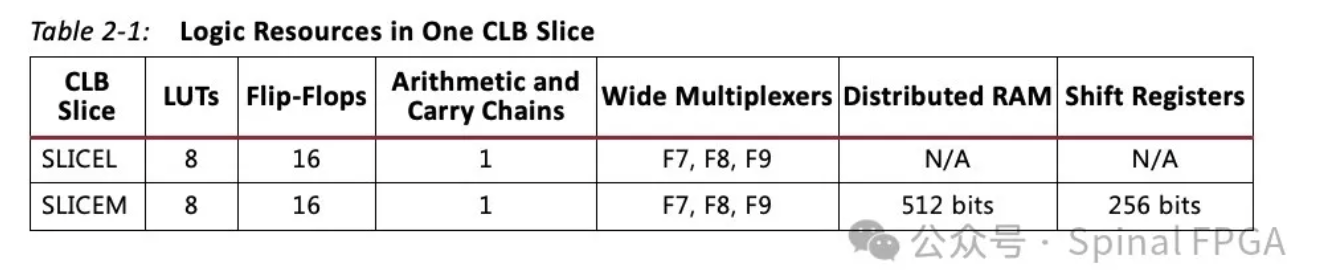

在Xilinx UltraScale系列器件中,一个基本的UltraScale CLB所能包含的资源如下:

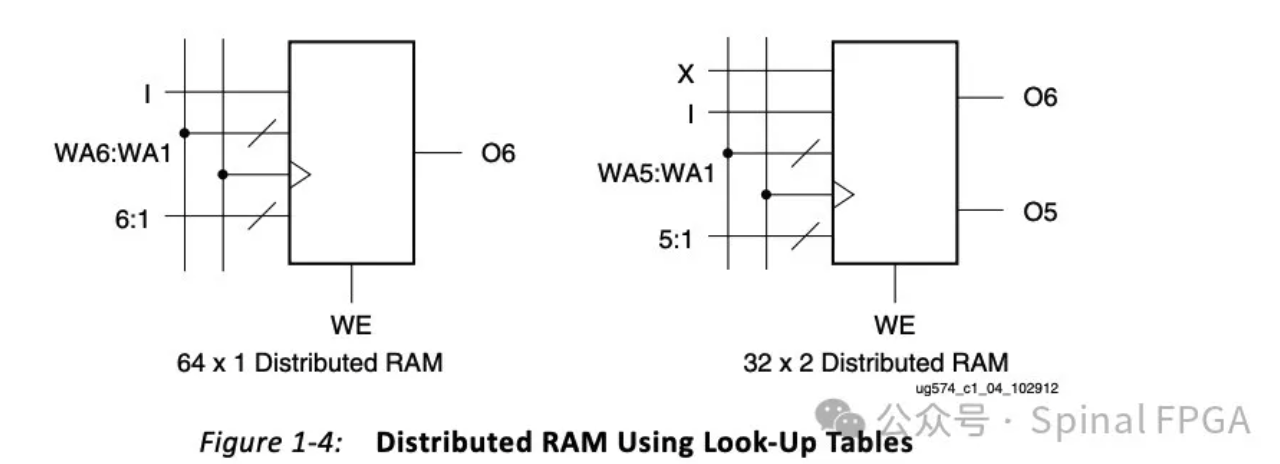

SLICEM可以作为分布式RAM。在使用 LUT来构建分布式RAM时,其支持两种配置模式:

即可以配置成一个64Dx1W或者32Dx2W两种模式。只不过相相较于Intel的简单双端口,在Xilinx上仅能设置成一个单端口RAM。即一个LUT可以配置成一个64Dx1W或者32Dx2W单端口RAM。那么在一个CLB(SLICEM)中,其所支持的就有两种模式:64Dx8W或者32Dx16W模式,如果两拍输出一个,那么可以配置成16Dx32W单端口RAM。当读端口采用寄存器输出时,32Dx16W正好可以将一个SLICEM中的LUT资源和寄存器资源全部给利用起来。

小结

就所能使用的资源形式来看,两家厂商趋同一致,只是配置形式略有不同。Altera能够支持简单双端口,而Xilinx则只能采用单端口以实现资源利用的最大化。

☆ END ☆

作者:玉骐

原文链接:Spinal FPGA

微信公众号:

推荐阅读

更多SpinalHDL技术干货请关注[Spinal FPGA]欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。