最近,CF中某些主播“开(下称KG)挂”升上热搜,作为十年老兵,瓜是吃的饱饱的。之后官方下场进行检测,但是没有检测到软件KG行为,而是检测到主播有硬件设备异常情况。关于事件的来龙去脉就不过多赘述了,大家可以去某些社区吃瓜,我们今天只谈技术,不吃瓜。

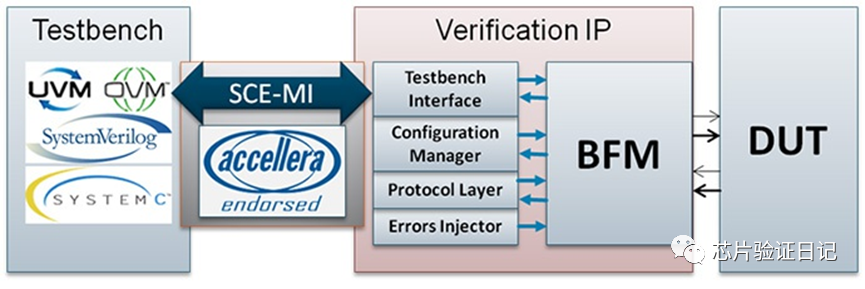

当今的SoC芯片,普遍包含大量的工业标准接口同外围设备相连。 在验证设计过程中,这些接口被用于和测试testbench相连接。这些沟通桥梁,被称为 Verification IP (VIP) 的模块实现。Verification IP (VIP) 是一种特殊的IP Core。它将一个接口的BFM 和 Test Harness features 结合在一起。VIP在芯片验证中的应用场景众多,...

之前在github([链接])上整理了一些开源的芯片类的项目,收获了很多人的点赞。这里再次拿出来分享给大家一起学习,共同进步,也欢迎大家到github上点star,或者有好的项目也欢迎提PR。

《优秀的IC/FPGA开源项目》是新开的系列,旨在介绍单一项目,会比《优秀的 Verilog/FPGA开源项目》内容介绍更加详细,包括但不限于综合、上板测试等。两者相辅相成,互补互充~

发现Bug,发现所有的Bug,或者证明没有Bug,是验证存在的唯一目的。无论任何验证语言、任何验证环境、任何验证方法学、任何FeatureList,都是为了达成这一目的而使用的方法,或者说手段。

总线结构及互连设计直接影响芯片总体性能发挥,选用成熟的总线架构有利于SoC整体性能提升。对于系列化或综合性能要求高的SoC设计,就需要深入进行系统架构研究和优化,将总线频率和带宽提升到更高水平。目前SoC总线主要分成IP授权和开源两大类,主流商用总线选用ARM的AMBA系列、片上网络NoC总线、wishbone总线等。构建深...

最近,讨论芯片行业的文章多了起来。看来,很多人已经觉察到了风向的变化。这里梳理一下近期的消息。投资人对半导体初创公司已经非常谨慎。创业者,去年融资,很多人抢着投资。如今却到处找投资人。甚至可以平轮。上市半导体企业,大量出现破发现象。迹象表明,依靠大量投入,然后上市套现这条路已经难以为继。市场层面...

由技术大牛John Marsh所著,Arm公司出版的《Arm Helium Technology M-Profile Vector Extension (MVE) for Arm Cortex-M Processors Reference Book》要翻译成中文版啦,现在诚挚招募相关专家进行翻译合作,欢迎感兴趣的人联系哈~

在描述组合逻辑的RTL时,必须遵循编码和设计指南。设计和编码指南将提高设计性能、可读性和可重用性。本文讨论组合逻辑设计的规范和编码准则。

市场调研机构IDC的全球半导体研究副总裁Mario Morales撰文指出,随着产能的加速扩张,芯片短缺将在2021年第四季度持续缓解,2022年中达到平衡,2023年可能出现产能过剩。

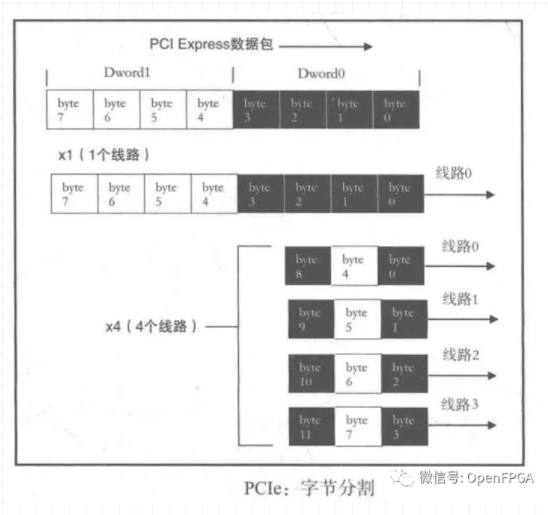

PCIe使用链路和线路来发送串行数据。链路是一个逻辑实体,能够具有单个线路或多个线路。当逻辑链路包括一个线路时,TLP和DLLP通过单一的线路发送,每次发送一字节。当链路包括多个线路时,TLP和DLLP分布在多个线路中,此时不是在不同的线路中发送不同的TLP而是所有的线路共同发送TLP在一个x4 PCIe链路(拥有4条线路)中...

用SpinalHDL提升生产力

遥想当年本科之时画过电路PCB、玩儿过单片机、PLC,亦学过C#(给我那数块板子的毕设做个上位机),Python。直到研究生之时方才选择FPGA这条道路,除了对数字电路本身的兴趣之外(对于做软件感觉一直找不到自己的优势所在,虽然最终还是进了互联网行业,也算是冥冥之中自有天意吧),重要的便是Verilog语法简单,可以令我很快...

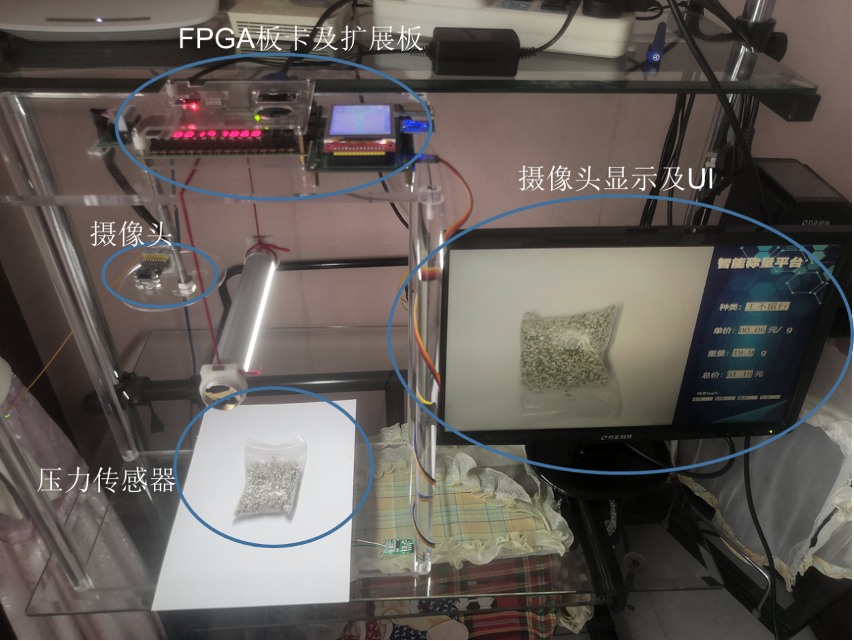

本作品参与极术社区组织的有奖征集|秀出你的集创赛作品风采,免费电子产品等你拿~活动。杯赛题目:Diligent杯:基于FPGA开源软核的硬件加速智能平台参赛组别:A组设计任务:利用业界主流软核处理器(仅限于Cortex-M系列及 RISC-V系列)在限定的DIGILENT官方FPGA平台上构建SoC片上系统,在 SoC中添加面向智能应用的硬件加速...

PCI总线是一条共享总线,在一条PCI总线上可以挂接多个PCI设备。这些PCI设备通过一系列信号与PCI总线相连,这些信号由地址/数据信号、控制信号、仲裁信号、中断信号等多种信号组成。

基于Arm技术竞赛作品的分享,欢迎交流~

2020年第四届全国大学生集成电路创新创业大赛自开赛以来,共有来自全国七大赛区的141支队伍报名“Arm杯”赛题,经过企业评审和分赛区初赛,有21支团队晋级全国总决赛。经过现场演示和评审,“Arm杯”赛产生了一等奖2名、二等奖5名、三等奖8名、优秀奖6名,此外,一等奖团队中的“起名好难队”脱颖而出,获得了“Arm杯”企业专项...

驭势资本是一家以研究驱动的硬科技精品投资银行,深耕集成电路、5G、物联网、数据智能和汽车科技领域,为顶尖的科技创业者提供专业资本服务。

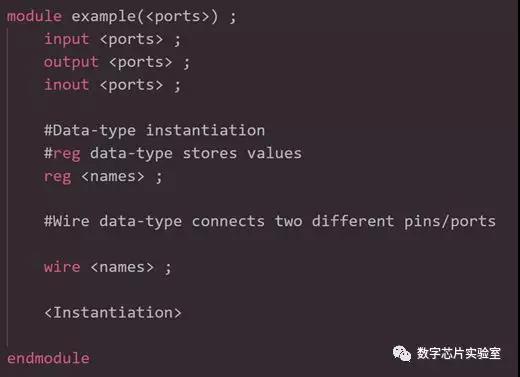

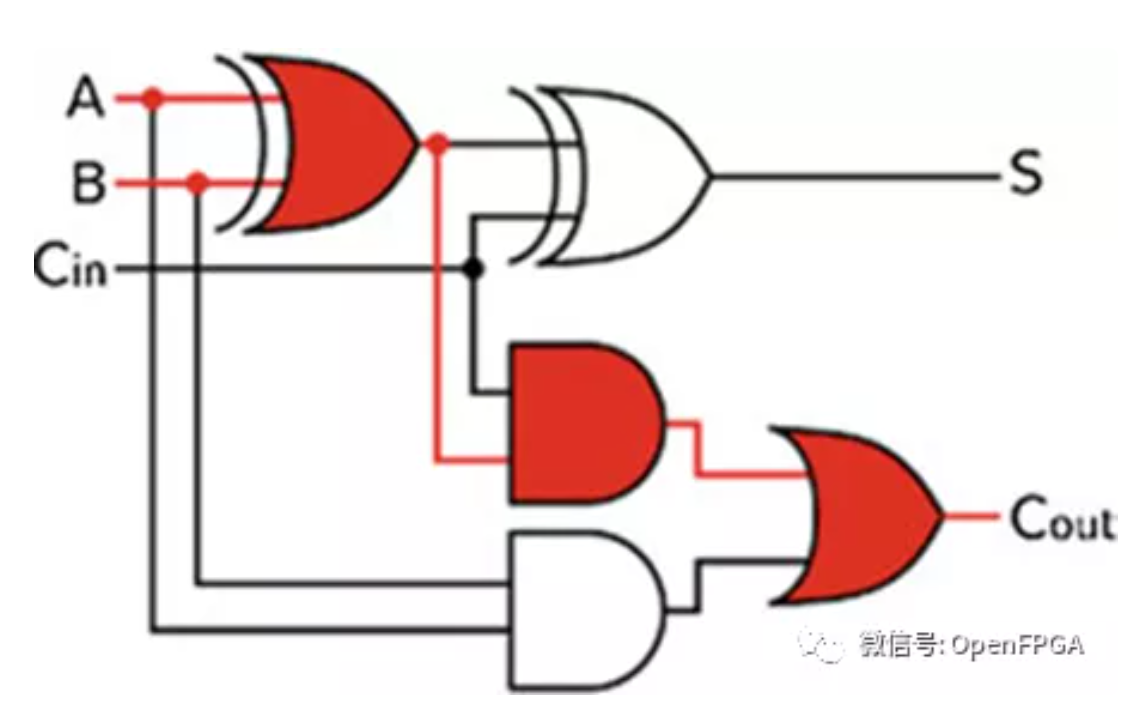

在数字系统设计中,有一些重要的设计级别概念:•行为级(Behavior Level):通过行为级算法描述数字系统。•寄存器传输级(Register Transfer Level):在寄存器传输级,通过寄存器之间的数据传输进行电路功能设计, 例如有限状态机。•门级(Gate level):数字系统按门级(AND,OR,NOT,NAND等等…)描述。通常不会进行...