Contents

• This guide is designed to show benefits of working with Arm based technology

• The intended audience is SiPs and OEMs

Arm and Our Partners

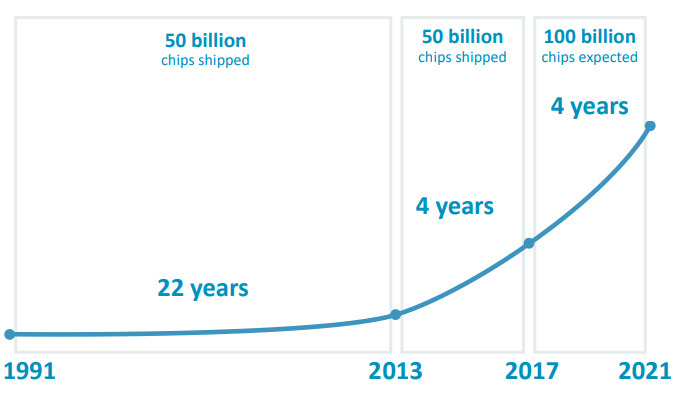

Transforming the way people live and businesses operate

• Arm and its global ecosystem of technology

innovators empower the world’s most

successful business and consumer brands,

powering mobile, IoT, automotive and more

• Arm and our partners are driving growth

towards a world of a trillion connected devices

• Arm has a partnership-based culture and

business model, driving innovation wherever

compute is happening from the device to the

cloud

The Architects of Global Possibilities

Fuelling our partners innovation

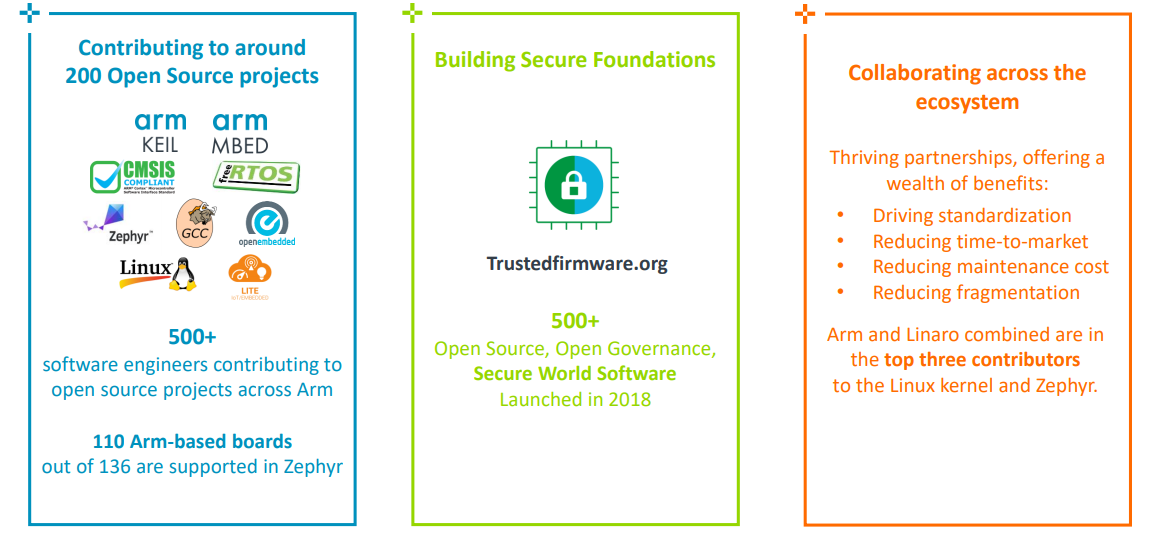

Arm is Committed to Open Source Innovation

Open Collaboration with Governance

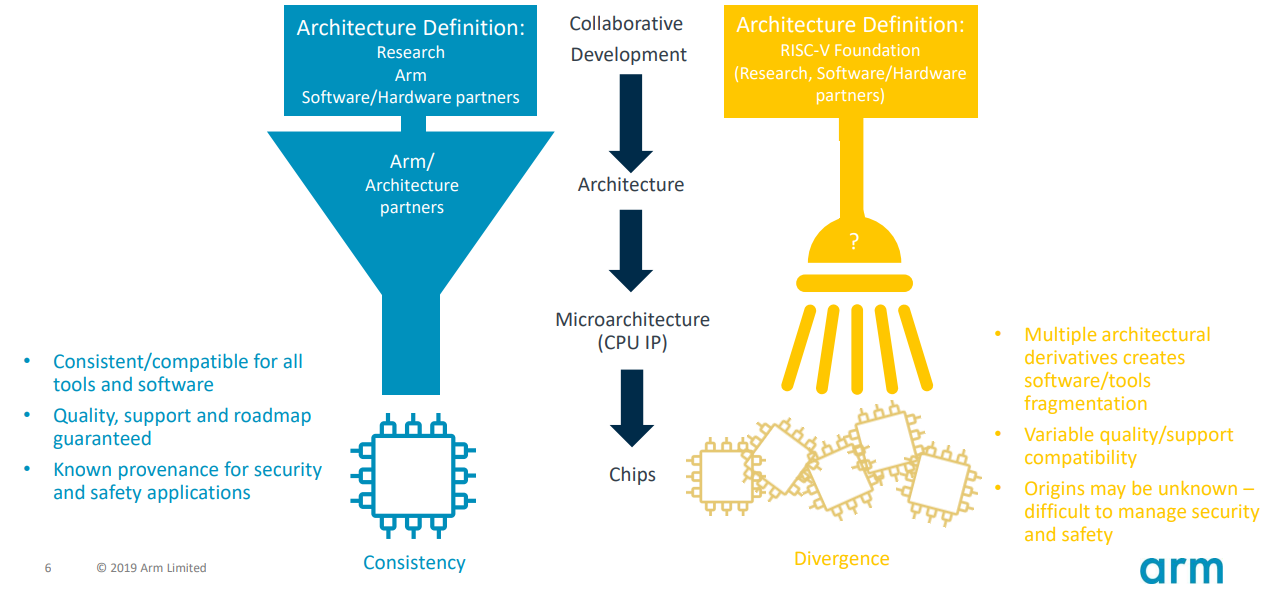

What do we Mean by “Fragmentation”

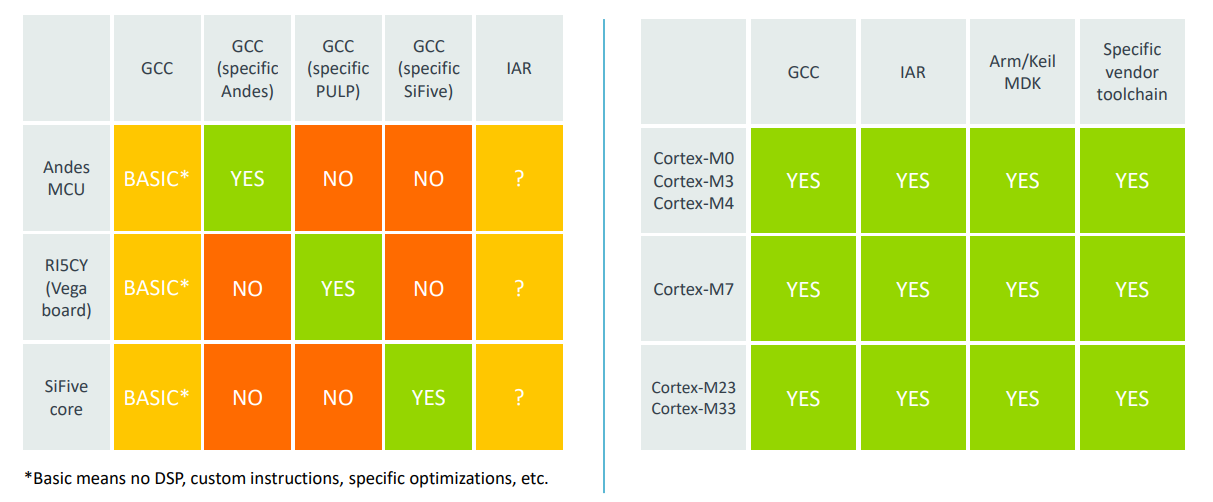

• Instruction set compatibility allows portability and reuse of code

• So long as the processors implement the same instruction set

– i.e. code written for Armv8-M processors is portable between different implementations of that instruction set

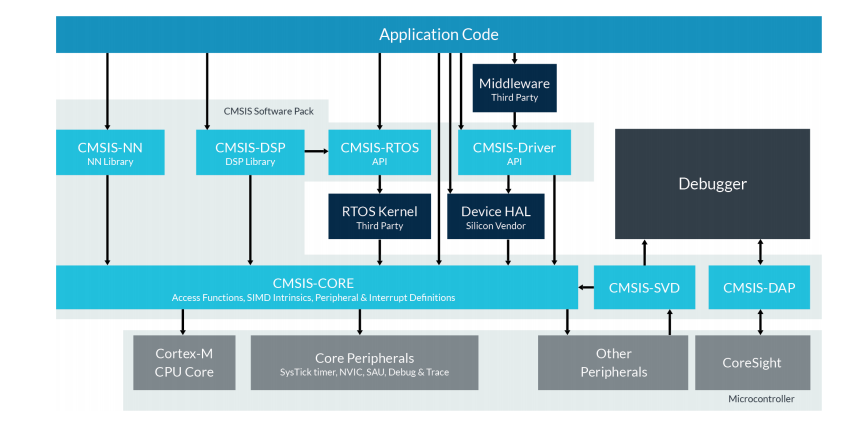

– CMSIS libraries improve abstraction across peripherals, RTOS etc

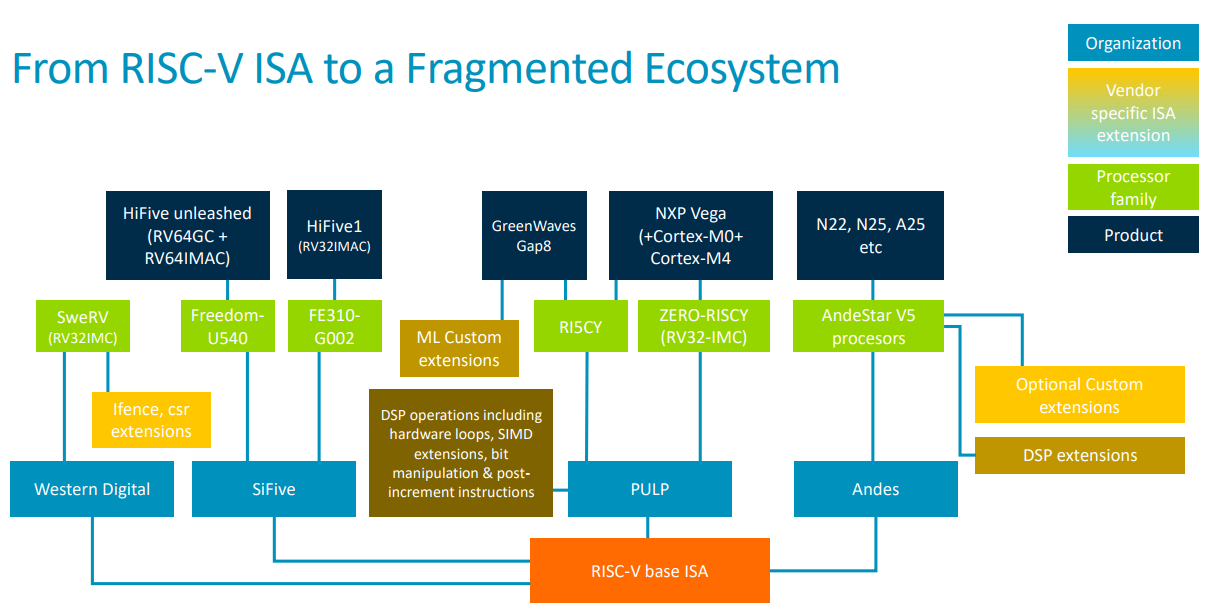

• RISC-V implementations encompasses many variations of the base ISA

• From floating point to atomics to multiplication to SIMD, vector and hypervisor as standard extensions

plus potentially many individual custom extensions

• Only the base instruction set is formally ratified

• Andes latest DSP extensions are incompatible with RISC-V ‘P’ specification

• Incompatibilities may require recompilation of code, or even different toolchains

• GCC for PULP family (including NXP VEGA) is incompatible with SiFive, SweRV, Rocket cores, despite all

being RISC-V implementations

From RISC-V ISA to a Fragmented Ecosystem

What Fragmentation Means

Supporting multiple forks is expensive and supporting all of them may not be possible

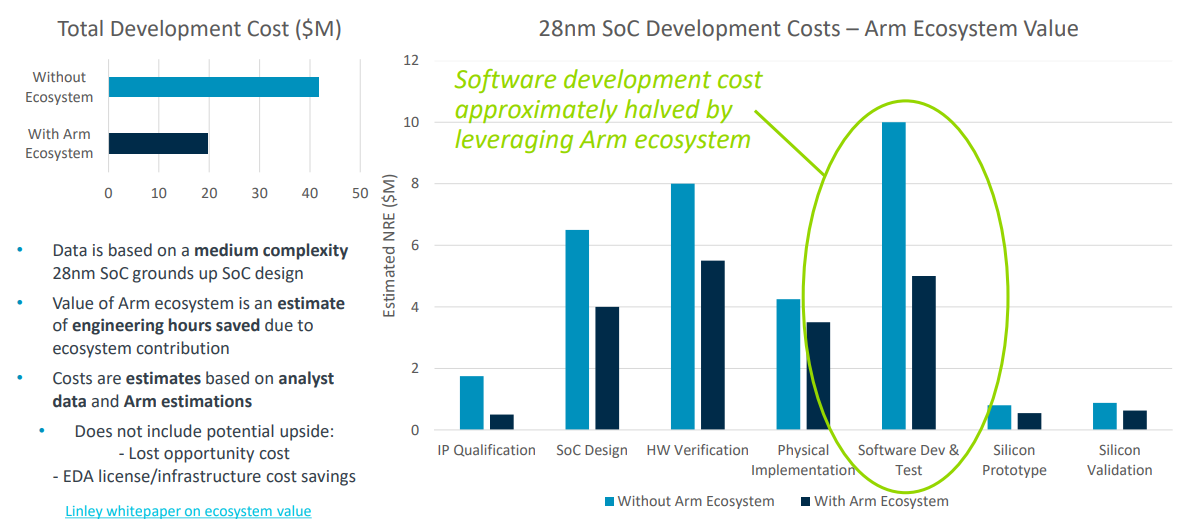

The Arm Ecosystem – Reducing Development Cost

CMSIS - Cortex Microcontroller Software Interface Standard

CMSIS enables consistent device support and simple software interfaces to the processor

and its peripherals, simplifying software reuse, reducing the learning curve for

microcontroller developers, and reducing the time to market for new devices.

Benchmarks Don’t Tell the Full Story

The wider picture

• Ease of development, availability of tools and

software libraries

• Does it reflect your application accurately?

• Is the score from a processor configuration you

will actually use?

Features that matter, but may not be in a

benchmark score

• Context switching, interrupt latencies, MPU

configuration

• Small MCU benchmarks such as Coremark and

Dhrystone won’t measure system performance

on a complex Cortex-A SoC

• Code size may be more important than

performance

• Only a few benchmarks consider energy

efficiency – eg EEMBC ULPMark

https://www.eembc.org/ulpmark/

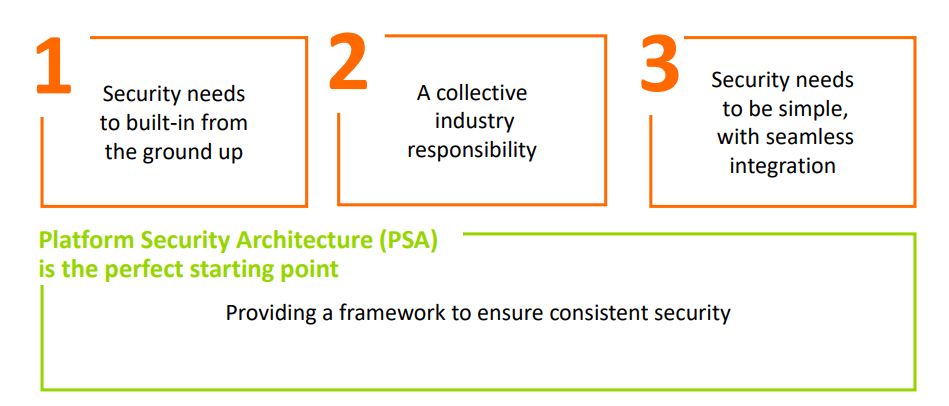

Arm’s Vision for IoT Security

A holistic approach from design to product

https://www.arm.com/why-arm/architecture/platform-security-architecture/

Recent Industry Observations

https://semiengineering.com/open-source-processors-fact-or-fiction/

• “When you buy a core from the likes of an Arm, you know it is going to be an Arm

and you know it is going to work… The amount of verification that has to be done in

the average SoC project is probably 10X if they use an open ISA compared to buying

a standard off-the-shelf part.” Simon Davidmann, chief executive officer for Imperas

• “With open source, there is a danger of hardware Trojans or unintended behavior

sneaking into the design.” - Raik Brinkmann, president and CEO for OneSpin solutions

• “A standard, robust golden test suite to make sure your RISC-V implementation is

compliant does not exist yet,” Jerry Ardizzone, VP of worldwide sales for Codasip

• “It may run the compliance suite, but that does not mean it is a fully verified core,” -

Neil Hand, director of marketing at Mentor, a Siemens Business

Conclusion

Scalable solutions

• Arm’s architecture scales

with your product line,

allowing you to re-use your

software.

• Fastest time to market

• Lowest total cost of

ownership (reduced

software development time)

• Choice and availability of

tools, libraries, software,

developers, documentation,

support, etc.

Many choices available

• Arm’s mature ecosystem

consists of many choices for

silicon, tools, software, and

models that are proven and

prolific

• Arm has a strong

commitment to open source

with over 500 software

engineers regularly

contributing, with Arm and

Linaro being in the top 3

contributors to the Linux

kernel

Lowest risk

• Arm has a proven history in

the marketplace shipping

over 138Bn units.

• Arm is the low risk solution

• The Arm instruction set is

governed, evolving over time

to continue to meet the

needs of industry while

recognizing the value in not

allowing arbitrary extensions

| 文件名 | 大小 | 下载次数 | 操作 |

|---|---|---|---|

| Arm value guide for OEMs_public.pdf | 913.91KB | 1 | 下载 |