本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

如果把 AMBA 看做一个大家族,那可老热闹了。

AMBA协议家族中有 AHB APB 这些用于 processor 的总线,他们一般很高冷,和我们 FPGA 的 ip 核们很少打交道。还有我们之前讨论的标准 AXI4 总线,另外还有 AXI4-Lite 协议,这是 AXI4 的弟弟;

还有 AXI4-Stream 协议,这也是 AXI4 的弟弟。

还有一位 ACE 协议,就是题图里和 AXI4 在一起的那位,我们将在以后的系列中再讨论。(实际上我没用过,也还不怎么知道这个 ACE 来着)

AXI4-Lite

说起来同样是弟弟,AXI4-Lite (为了方便,以下简称 Lite)应该算是亲弟,AXI4-Stream (Stream)那只能算表弟了,因为 AXI4-S 和他们没住在一本 specification 里。

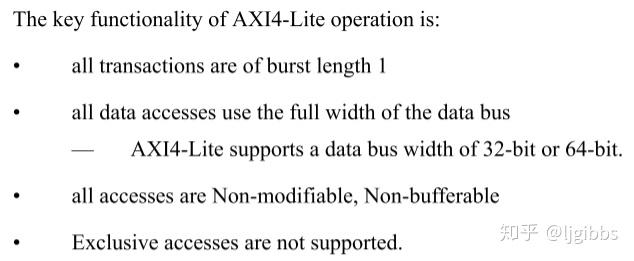

先介绍下 AXI4-L ,用通俗的说法,Lite 是标准 AXI4 协议被砍了几刀的结果。相比 AXI4 ,Lite 有以下不同:

- 突发传输长度固定为 1(说人话:不支持突发传输)

- 数据位宽固定为 32 位或者 64 位(说人话:不支持除此之外的位宽,也不支持在宽通道上传输比通道宽度窄的数据,每次传输必须使用 full width )

- 不支持原子操作属性以及缓存操作属性(说人话:砍了)

- 不支持多端传输下的独占操作(说人话:砍了)

speak in English

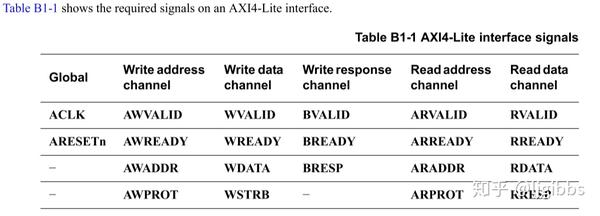

那这样砍了 4 刀之后的 Lite 就很清爽了,信号数量一下子变得很少:

群众:嗯,砍起来很爽,你这刀怕不是从微软借的,砍了之后也是很清爽,信号少了之后确实省了不少事,但这个性能还能保证么?

放心,这个性能自然是。。下降不少的,灵活性也失去大半。

但性能要根据使用场景来看。AXI4-Lite 的使用场景主要用于寄存器的配置,这也就是为什么数据通道的宽度被设置为 32 位或者 64 位了。(小问题:请问是为什么呢?)

配置寄存器这类操作的特点有:

- 相比数据读写,数据量很小并且固定;

- 一般对某个寄存器进行配置,一般不会对连续地址上的一串寄存器进行配置,也就没有突发传输的必要了;

- 一般不会有多个逻辑同时对一个寄存器进行配置,也就没有必要对地址进行保护了;

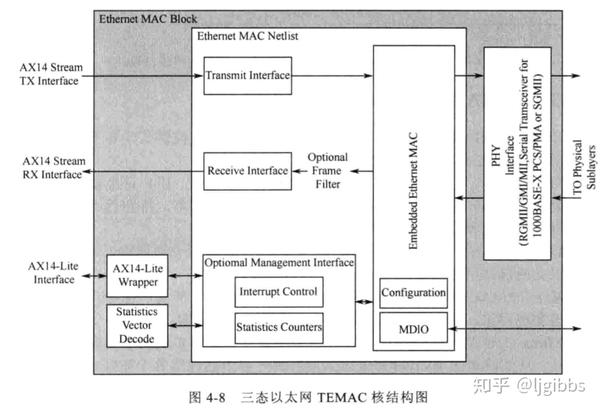

所以说啊,ARM 可谓刀刀砍得有来头,这样一来一个精简的,适用于寄存器读写配置的协议就诞生了。在很多 ip 核中都可以看到 Lite 和标准 AXI4 协议,以及我们接下来要说的 AXI-Stream 协议,一起工作的身影。

比如这个 MAC 核,就可以同时看到二者

AXI4-Stream

之前也说了 Stream 住在另一本 specification 上:

独门独院,很舒服。

之前也说 AXI4-Lite 被砍的悲惨遭遇,其实 AXI4-Stream 被砍得尤其惨,不过与此同时也在另一方面得到了补强。

首先 AXI4-Stream 砍去了地址概念,Stream 将不再是一种 address mapped 的协议,而是一种点对点(或者一点对多点)数据流通信的协议。打个比方, AXI4 适合访问诸如 RAM 等有地址概念的存储介质,而 Stream 协议则适合访问诸如 FIFO 这样没有地址概念的存储介质。

没有了地址概念,自然也没有突发传输的概念。所有的数据都是点对点(点对多点)传输,可以理解为始终不断地对一个地址读写(或者是多个接收端设备各自的固定接收地址)。

在去除地址概念后,Stream 协议主要面向高速的,大数据量的数据流传输,在今天的异构系统的数据传输中起着非常重要的作用,比如 Xilinx 的嵌入式系统 Zynq 中,Stream 总线是一项基础设施。

AXI4-Stream 的基本信号机制与 AXI4 相同,比如握手机制。但为了适应面向数据流的传输,做了很多改变。

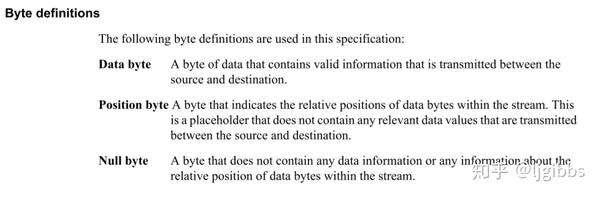

首先,作为一种面向数据流的协议,不存在专门传输控制信息的通道,但为了在数据流中传输部分控制信息,需要在数据中插入一些控制信息字节。所以 Stream 协议的字节分为三种类型:数据,位置字节以及空字节

数据类型自然就纯粹是传输的数据,位置字节不包含有效的数据,只指出当前数据在数据流中的相对位置。空字节不包含任何信息。

在数据流传输中,通过两个信号:tkeep,tstrb 的高低电平表示当前传输的字节类型。

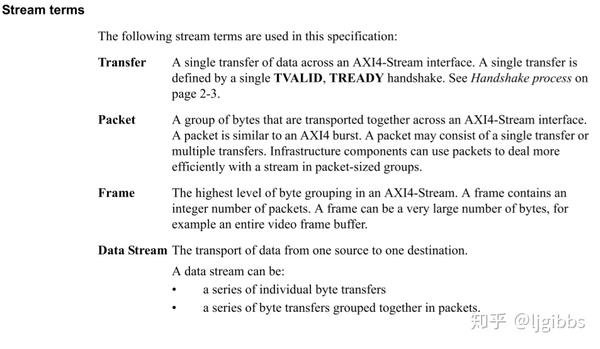

同 AXI4 中的 transfer 以及 burst 的组织形式不同,Stream 协议定义了四类传输。

transfer 的概念与 AXI4 中的同名概念完全相同,以一次 TREADY,TVALID 握手表示一次传输,每次 transfer 的数据传输量一般为数据总线的宽度。

packet 是 Stream 中的新概念,类似 burst ,包含一个或多个 transfer。

frame 是 Stream 中最高层次的传输组织形式,包含整数个 packet。

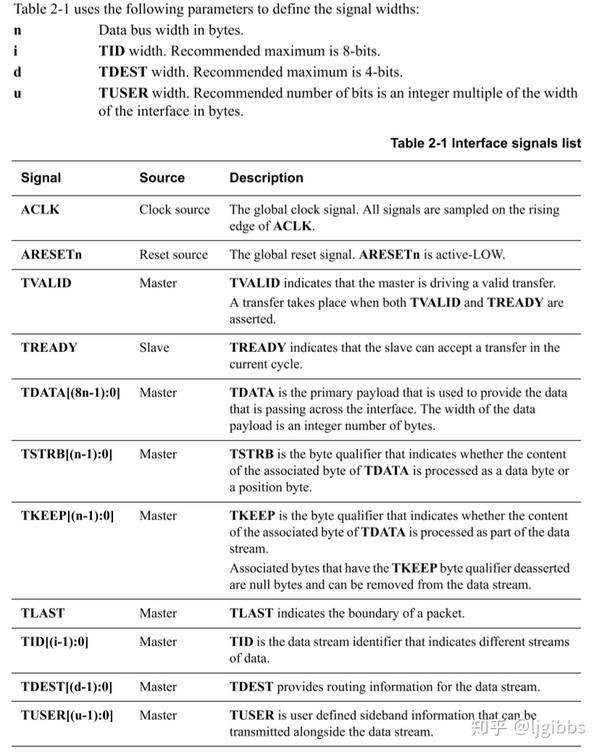

因为没有了地址控制信息的概念,自然也没有了地址控制通道,Stream 的信号包括:

很多信号的概念同 AXI4 完全相同或者大同小异,比如 tlast 表示一次 packet 的结束,类比 r/wlast 信号表示一次 burst 结束。值得注意的是 tstrb 信号不再表示字节是否有效,而是用于标识比特的类型,同 tkeep 配合。tkeep 信号主要用于标识数据字节是否有效。

Stream 协议的读写通道也是单向的,但信号是完全一致的,Stream 协议中不再存在读写通道的区别,也不再有独立的写回复通道。

结束语

本文主要从概念上介绍了下,AXI4 标准协议的两位兄弟,比较“湿”,干活不多。在后续的文章中,我们将结合实例进一步介绍,尤其是同 AXI4 有所不同的 AXI4-Stream 协议,在目前的 FPGA 开发中,Stream 协议和总线的使用非常广泛。

更多AMBA协议相关文章请关注极术专栏Arm AMBA 协议集

| 文件名 | 大小 | 下载次数 | 操作 |

|---|---|---|---|

| hello_axi.pdf | 2.15MB | 128 | 下载 |

| IHI0022E_amba_axi_and_ace_protocol_spec.pdf | 1.92MB | 497 | 下载 |